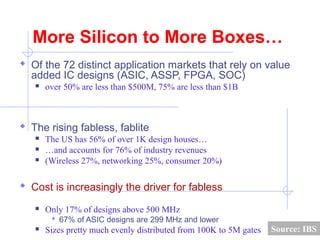

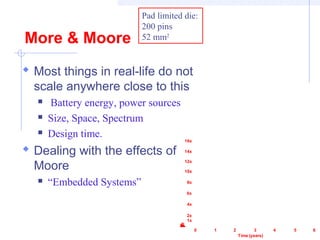

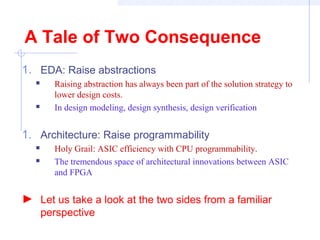

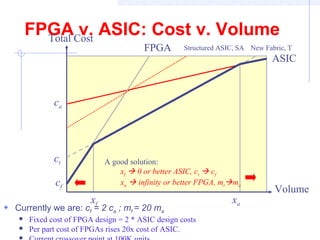

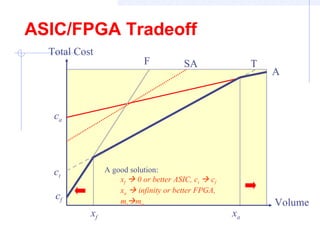

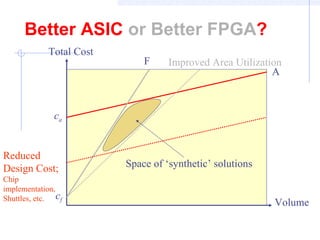

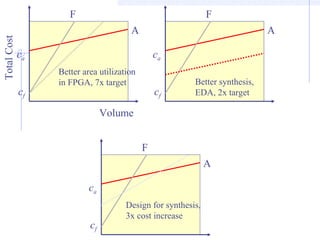

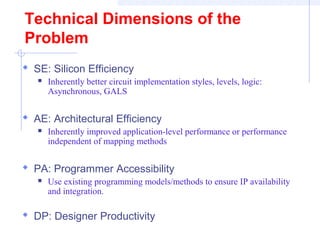

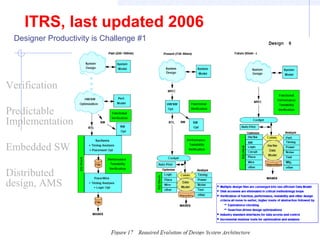

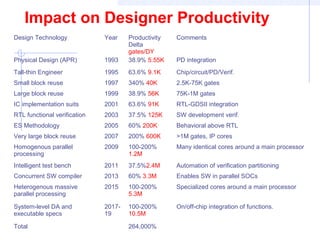

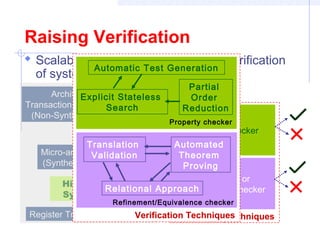

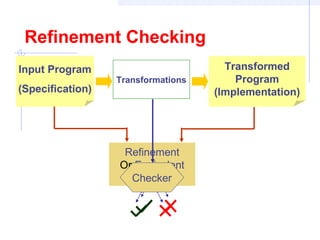

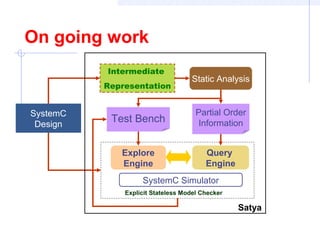

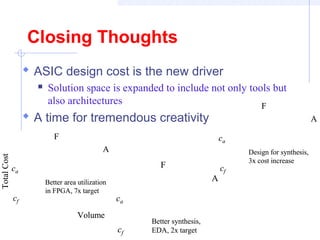

Rajesh Gupta argues that design cost is increasingly driving innovation in system-level integrated circuit designs. Future innovations will focus on tools, methods, architectures, and programming models to lower design costs. Verification techniques that improve designer productivity, such as refinement checking and explicit stateless model checking, will be important to address rising complexity. The solution space includes both improving EDA tools and developing new architectures.