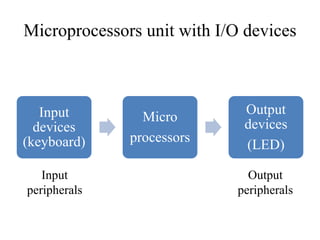

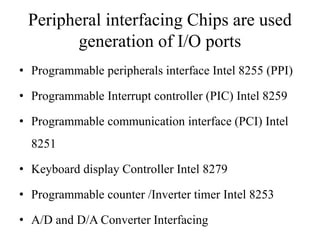

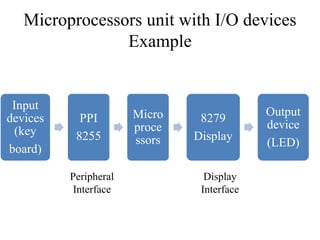

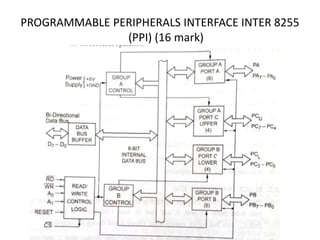

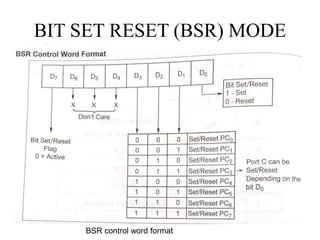

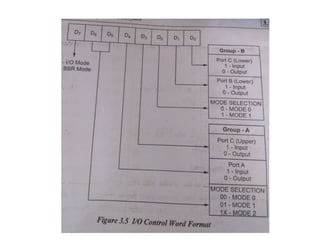

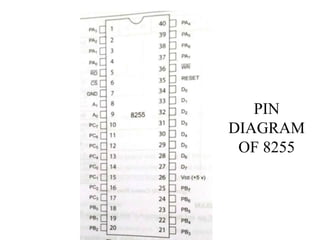

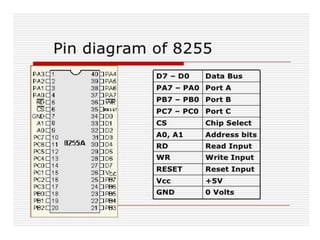

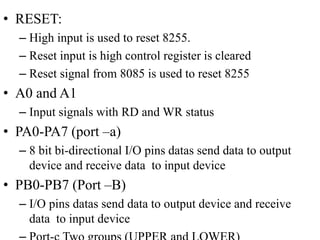

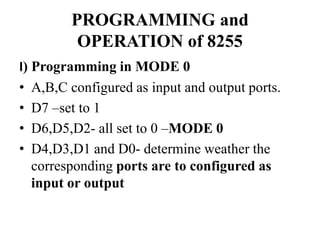

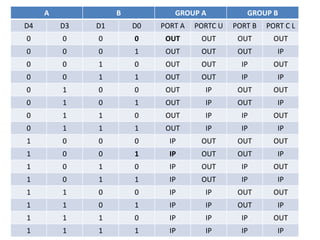

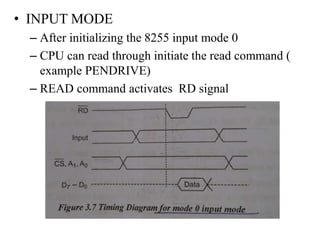

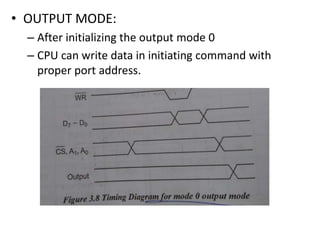

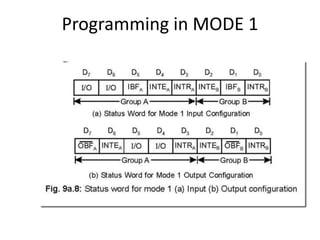

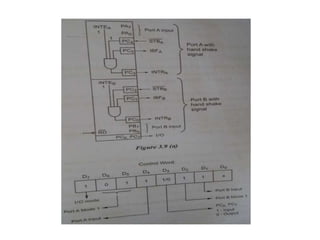

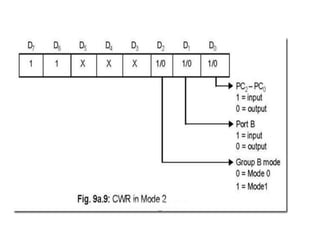

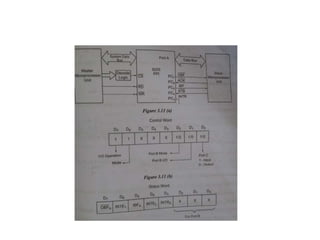

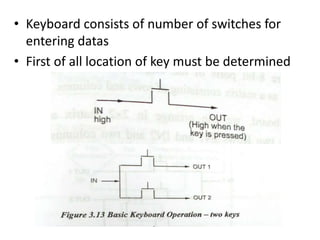

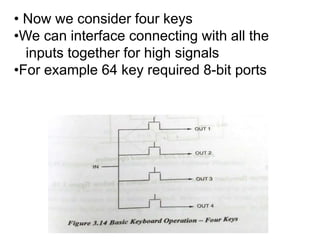

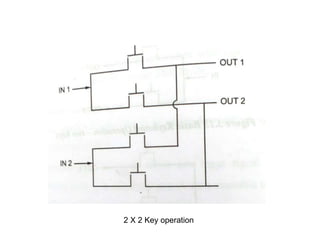

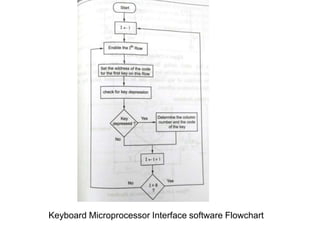

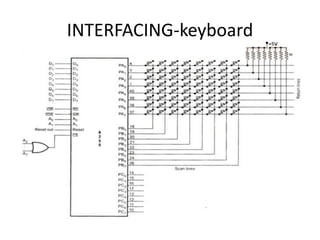

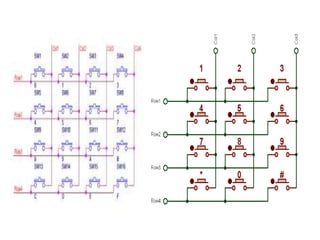

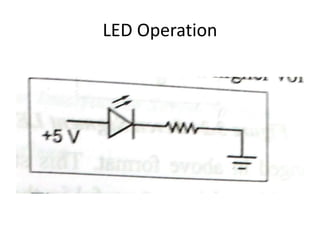

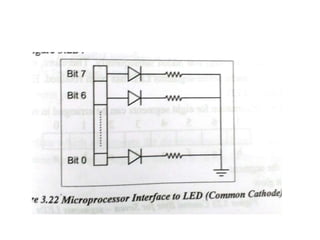

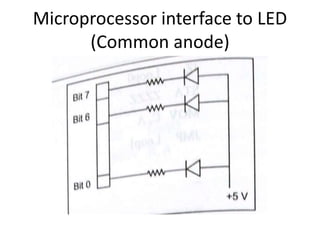

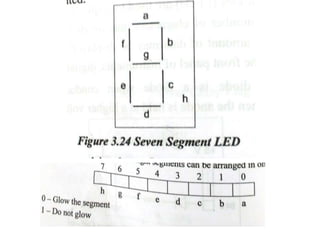

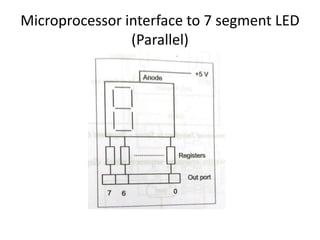

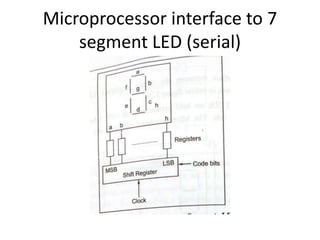

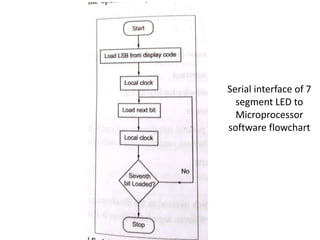

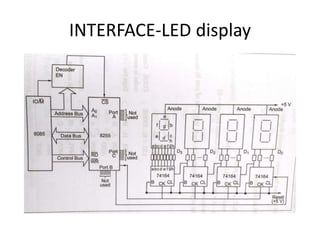

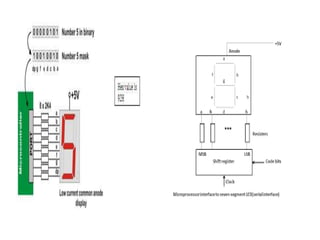

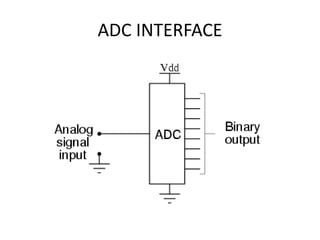

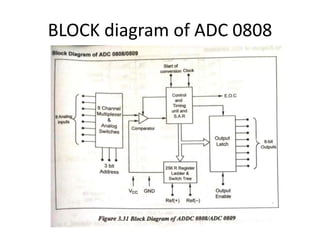

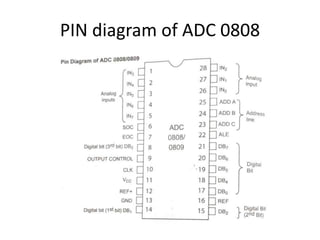

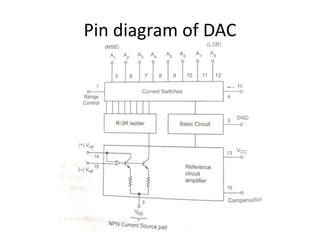

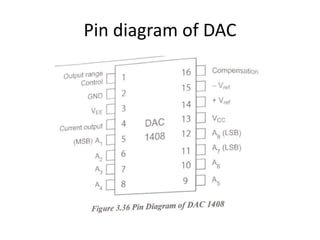

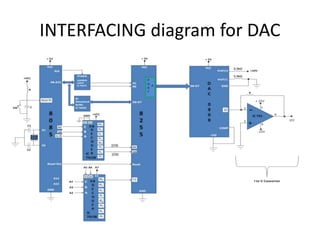

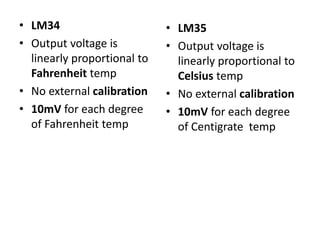

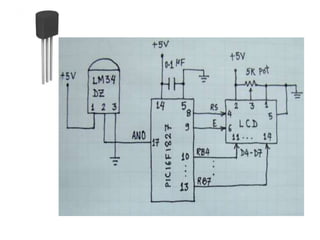

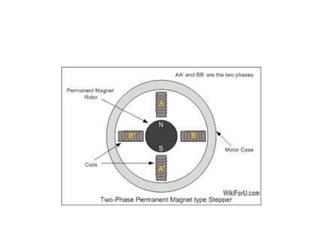

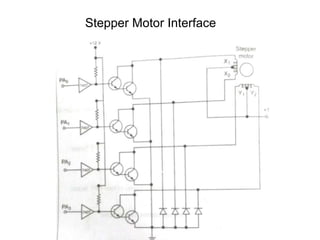

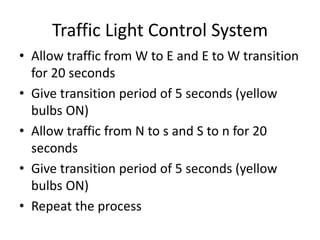

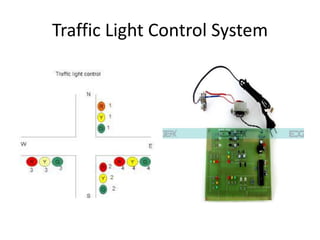

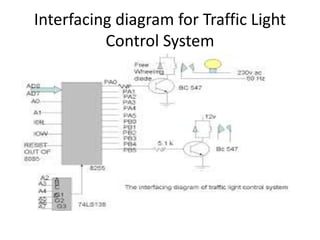

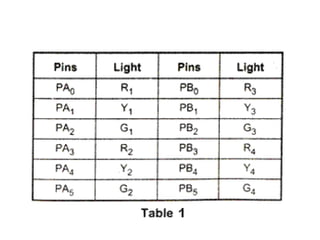

The document discusses various programmable peripheral interface chips used for input/output interfacing in microprocessor systems. It describes the architecture and operating modes of the 8255 Programmable Peripheral Interface chip, which has three 8-bit I/O ports that can be programmed for applications like keyboard interfacing, LED displays, analog-to-digital conversion, digital-to-analog conversion, temperature control, stepper motor control, and traffic light control systems. Circuit diagrams and software flowcharts are provided for different interfacing applications using the 8255 PPI chip.