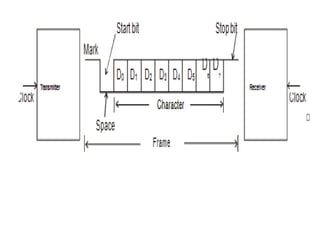

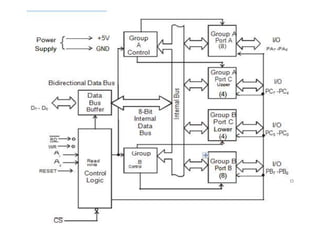

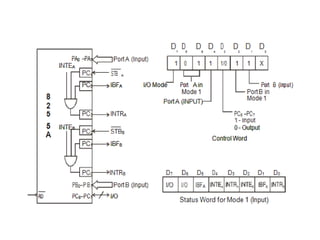

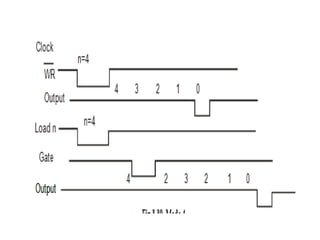

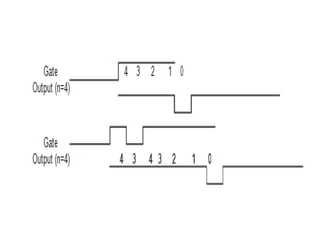

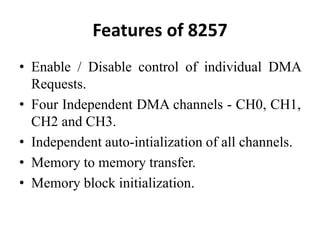

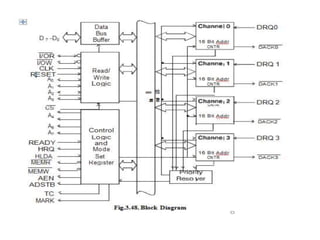

This document provides information on peripheral interfacing in microprocessors. It discusses memory interfacing and I/O interfacing, and some of the peripheral devices developed by Intel like the 8255 parallel communication interface, 8251 serial communication interface, 8254 programmable timer, and 8257 DMA controller. It then describes serial and parallel communication interfaces. It provides details on the 8255 programmable peripheral interface and its operating modes. Finally, it discusses digital to analog converters, applications of the 8254 timer/counter, and analog to digital converters.