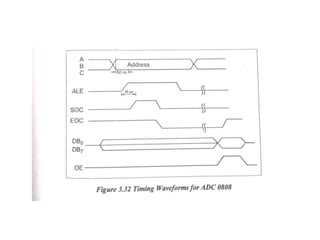

This document discusses the programmable peripheral interface 8255 and its applications. It describes the architecture and operating modes of the 8255 including bit set reset mode and I/O modes 0, 1, and 2. It provides examples of interfacing the 8255 to keyboards, LED displays, analog to digital converters, digital to analog converters, temperature sensors, stepper motors, and traffic light systems. Diagrams and flowcharts illustrate the interfacing between these peripheral devices and a microprocessor using the 8255.