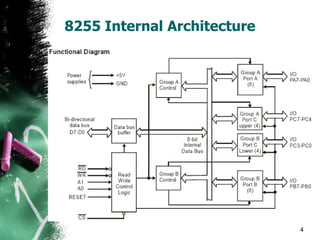

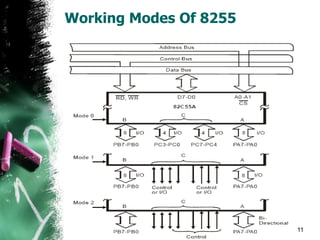

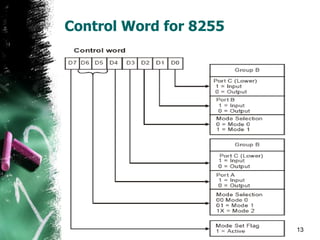

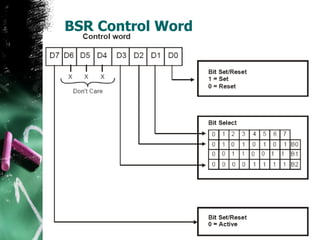

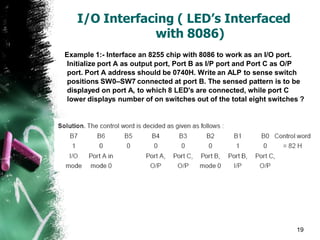

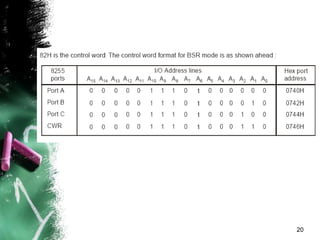

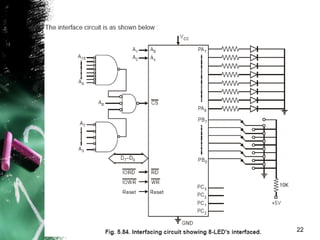

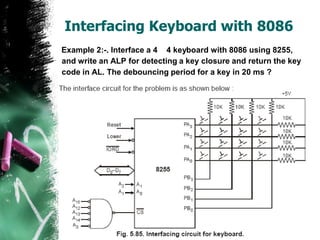

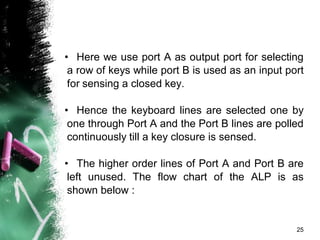

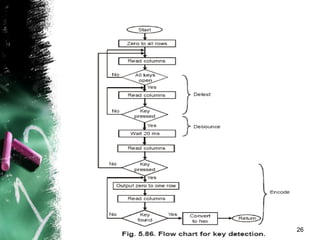

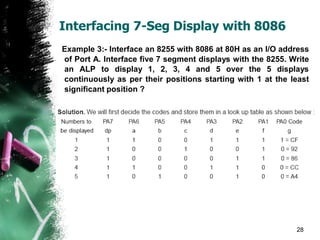

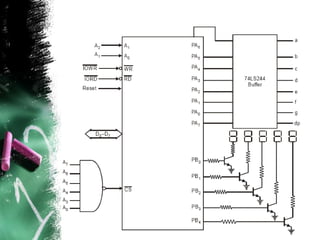

This document discusses interfacing the 8255 Programmable Peripheral Interface chip with the 8086 microprocessor. It describes the internal architecture of the 8255 including its data bus buffer, control logic, port select pins, and control pins. It then explains the different operating modes of the 8255 including basic I/O, strobed I/O, and bidirectional bus modes. Examples are provided of interfacing LEDs, a keyboard, and 7-segment displays with the 8086 using the 8255 to control I/O operations.