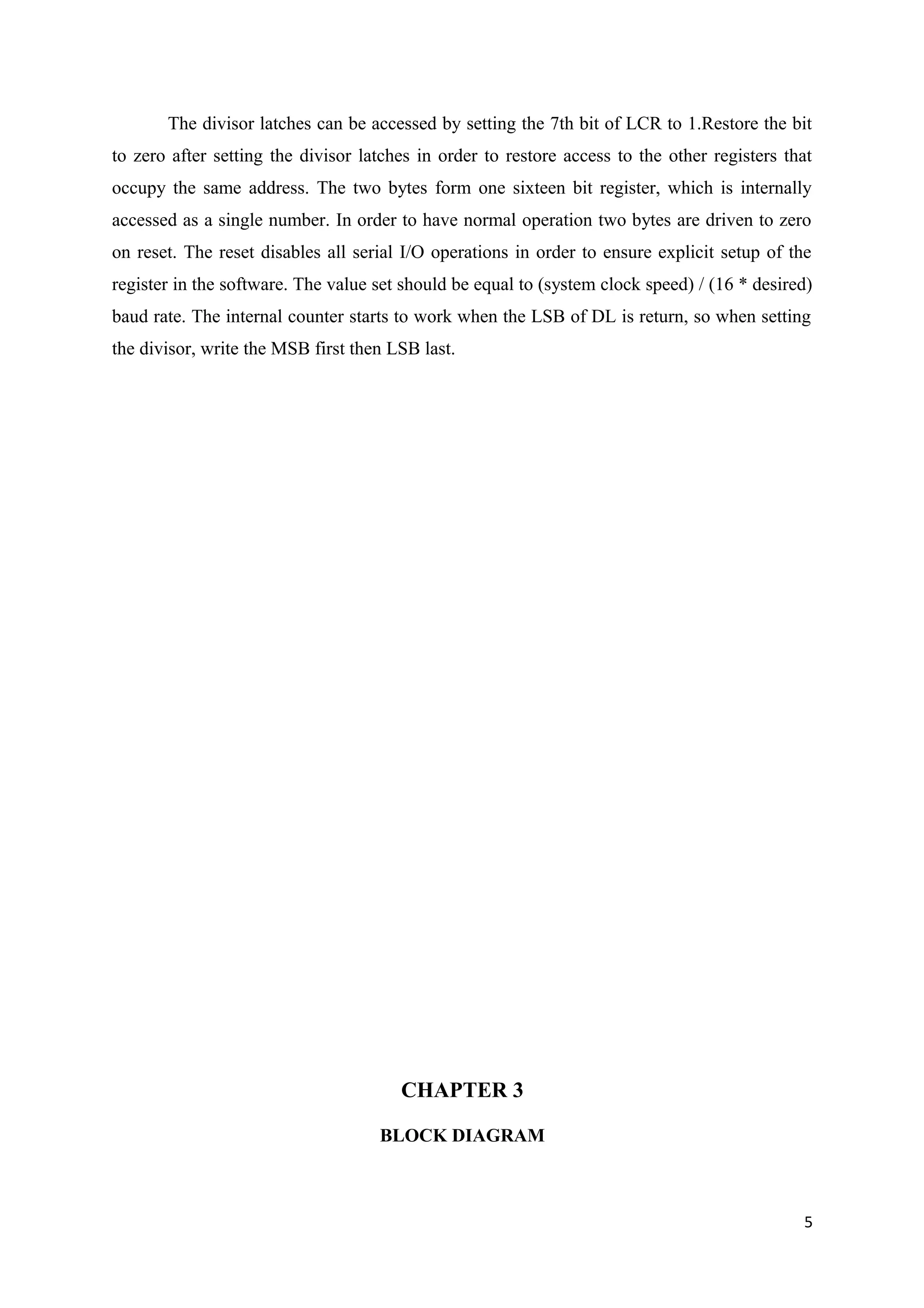

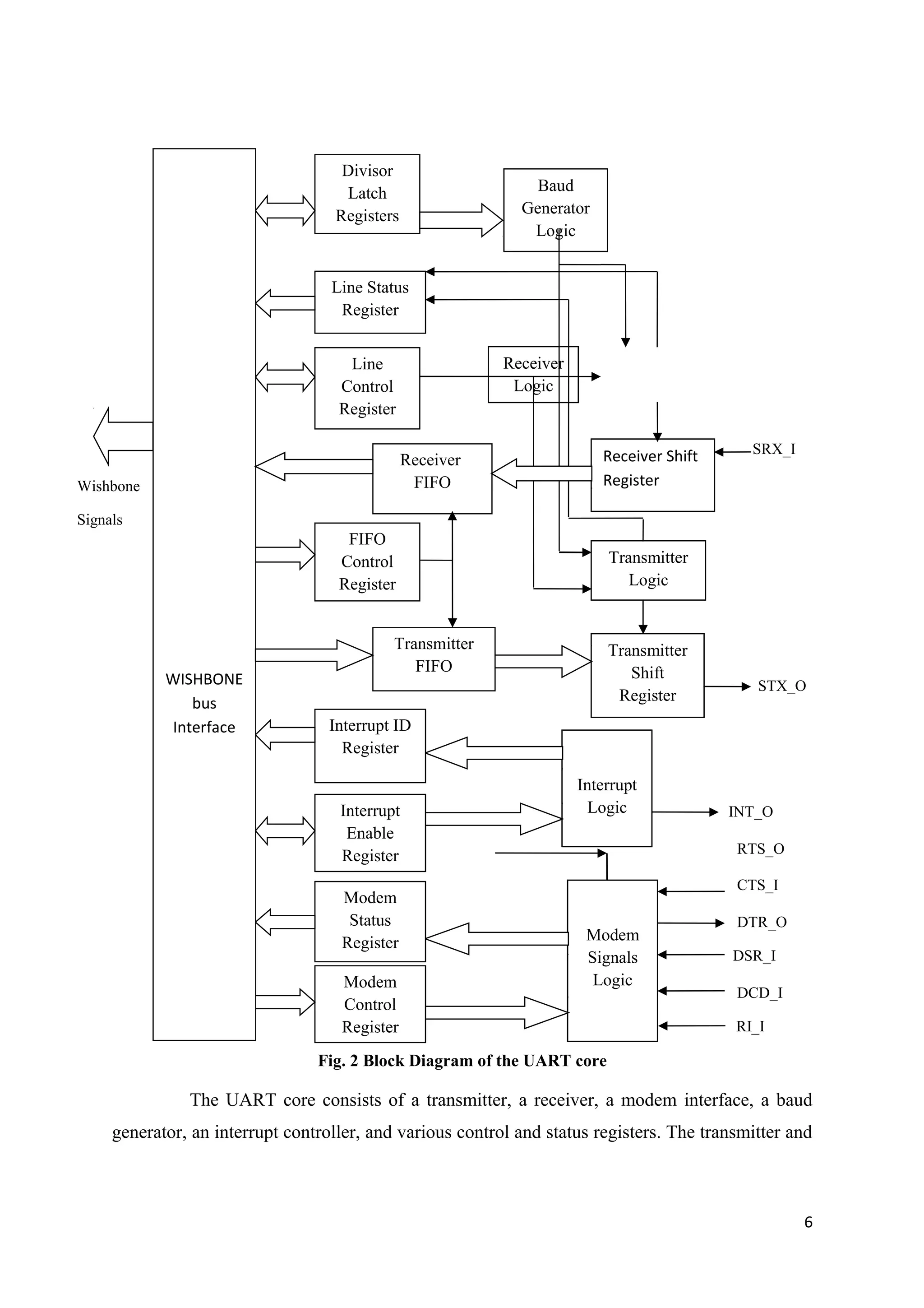

The document describes a UART verification IP core. It consists of a transmitter, receiver, modem interface, baud generator, interrupt controller and control/status registers. The core performs serial-to-parallel and parallel-to-serial conversions. It can operate in 8-bit or 32-bit data bus mode and interfaces with a wishbone bus. The document outlines the UART packet structure, registers, modes of operation, block diagram, UVM verification architecture including transactions, agents, drivers, monitors, sequences, tests and scoreboard. It concludes by summarizing that the UART core was verified for different modes and test cases.