This document discusses BICMOS technology. It begins by justifying the need for transistors and explaining the progression from vacuum tubes to BJT to FET to BICMOS. BICMOS combines bipolar and CMOS technologies, allowing designers to use both device types on a single integrated circuit. This provides benefits like high speed, gain, and driving capability from bipolar devices, along with low power and high density from CMOS. Key uses of BICMOS include high-performance microprocessors and mixed-signal circuit design. The document covers basic BICMOS circuitry and switching behavior, as well as applications like input/output and sample and hold circuits.

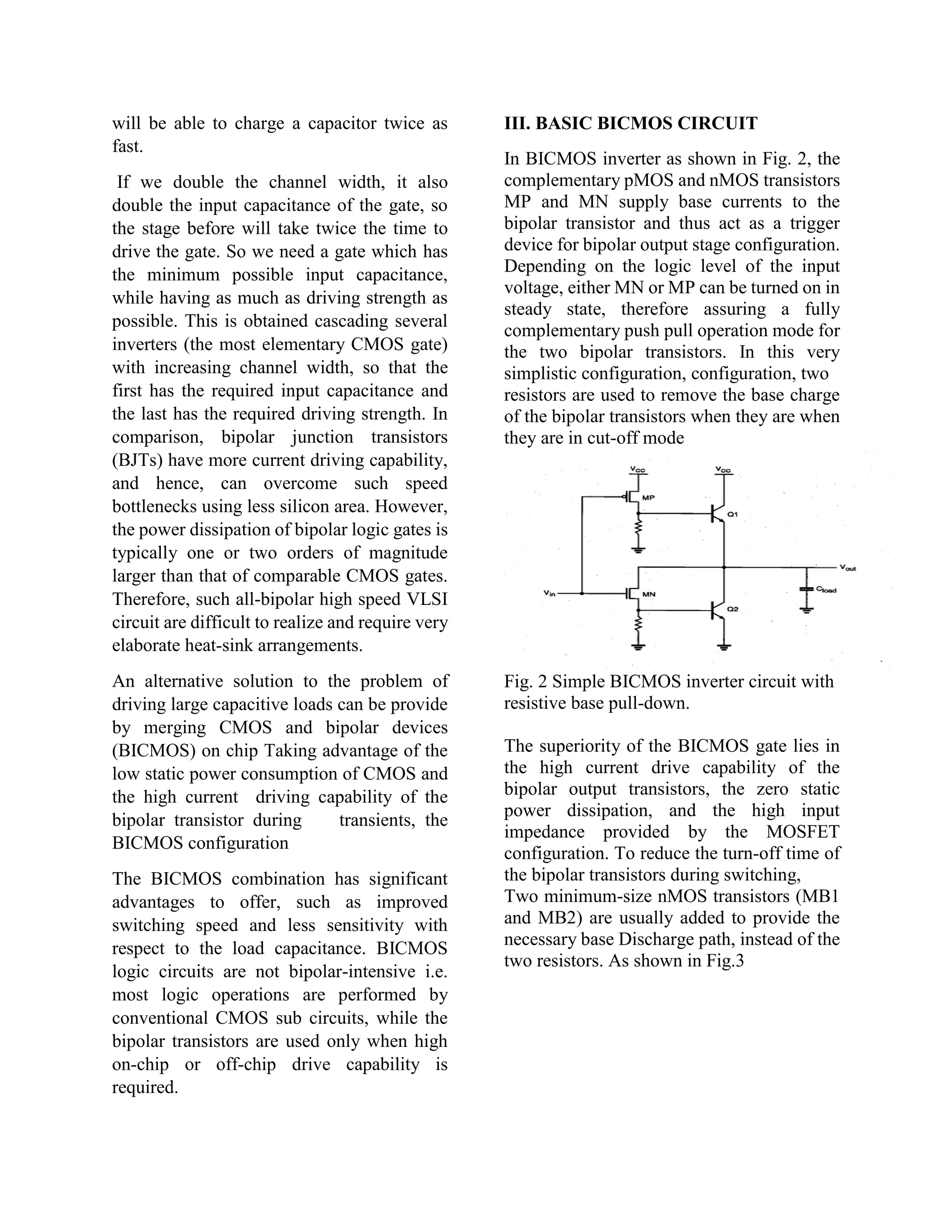

![As the input voltage rises, the pMOS

transistor MP is turned off and the nMOS

Transistors MN and MB 1 are turned on. The

bipolar pull-up transistor Q1 immediately

ceases to conduct because its base current

drops to zero, and MB 1 starts to remove the

excess minority carrier base charge of Q1.

The nMOS transistor MN operates initially in

the saturation region and supplies the base

current of the bipolar pull-down transistor

Q2.

IV. USES OF BICMOS TECHNOLOGY

There have been two significant uses of

BICMOS technology.

One of the usages is in the design of the high-

performance microprocessor unit (MPU)

using the high driving capability of bipolar

junction transistor because bipolar junction

transistor has better transconductance.

Comparing the gate delay time and load

capacitance capability for same area design,

BICMOS has a lower gate delay time than the

CMOS at high load capacitive environment

as illustrated in Fig 6.

Fig. 6 CMOS vs BICMOS

And second one is in the mixed signal circuit

design, BICMOS design utilizes the excellent

analog performance of the double poly self-

aligned bipolar junction transistor

V. BICMOS APPLICATION

1. In some applications (in which there is

finite budget for power) the BICMOS speed

performance is better than that of bipolar.

2. This technology is well suited for the

intensive input/output applications.

3. The applications of BICMOS were initially

in RISC microprocessors rather than

traditional CISC microprocessors.

4. It can be used for sample and hold

applications as it provides high impedance

inputs.

5. This is also used in applications such as

adders, mixers, ADC and DAC

VI. CONCLUSION

The most significant drawback of the

BICMOS circuits lies in the increased

fabrication process complexity more than

that of CMOS. Apart from this it can be used

as an alternate of the previous bipolar, ECL

and CMOS in the market.

VII. REFERENCE

[1] http://www.nobelprize.org

[2] http://blog.oscarliang.net/bjt-vs-mosfet

[3] http:// www.elprocus.com

[4] Digital Integrated Circuits, 2/E Jan M.

Rabaey, University of California, Berkeley

Anantha Chandrakasan, Massachusetts

Institute of Technology, Cambridge Borivoje

Nikolic, University of California, Berkeley.

[5] CMOS Digital integrated Circuits Sung-

Mo-Kang & Yusuf Leblebici 3rd 2003 Tata

McGraw Hill](https://image.slidesharecdn.com/modifiedbicmos-150117070853-conversion-gate01/75/Modified-bicmos-4-2048.jpg)