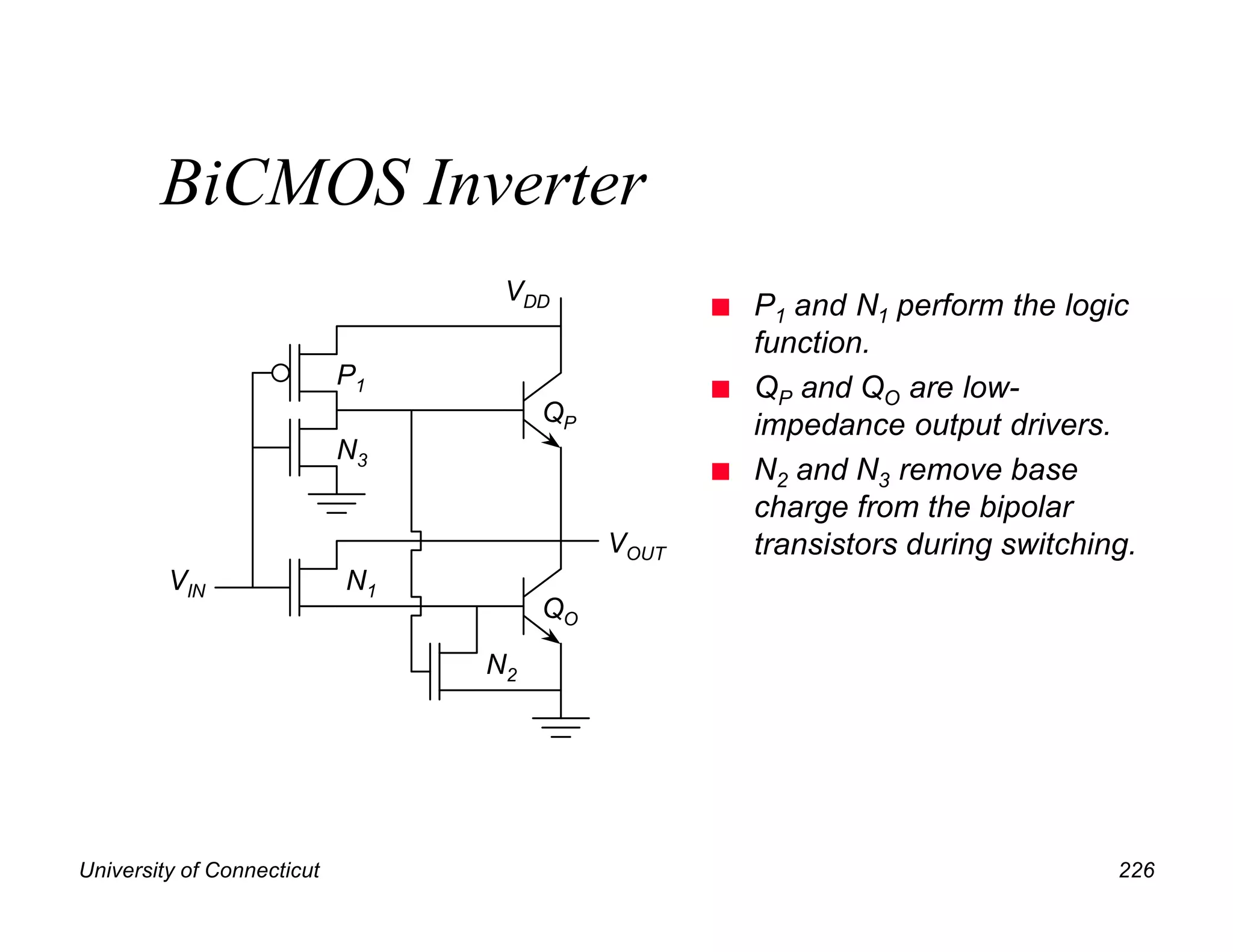

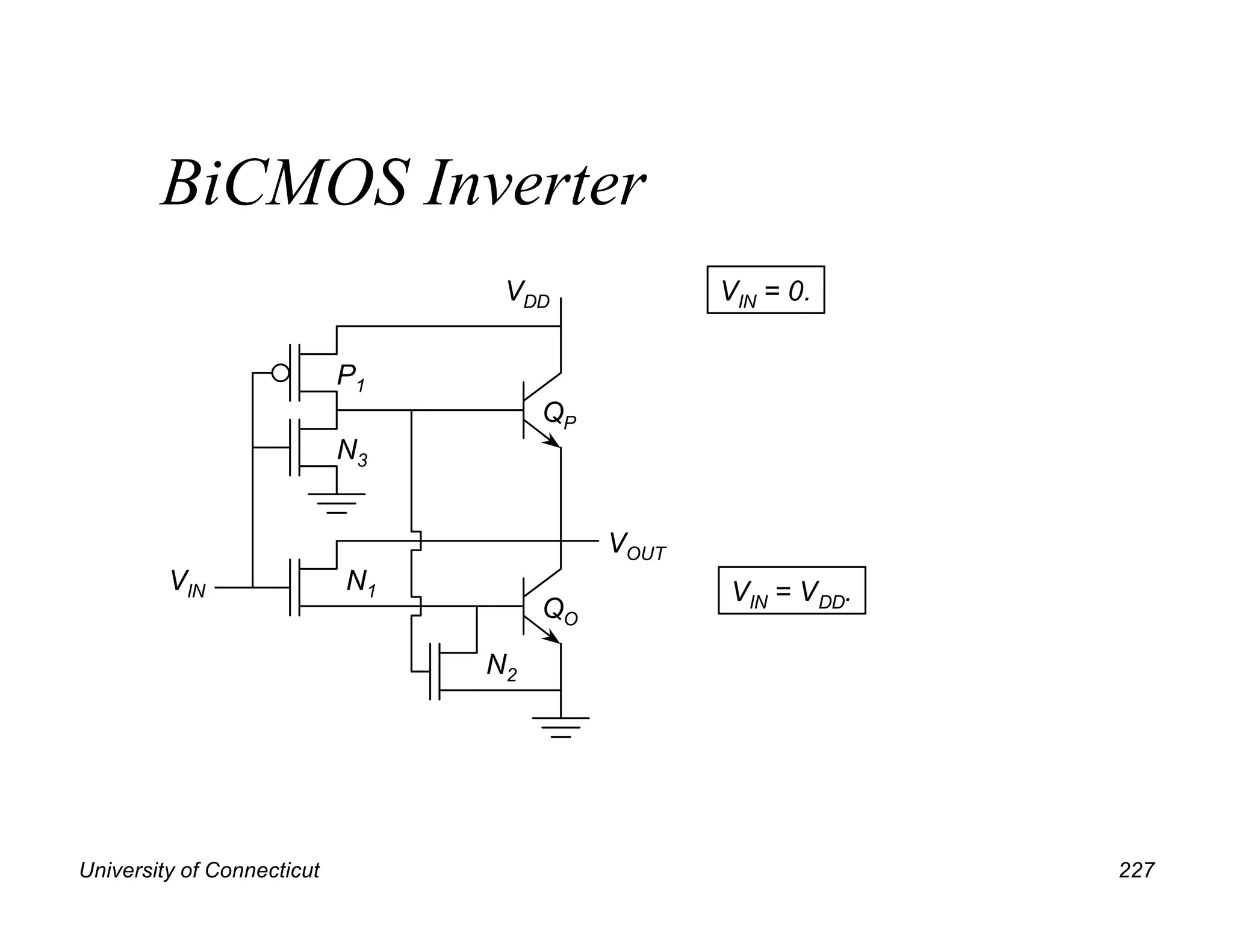

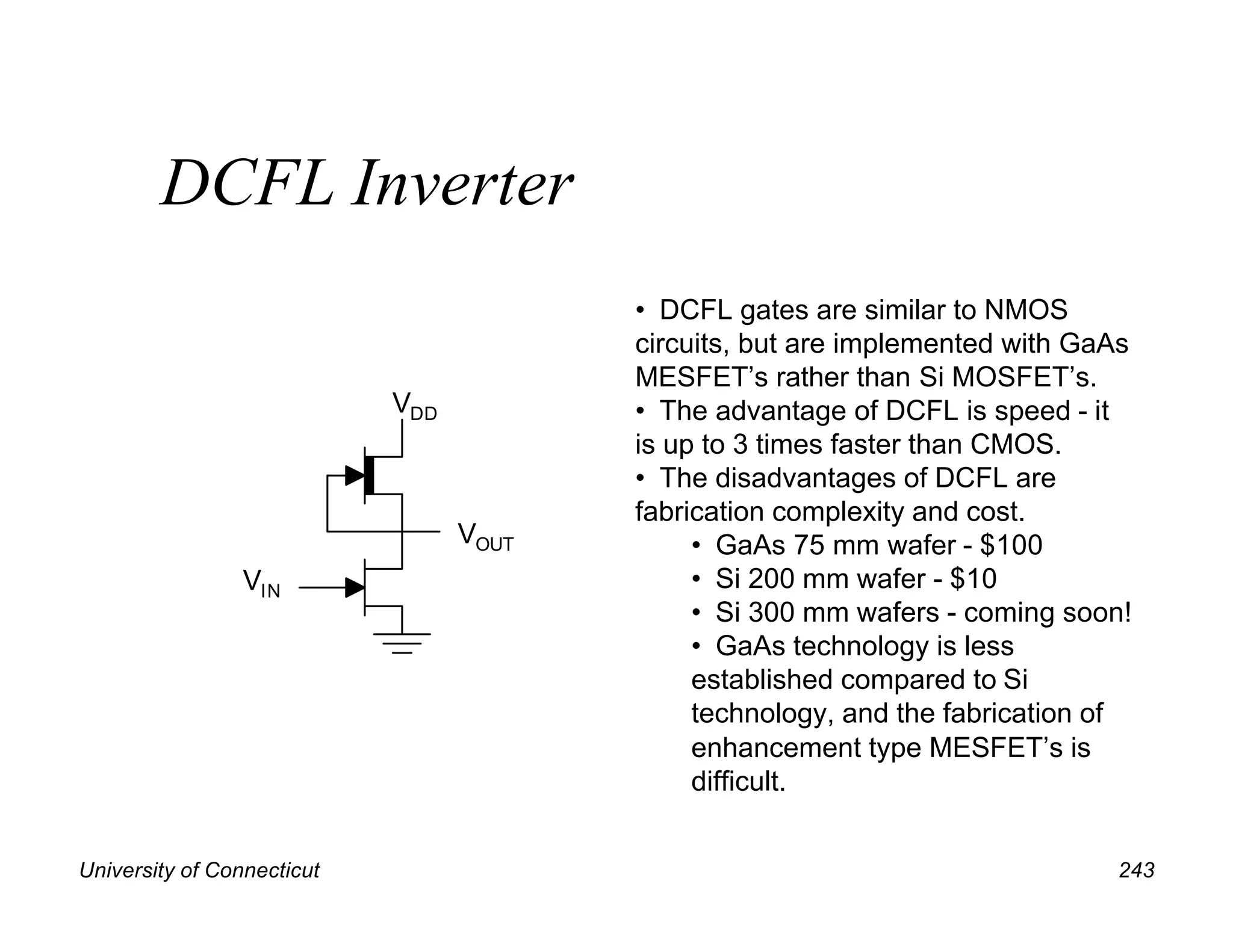

This document discusses BiCMOS and DCFL logic circuitry as alternatives to traditional CMOS. It provides details on the operation and advantages/disadvantages of BiCMOS inverters, NAND gates, and other circuits. DCFL using gallium arsenide is also examined and compared to CMOS. While BiCMOS and DCFL provide higher speeds, they have higher fabrication complexity and costs compared to CMOS. Examples of applications where the extra speed justifies the costs are mentioned.

![University of Connecticut 248

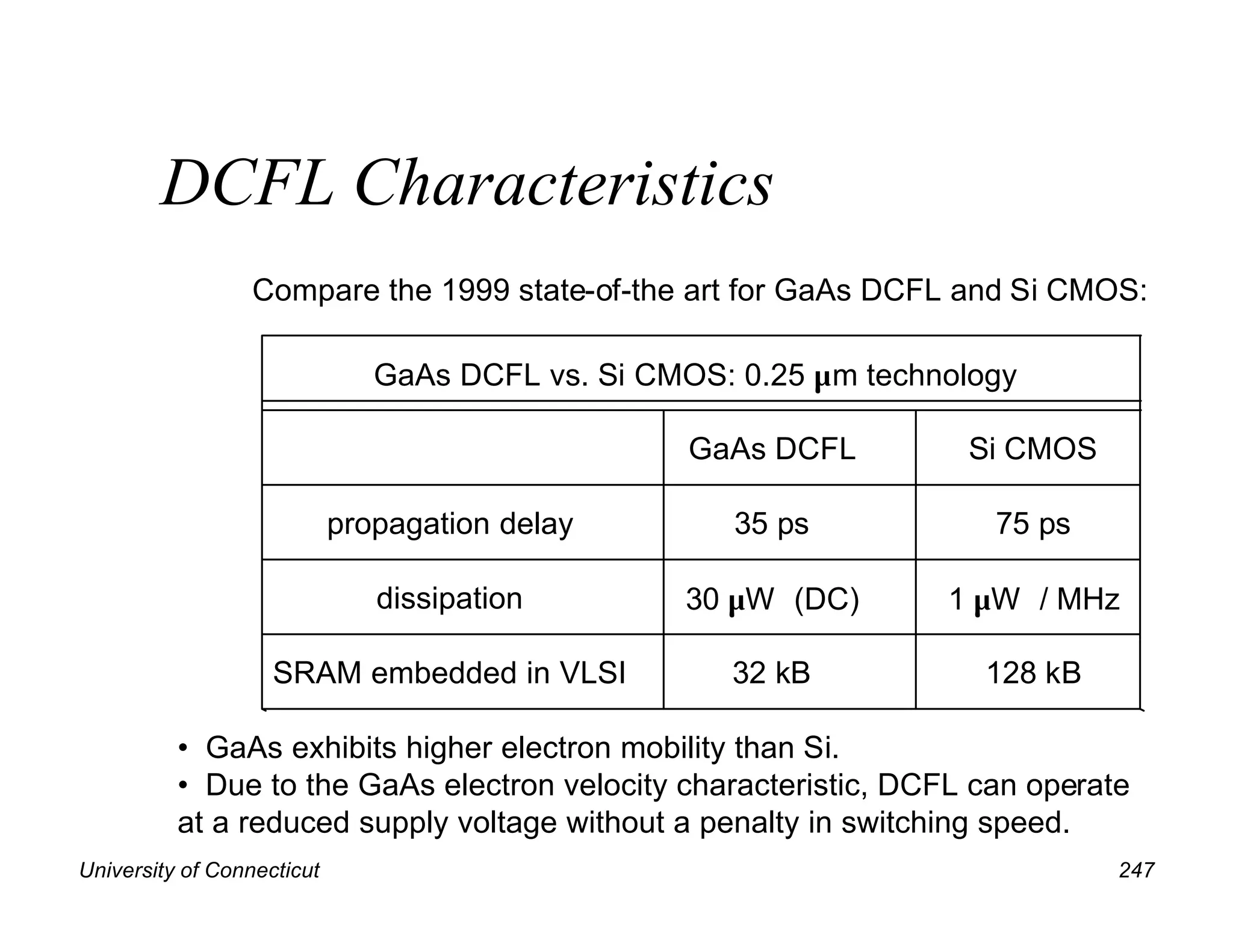

DCFL Applications

n For a given minimum linewidth, GaAs DCFL circuitry is about 2

to 3 times faster than Si CMOS because of the difference in

electron mobilities.

n The extra speed comes at a premium, because GaAs

technology is less developed and DCFL is expensive.

n DCFL applications are at the high end, where the extra cost can

be justified. Examples are the Cray Y-MP and the Vitesse

Semiconductor GaAs microprocessor, which boasts 1.2 M

transistors [see Ira Deyhimy, “Gallium Arsenide Joins the Giants,” IEEE

Spectrum, pp. 33-40, February 1995].

n At the present time, the area of fastest growth for GaAs DCFL is

communications.

n A factor of three isn’t much, though, when you consider the rapid

advancement of Si CMOS / BiCMOS technology.](https://image.slidesharecdn.com/bicoms-210427032303/75/Bicoms-25-2048.jpg)