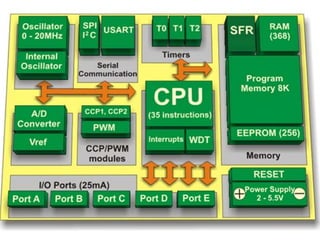

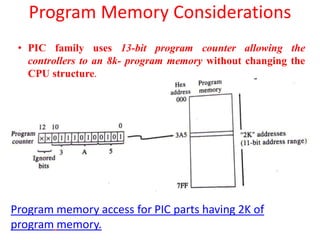

This document provides an introduction to PIC microcontrollers. It discusses the architecture of PIC microcontrollers, including the 16C6x and 16C7x architectures. It describes the registers, memory, and instruction set of PIC microcontrollers. Some key points covered include the Harvard architecture, pipelining, addressing modes, arithmetic, logical, and conditional instructions. Peripherals like timers and interrupts are also mentioned.