This document summarizes the key topics covered in a lecture on digital electronics, including:

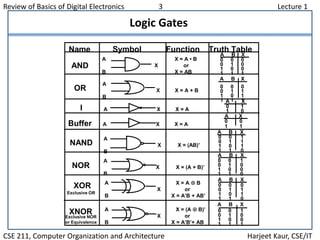

- Common logic gates like AND, OR, NOT and their truth tables.

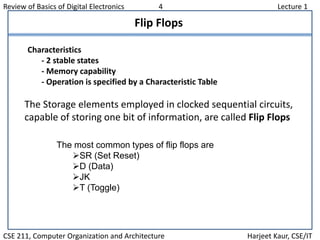

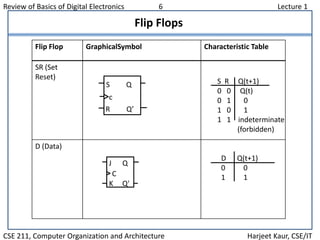

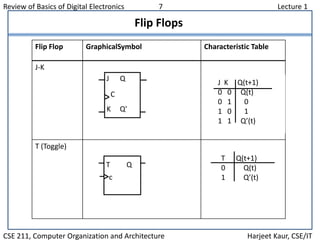

- Flip flops which are used to store digital data and come in types like SR, D, JK.

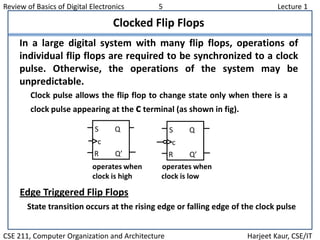

- Clocked flip flops which only change state on the rising/falling edge of a clock pulse for synchronization.

- Other common digital components like registers, counters, multiplexers and decoders.