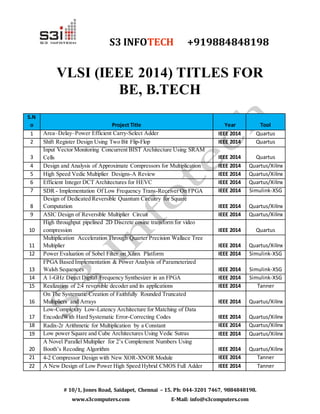

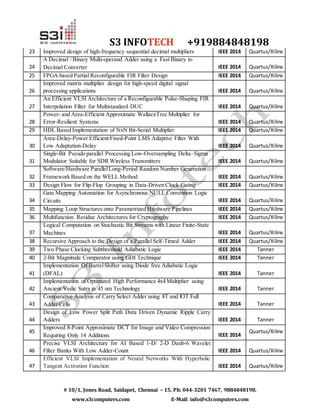

This document contains 50 titles of VLSI projects presented at the IEEE conference in 2014. The projects cover a range of topics related to digital circuit design including adder circuits, multiplier designs, DSP applications, cryptography, and neural networks. Each project listing includes the title, year presented, and design tools used such as Quartus, Xilinx, Tanner, and Simulink.