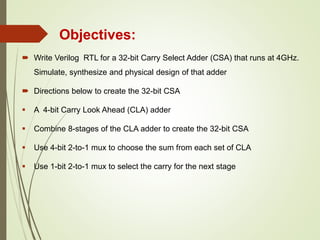

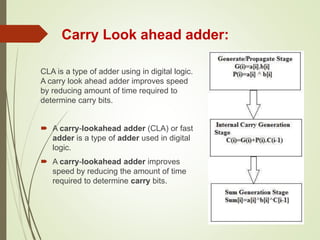

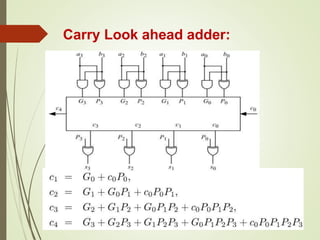

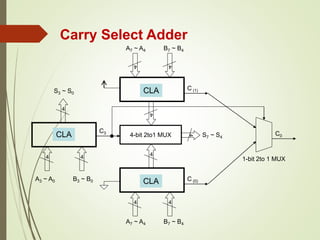

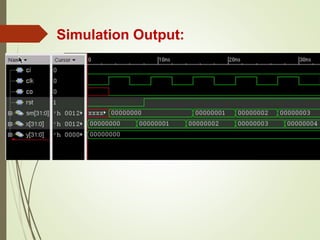

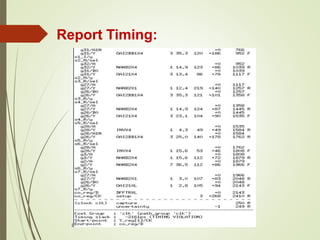

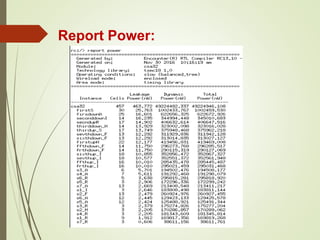

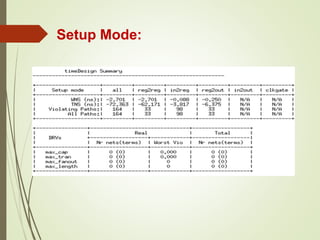

The document outlines a project focused on designing a 32-bit Carry Select Adder (CSA) in Verilog RTL, aimed to operate at 4 GHz. It describes the construction of the CSA using 4-bit Carry Lookahead Adders and multiplexers for efficient carry and sum selection. Additionally, it discusses the simulation, synthesis, and physical design aspects of the adder.