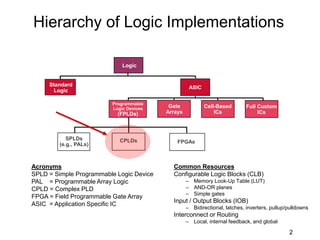

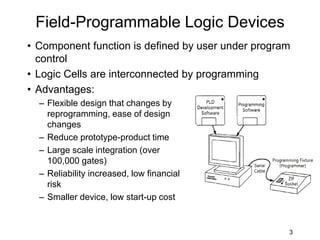

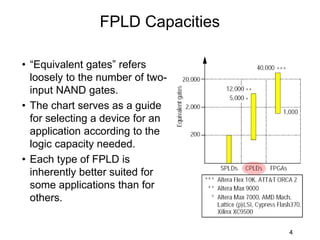

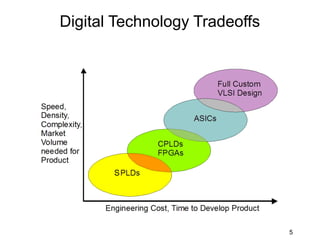

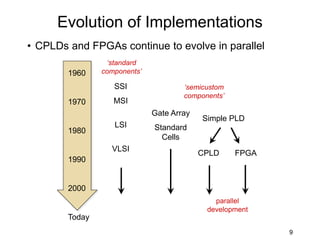

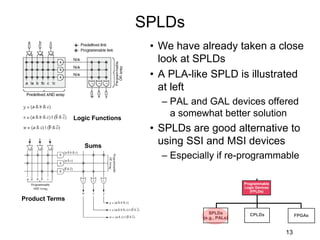

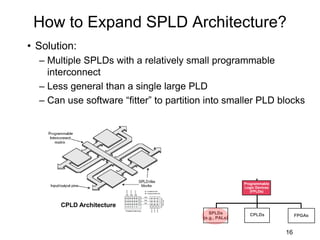

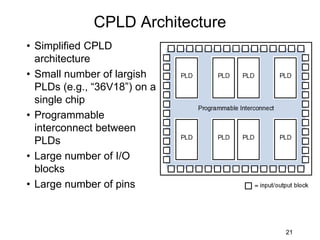

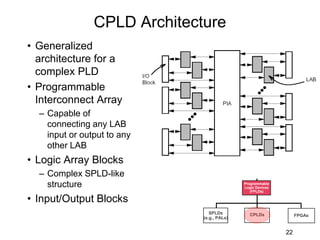

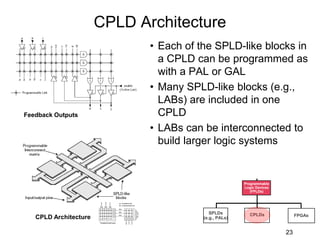

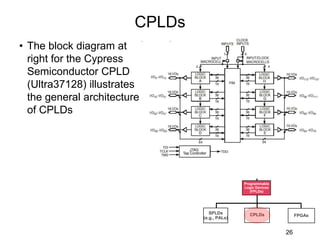

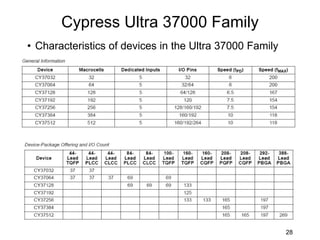

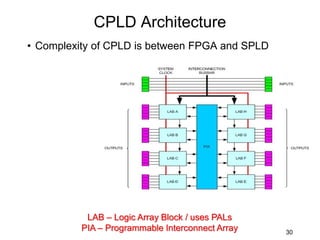

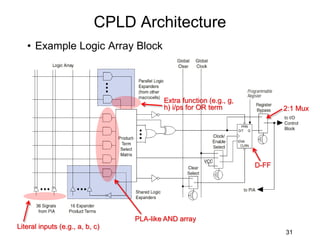

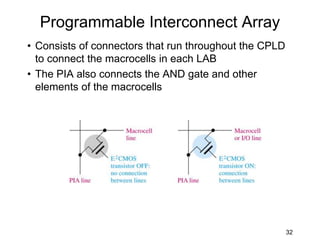

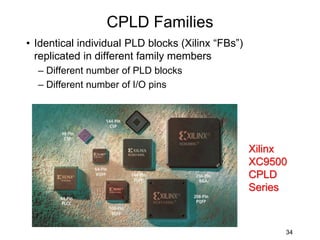

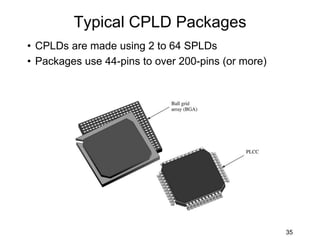

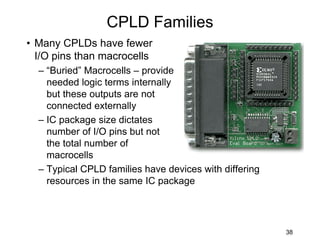

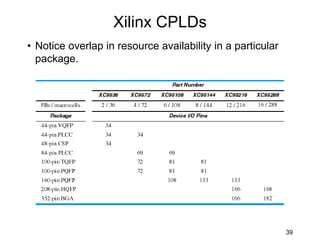

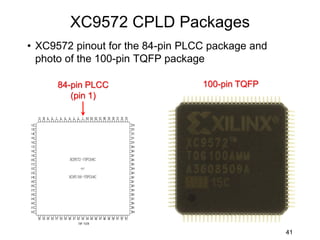

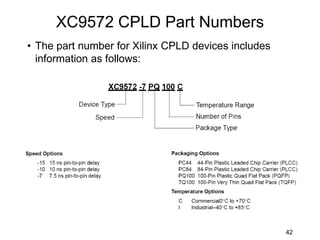

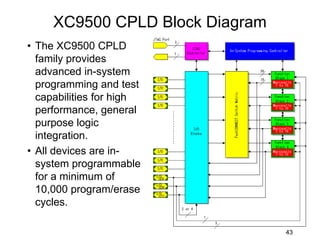

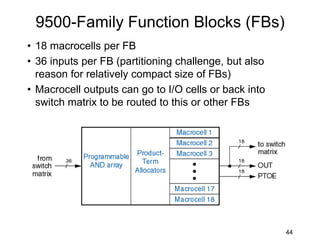

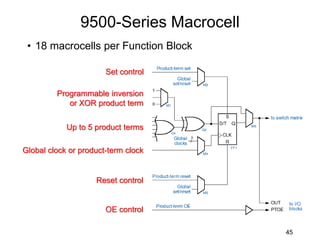

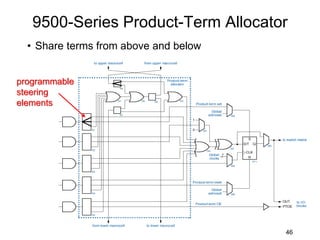

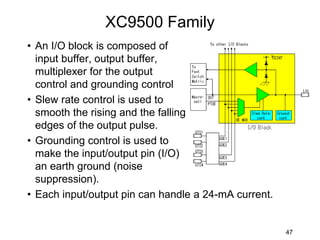

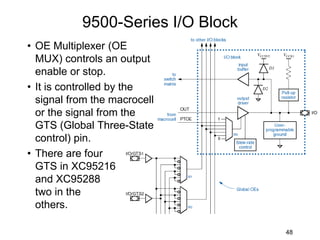

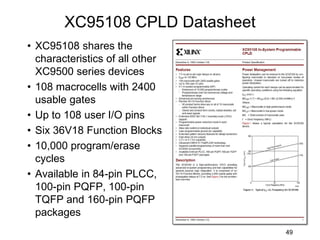

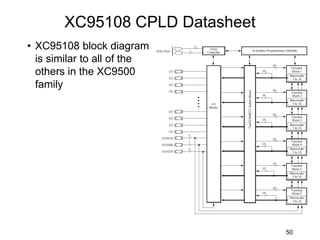

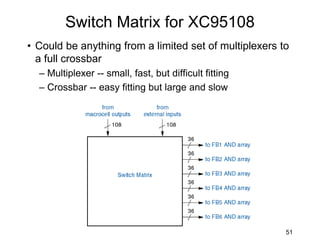

The document provides an overview of field-programmable logic devices (FPLDs) such as complex programmable logic devices (CPLDs) and field-programmable gate arrays (FPGAs). It discusses the history and basic architecture of CPLDs, including logic array blocks (LABs) and programmable interconnect arrays (PIAs). It also covers specific CPLD families and devices from vendors like Xilinx and Altera.