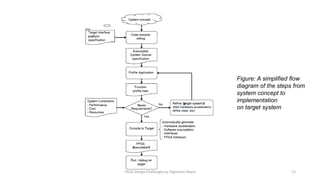

The document discusses the complexities and challenges associated with FPGA design, including prolonged design cycles, system design complexity, and debugging difficulties. It offers strategies to address these challenges, such as selecting appropriate prototyping systems and managing design size and power consumption. Additionally, it emphasizes the importance of reliability, reusability, and remote management in FPGA-based design and prototyping.