Final poster

•Download as PPTX, PDF•

0 likes•28 views

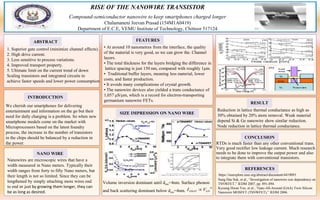

The document discusses the rise of the nanowire transistor for use in smartphones. Nanowires are microscopic wires with widths measured in nanometers that can improve transistor performance by allowing for superior gate control, high drive current, reduced sensitivity to process variations, and improved transport properties. This helps push the limits of transistor downscaling for faster speeds and lower power consumption. The document also notes specific benefits of nanowires such as reduced lattice thermal conductance and faster switching speeds compared to conventional transistors.

Report

Share

Report

Share

Recommended

Junctionless Transistor

in this performance estimation of Junctionless Transistor and its application is explained

Analysis of analog and RF behaviors in junctionless double gate vertical MOSFET

The prime obstacle in continuing the transistor’s scaling is to maintain ultra-shallow source/drain (S/D) junctions with high doping concentration gradient, which definitely demands an advanced and complicated S/D and channel engineering. Junctionless transistor configuration has been found to be an alternative device structure in which the junction and doping gradients could be totally eliminated, thus simplifying the fabrication process. In this paper, a process simulation has been performed to study the impact of junctionless configuration on the analog and RF behaviors of double-gate vertical MOSFET. The result proves that the performance of n-channel junctionless double-gate vertical MOSFET (n-JLDGVM) is slightly better than the junction double-gate vertical MOSFET (n-JDGVM). Junctionless device exhibits better analog behaviors as the transconductance (gm) is increased by approximately 4%. In term of RF behaviors, the junctionless device exhibits 3.4% and 7% higher cut-off frequency (fT) and gain band-width product (GBW) respectively over the junction device.

MS Thesis Defense Presentation

Particle Separation and Chemical Gradient Control

via

Focused Travelling Surface Acoustic Waves (F-TSAW)

PARTICLE SEPARATION, CHEMICAL GRADIENT CONTROL AND MICROMIXING VIA FOCUSED TR...

Presented our work at MicroTAS2013 in Freiburg, Germany

Recommended

Junctionless Transistor

in this performance estimation of Junctionless Transistor and its application is explained

Analysis of analog and RF behaviors in junctionless double gate vertical MOSFET

The prime obstacle in continuing the transistor’s scaling is to maintain ultra-shallow source/drain (S/D) junctions with high doping concentration gradient, which definitely demands an advanced and complicated S/D and channel engineering. Junctionless transistor configuration has been found to be an alternative device structure in which the junction and doping gradients could be totally eliminated, thus simplifying the fabrication process. In this paper, a process simulation has been performed to study the impact of junctionless configuration on the analog and RF behaviors of double-gate vertical MOSFET. The result proves that the performance of n-channel junctionless double-gate vertical MOSFET (n-JLDGVM) is slightly better than the junction double-gate vertical MOSFET (n-JDGVM). Junctionless device exhibits better analog behaviors as the transconductance (gm) is increased by approximately 4%. In term of RF behaviors, the junctionless device exhibits 3.4% and 7% higher cut-off frequency (fT) and gain band-width product (GBW) respectively over the junction device.

MS Thesis Defense Presentation

Particle Separation and Chemical Gradient Control

via

Focused Travelling Surface Acoustic Waves (F-TSAW)

PARTICLE SEPARATION, CHEMICAL GRADIENT CONTROL AND MICROMIXING VIA FOCUSED TR...

Presented our work at MicroTAS2013 in Freiburg, Germany

3D or Tri-gate transistors

3D or Tri-gate transistors are multigate transistors having gate wrapped on three sides of conducting channel of electrons.

SEBA KMT MFM5 1 Cable Sheath Testing, Fault Prelocation & Pinpointing

SEBA KMT MFM5-1 is the universal test instrument for cable sheath testing including prelocation and pinpointing of cable sheath faults - in sheath testing mode SEBA KMT MFM5-1 can detect minute cable sheath insulation damage on low and high voltage cable networks.

SEBA KMT MFM5-1 ensures fast and precise cable sheath fault location - the instrument is menu-driven and fully automatic sheath fault prelocation is accurately achieved by inputting total cable length. SEBA KMT ESG 80-2 can be combined with the MFM5-1 for earth fault location in LV-HV cables.

Cable Sheath Test & Fault Location SEBA KMT MFM5-1 Features : Sheath testing, fault prelocation and pinpointing combined in single unit, sheath testing up to 5kV, time saving prelocation of sheath fault.

Parallel wire Technique in CTO PCI

Use of Parallel wire technique to enhance procedural success in CTO PCI

Introduction to FinFET

For more information regarding the "Construction of finFET" you can contact through mail (manishkenchi111296@gmail.com)

eDRAM Cells using FinFET Technology

FinFET is nothing but a MOSFET whose body is a thin piece of silicon with gate wrapped around it.

22nm tri-gate technology

this presentation giver the outline of use of trigate technology in 22 nm technology and its manufacture

Visi fault™ visual fault locator

Visi fault™ visual fault locator. Industrial-strength fiber tracing, verification and fault location tool.

Bright red visible laser light source

• Accelerates end-to-end fiber

continuity checks

• Speeds fiber tracing and identification

• Simplifies fiber polarity verification

• Aids in location of fiber faults including

tight bends, breaks and bad connectors

Cutoff wavelength in optical fibre

Cutoff wavelength optical fibre is presentation of principal of cutoff wavelength of cabled and uncabled fibre, measurment description , measurment procedures and index of refraction explained

Cable Sniffer LV Cable Fault Locator - Operating Manual

Cable Sniffer LV Cable Fault Locator - Operating Manual

Please read the following IEEE Spectrum articles and answer the quest.pdf

Please read the following IEEE Spectrum articles and answer the questions given. You may

want to use illustrations in your answer to the questions, and mark them up accordingly as part of

answering the questions. If you take illustrations from some source (including the IEEE

Spectrum articles) please make sure this is properly cited.

http://spectrum.ieee.org/semiconductors/nanotechnology/the-next-highperformance-transistor-

could-be-made-from-lateral-nanowires Describe a FINFET and how it works. How is it different

than the planar MOSFET described in the first 5 slides of the TFET lecture? Is the FINFET a

quantum device? Give reasons why or why not. How is the nanowire device described here

different than the FINFET? Why is this difference an advantage for the nanowire device? They

one problem with the nanowire device is capacitive coupling. What is this and explain why it is a

problem with the nanowire device?

Solution

1)

The FinFET technology promises to provide the deliver superior levels of scalability needed to

ensure that the current progress with increased levels of integration within integrated circuits can

be maintained.

The FinFET offers many advantages in terms of IC processing that mean that it has been adopted

as a major way forwards for incorporation within IC technology.

FinFET technology has been born as a result of the relentless increase in the levels of

integration. The basic tenet of Moore\'s law has held true for many years from the earliest years

of integrated circuit technology. Essentially it states that the number of transistors on a given

area of silicon doubles every two years.

Some of the landmark chips of the relatively early integrated circuit era had a low transistor

count even though they were advanced for the time. The 6800 microprocessor for example had

just 5000 transistors. Todays have many orders of magnitude more.

basically what is finfet??

FinFET technology takes its name from the fact that the FET structure used looks like a set of

fins when viewed.

The main characteristic of the FinFET is that it has a conducting channel wrapped by a thin

silicon \"fin\" from which it gains its name. The thickness of the fin determines the effective

channel length of the device.

In terms of its structure, it typically has a vertical fin on a substrate which runs between a larger

drain and source area. This protrudes vertically above the substrate as a fin.

The gate orientation is at right angles to the vertical fin. And to traverse from one side of the fin

to the other it wraps over the fin, enabling it to interface with three side of the fin or channel.

This form of gate structure provides improved electrical control over the channel conduction and

it helps reduce leakage current levels and overcomes some other short-channel effects..

The term FinFET is used somewhat generically. Sometimes it is used to describe any fin-based,

multigate transistor architecture regardless of number of gates.

Due to the increased emphas.

More Related Content

What's hot

3D or Tri-gate transistors

3D or Tri-gate transistors are multigate transistors having gate wrapped on three sides of conducting channel of electrons.

SEBA KMT MFM5 1 Cable Sheath Testing, Fault Prelocation & Pinpointing

SEBA KMT MFM5-1 is the universal test instrument for cable sheath testing including prelocation and pinpointing of cable sheath faults - in sheath testing mode SEBA KMT MFM5-1 can detect minute cable sheath insulation damage on low and high voltage cable networks.

SEBA KMT MFM5-1 ensures fast and precise cable sheath fault location - the instrument is menu-driven and fully automatic sheath fault prelocation is accurately achieved by inputting total cable length. SEBA KMT ESG 80-2 can be combined with the MFM5-1 for earth fault location in LV-HV cables.

Cable Sheath Test & Fault Location SEBA KMT MFM5-1 Features : Sheath testing, fault prelocation and pinpointing combined in single unit, sheath testing up to 5kV, time saving prelocation of sheath fault.

Parallel wire Technique in CTO PCI

Use of Parallel wire technique to enhance procedural success in CTO PCI

Introduction to FinFET

For more information regarding the "Construction of finFET" you can contact through mail (manishkenchi111296@gmail.com)

eDRAM Cells using FinFET Technology

FinFET is nothing but a MOSFET whose body is a thin piece of silicon with gate wrapped around it.

22nm tri-gate technology

this presentation giver the outline of use of trigate technology in 22 nm technology and its manufacture

Visi fault™ visual fault locator

Visi fault™ visual fault locator. Industrial-strength fiber tracing, verification and fault location tool.

Bright red visible laser light source

• Accelerates end-to-end fiber

continuity checks

• Speeds fiber tracing and identification

• Simplifies fiber polarity verification

• Aids in location of fiber faults including

tight bends, breaks and bad connectors

Cutoff wavelength in optical fibre

Cutoff wavelength optical fibre is presentation of principal of cutoff wavelength of cabled and uncabled fibre, measurment description , measurment procedures and index of refraction explained

Cable Sniffer LV Cable Fault Locator - Operating Manual

Cable Sniffer LV Cable Fault Locator - Operating Manual

What's hot (20)

SEBA KMT MFM5 1 Cable Sheath Testing, Fault Prelocation & Pinpointing

SEBA KMT MFM5 1 Cable Sheath Testing, Fault Prelocation & Pinpointing

Effective Elastic Properties of a Molecular Monolayer at a Metal Surface

Effective Elastic Properties of a Molecular Monolayer at a Metal Surface

Cable Sniffer LV Cable Fault Locator - Operating Manual

Cable Sniffer LV Cable Fault Locator - Operating Manual

Similar to Final poster

Please read the following IEEE Spectrum articles and answer the quest.pdf

Please read the following IEEE Spectrum articles and answer the questions given. You may

want to use illustrations in your answer to the questions, and mark them up accordingly as part of

answering the questions. If you take illustrations from some source (including the IEEE

Spectrum articles) please make sure this is properly cited.

http://spectrum.ieee.org/semiconductors/nanotechnology/the-next-highperformance-transistor-

could-be-made-from-lateral-nanowires Describe a FINFET and how it works. How is it different

than the planar MOSFET described in the first 5 slides of the TFET lecture? Is the FINFET a

quantum device? Give reasons why or why not. How is the nanowire device described here

different than the FINFET? Why is this difference an advantage for the nanowire device? They

one problem with the nanowire device is capacitive coupling. What is this and explain why it is a

problem with the nanowire device?

Solution

1)

The FinFET technology promises to provide the deliver superior levels of scalability needed to

ensure that the current progress with increased levels of integration within integrated circuits can

be maintained.

The FinFET offers many advantages in terms of IC processing that mean that it has been adopted

as a major way forwards for incorporation within IC technology.

FinFET technology has been born as a result of the relentless increase in the levels of

integration. The basic tenet of Moore\'s law has held true for many years from the earliest years

of integrated circuit technology. Essentially it states that the number of transistors on a given

area of silicon doubles every two years.

Some of the landmark chips of the relatively early integrated circuit era had a low transistor

count even though they were advanced for the time. The 6800 microprocessor for example had

just 5000 transistors. Todays have many orders of magnitude more.

basically what is finfet??

FinFET technology takes its name from the fact that the FET structure used looks like a set of

fins when viewed.

The main characteristic of the FinFET is that it has a conducting channel wrapped by a thin

silicon \"fin\" from which it gains its name. The thickness of the fin determines the effective

channel length of the device.

In terms of its structure, it typically has a vertical fin on a substrate which runs between a larger

drain and source area. This protrudes vertically above the substrate as a fin.

The gate orientation is at right angles to the vertical fin. And to traverse from one side of the fin

to the other it wraps over the fin, enabling it to interface with three side of the fin or channel.

This form of gate structure provides improved electrical control over the channel conduction and

it helps reduce leakage current levels and overcomes some other short-channel effects..

The term FinFET is used somewhat generically. Sometimes it is used to describe any fin-based,

multigate transistor architecture regardless of number of gates.

Due to the increased emphas.

W04406104107

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Gy3612471250

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

REVIEW PAPER ON NEW TECHNOLOGY BASED NANOSCALE TRANSISTOR

Owing to the fact that MOSFETs can be effortlessly assimilated into ICs, they have become the heart of the

growing semiconductor industry. The need to procure low power dissipation, high operating speed and

small size requires the scaling down of these devices. This fully serves the Moore’s Law. But scaling down

comes with its own drawbacks which can be substantiated as the Short Channel Effect. The working of the

device deteriorates owing to SCE. In this paper, the problems of device downsizing as well as how the use

of SED based devices prove to be a better solution to device downsizing has been presented. As such the

study of Short Channel effects as well as the issues associated with a nanoMOSFET is provided. The study

of the properties of several Quantum dot materials and how to choose the best material depending on the

observation of clear Coulomb blockade is done. Specifically, a study of a graphene single electron

transistor is reviewed. Also a theoretical explanation to a model designed to tune the movement of

electrons with the help of a quantum wire has been presented.

REVIEW PAPER ON NEW TECHNOLOGY BASED NANOSCALE TRANSISTOR

Owing to the fact that MOSFETs can be effortlessly assimilated into ICs, they have become the heart of the

growing semiconductor industry. The need to procure low power dissipation, high operating speed and

small size requires the scaling down of these devices. This fully serves the Moore’s Law. But scaling down

comes with its own drawbacks which can be substantiated as the Short Channel Effect. The working of the

device deteriorates owing to SCE. In this paper, the problems of device downsizing as well as how the use

of SED based devices prove to be a better solution to device downsizing has been presented. As such the

study of Short Channel effects as well as the issues associated with a nanoMOSFET is provided. The study

of the properties of several Quantum dot materials and how to choose the best material depending on the

observation of clear Coulomb blockade is done. Specifically, a study of a graphene single electron

transistor is reviewed. Also a theoretical explanation to a model designed to tune the movement of

electrons with the help of a quantum wire has been presented.

Reconfigurable C and Ku band antenna Using Duelpatch

https://irjet.net/archives/V3/i2/IRJET-V3I2243.pdf

A Comparative Performance Analysis of Copper on Chip and CNTFET Nano Intercon...

https://www.irjet.net/archives/V10/i6/IRJET-V10I6150.pdf

Mlgnr interconnects with finfet driver optimized delay and power performance ...

Mlgnr interconnects with finfet driver optimized delay and power performance ...eSAT Publishing House

IJRETDual-Diameter Variation –Immune CNFET-based 7T SRAM Cell

This paper proposes a variation – tolerant dual-diameter CNFET-based 7T (seven transistor) SRAM (static random access memory) cell. The use of appropriate DCNT (diameter of CNFET) and hence Vt of CNFETs is a critical piece of our design strategy. In this work, dual-Vt and dual-diameter CNFETs have been used using suitable chiral vectors for appropriate transistors. It also investigates the impact of process, voltage and temperature variations on its design metrics and compares the results with its counterpart − CMOS-based 7T SRAM cell and standard 6T SRAM cell (only few parameters). The proposed SRAM cell offers 1.35× and 1.25× improvement in standby power on an average @ VDD = 1 V and 0.9 V respectively, 30% improvement in SNM (Static Noise Margin) over CMOS-based 7T cell. Proposed design outperforms 6T in terms of 71.4% improvement in RSNM and shows same read stability as its CMOS counterpart, It shows its robustness by offering 1.4× less spread in TRA (read access time) at 1 V and 1.2× less spread in TRA at 0.9 V than that of its CMOS counterpart at the expense of 1.6× read delay. The proposed bitcell also exhibits higher performance while writing (takes 1.3× and 1.2× less TWA (write access time) @ VDD = 1 V and VDD= 0.9 V respectively). It also proves its robustness against process variations by featuring tighter spread in TWA variability (1.4× and 1.2× @ VDD= 1 V and 0.9 V respectively).

Kg3418451855

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Novel Microstrip Antenna Design for UWB

Presentation is made for the paper presentated in the IETE conference.

ZnO based transparent electronics

Talk delivered by Jidong Jin, University of Liverpool @ CDTPV masterclass, Nov 12 2014

Nanoscale Based Digital VLSI Circuits (1) - NEHA PATEL.pptx.pdf

Nanoscale Based Digital Very Large Scale Integration Circuit.

Review of Fin FET Technology and Circuit Design Challenges

Considering the difficulties in planar CMOS transistor scaling to secure an acceptable gate to channel control

FinFET based multi-gate (MuGFET) devices have been proposed as a technology option for replacing the

existing technology. The desirability of FinFET that it’s operation principle is same as CMOS process. This

permits to lengthening the gate scaling beyond the planar transistor limits, sustaining a steep subthreshold slope,

better performance with bias voltage scaling and good matching due to low doping concentration in the channel.

There are, still, several challenges and limitations that FinFET technology has to face to be competitive with

other technology options: Fin shape, pitch, isolation, doping, crystallographic orientation and stressing as well as

device parasitic, performance and patterning approaches will be discussed.

Similar to Final poster (20)

Please read the following IEEE Spectrum articles and answer the quest.pdf

Please read the following IEEE Spectrum articles and answer the quest.pdf

REVIEW PAPER ON NEW TECHNOLOGY BASED NANOSCALE TRANSISTOR

REVIEW PAPER ON NEW TECHNOLOGY BASED NANOSCALE TRANSISTOR

REVIEW PAPER ON NEW TECHNOLOGY BASED NANOSCALE TRANSISTOR

REVIEW PAPER ON NEW TECHNOLOGY BASED NANOSCALE TRANSISTOR

Reconfigurable C and Ku band antenna Using Duelpatch

Reconfigurable C and Ku band antenna Using Duelpatch

A Comparative Performance Analysis of Copper on Chip and CNTFET Nano Intercon...

A Comparative Performance Analysis of Copper on Chip and CNTFET Nano Intercon...

Mlgnr interconnects with finfet driver optimized delay and power performance ...

Mlgnr interconnects with finfet driver optimized delay and power performance ...

RBL paper _Design_of_MIGFET_based_junctionless_transistor

RBL paper _Design_of_MIGFET_based_junctionless_transistor

Dual-Diameter Variation –Immune CNFET-based 7T SRAM Cell

Dual-Diameter Variation –Immune CNFET-based 7T SRAM Cell

Nanoscale Based Digital VLSI Circuits (1) - NEHA PATEL.pptx.pdf

Nanoscale Based Digital VLSI Circuits (1) - NEHA PATEL.pptx.pdf

Review of Fin FET Technology and Circuit Design Challenges

Review of Fin FET Technology and Circuit Design Challenges

Recently uploaded

Student information management system project report ii.pdf

Our project explains about the student management. This project mainly explains the various actions related to student details. This project shows some ease in adding, editing and deleting the student details. It also provides a less time consuming process for viewing, adding, editing and deleting the marks of the students.

Halogenation process of chemical process industries

This presentation is about nitration process of industries, unit processes of chemical engineering.

Final project report on grocery store management system..pdf

In today’s fast-changing business environment, it’s extremely important to be able to respond to client needs in the most effective and timely manner. If your customers wish to see your business online and have instant access to your products or services.

Online Grocery Store is an e-commerce website, which retails various grocery products. This project allows viewing various products available enables registered users to purchase desired products instantly using Paytm, UPI payment processor (Instant Pay) and also can place order by using Cash on Delivery (Pay Later) option. This project provides an easy access to Administrators and Managers to view orders placed using Pay Later and Instant Pay options.

In order to develop an e-commerce website, a number of Technologies must be studied and understood. These include multi-tiered architecture, server and client-side scripting techniques, implementation technologies, programming language (such as PHP, HTML, CSS, JavaScript) and MySQL relational databases. This is a project with the objective to develop a basic website where a consumer is provided with a shopping cart website and also to know about the technologies used to develop such a website.

This document will discuss each of the underlying technologies to create and implement an e- commerce website.

Quality defects in TMT Bars, Possible causes and Potential Solutions.

Maintaining high-quality standards in the production of TMT bars is crucial for ensuring structural integrity in construction. Addressing common defects through careful monitoring, standardized processes, and advanced technology can significantly improve the quality of TMT bars. Continuous training and adherence to quality control measures will also play a pivotal role in minimizing these defects.

Vaccine management system project report documentation..pdf

The Division of Vaccine and Immunization is facing increasing difficulty monitoring vaccines and other commodities distribution once they have been distributed from the national stores. With the introduction of new vaccines, more challenges have been anticipated with this additions posing serious threat to the already over strained vaccine supply chain system in Kenya.

CFD Simulation of By-pass Flow in a HRSG module by R&R Consult.pptx

CFD analysis is incredibly effective at solving mysteries and improving the performance of complex systems!

Here's a great example: At a large natural gas-fired power plant, where they use waste heat to generate steam and energy, they were puzzled that their boiler wasn't producing as much steam as expected.

R&R and Tetra Engineering Group Inc. were asked to solve the issue with reduced steam production.

An inspection had shown that a significant amount of hot flue gas was bypassing the boiler tubes, where the heat was supposed to be transferred.

R&R Consult conducted a CFD analysis, which revealed that 6.3% of the flue gas was bypassing the boiler tubes without transferring heat. The analysis also showed that the flue gas was instead being directed along the sides of the boiler and between the modules that were supposed to capture the heat. This was the cause of the reduced performance.

Based on our results, Tetra Engineering installed covering plates to reduce the bypass flow. This improved the boiler's performance and increased electricity production.

It is always satisfying when we can help solve complex challenges like this. Do your systems also need a check-up or optimization? Give us a call!

Work done in cooperation with James Malloy and David Moelling from Tetra Engineering.

More examples of our work https://www.r-r-consult.dk/en/cases-en/

Design and Analysis of Algorithms-DP,Backtracking,Graphs,B&B

Dynamic Programming

Backtracking

Techniques for Graphs

Branch and Bound

Democratizing Fuzzing at Scale by Abhishek Arya

Presented at NUS: Fuzzing and Software Security Summer School 2024

This keynote talks about the democratization of fuzzing at scale, highlighting the collaboration between open source communities, academia, and industry to advance the field of fuzzing. It delves into the history of fuzzing, the development of scalable fuzzing platforms, and the empowerment of community-driven research. The talk will further discuss recent advancements leveraging AI/ML and offer insights into the future evolution of the fuzzing landscape.

Event Management System Vb Net Project Report.pdf

In present era, the scopes of information technology growing with a very fast .We do not see any are untouched from this industry. The scope of information technology has become wider includes: Business and industry. Household Business, Communication, Education, Entertainment, Science, Medicine, Engineering, Distance Learning, Weather Forecasting. Carrier Searching and so on.

My project named “Event Management System” is software that store and maintained all events coordinated in college. It also helpful to print related reports. My project will help to record the events coordinated by faculties with their Name, Event subject, date & details in an efficient & effective ways.

In my system we have to make a system by which a user can record all events coordinated by a particular faculty. In our proposed system some more featured are added which differs it from the existing system such as security.

Nuclear Power Economics and Structuring 2024

Title: Nuclear Power Economics and Structuring - 2024 Edition

Produced by: World Nuclear Association Published: April 2024

Report No. 2024/001

© 2024 World Nuclear Association.

Registered in England and Wales, company number 01215741

This report reflects the views

of industry experts but does not

necessarily represent those

of World Nuclear Association’s

individual member organizations.

Hybrid optimization of pumped hydro system and solar- Engr. Abdul-Azeez.pdf

Advancements in technology unveil a myriad of electrical and electronic breakthroughs geared towards efficiently harnessing limited resources to meet human energy demands. The optimization of hybrid solar PV panels and pumped hydro energy supply systems plays a pivotal role in utilizing natural resources effectively. This initiative not only benefits humanity but also fosters environmental sustainability. The study investigated the design optimization of these hybrid systems, focusing on understanding solar radiation patterns, identifying geographical influences on solar radiation, formulating a mathematical model for system optimization, and determining the optimal configuration of PV panels and pumped hydro storage. Through a comparative analysis approach and eight weeks of data collection, the study addressed key research questions related to solar radiation patterns and optimal system design. The findings highlighted regions with heightened solar radiation levels, showcasing substantial potential for power generation and emphasizing the system's efficiency. Optimizing system design significantly boosted power generation, promoted renewable energy utilization, and enhanced energy storage capacity. The study underscored the benefits of optimizing hybrid solar PV panels and pumped hydro energy supply systems for sustainable energy usage. Optimizing the design of solar PV panels and pumped hydro energy supply systems as examined across diverse climatic conditions in a developing country, not only enhances power generation but also improves the integration of renewable energy sources and boosts energy storage capacities, particularly beneficial for less economically prosperous regions. Additionally, the study provides valuable insights for advancing energy research in economically viable areas. Recommendations included conducting site-specific assessments, utilizing advanced modeling tools, implementing regular maintenance protocols, and enhancing communication among system components.

Standard Reomte Control Interface - Neometrix

About

Indigenized remote control interface card suitable for MAFI system CCR equipment. Compatible for IDM8000 CCR. Backplane mounted serial and TCP/Ethernet communication module for CCR remote access. IDM 8000 CCR remote control on serial and TCP protocol.

• Remote control: Parallel or serial interface.

• Compatible with MAFI CCR system.

• Compatible with IDM8000 CCR.

• Compatible with Backplane mount serial communication.

• Compatible with commercial and Defence aviation CCR system.

• Remote control system for accessing CCR and allied system over serial or TCP.

• Indigenized local Support/presence in India.

• Easy in configuration using DIP switches.

Technical Specifications

Indigenized remote control interface card suitable for MAFI system CCR equipment. Compatible for IDM8000 CCR. Backplane mounted serial and TCP/Ethernet communication module for CCR remote access. IDM 8000 CCR remote control on serial and TCP protocol.

Key Features

Indigenized remote control interface card suitable for MAFI system CCR equipment. Compatible for IDM8000 CCR. Backplane mounted serial and TCP/Ethernet communication module for CCR remote access. IDM 8000 CCR remote control on serial and TCP protocol.

• Remote control: Parallel or serial interface

• Compatible with MAFI CCR system

• Copatiable with IDM8000 CCR

• Compatible with Backplane mount serial communication.

• Compatible with commercial and Defence aviation CCR system.

• Remote control system for accessing CCR and allied system over serial or TCP.

• Indigenized local Support/presence in India.

Application

• Remote control: Parallel or serial interface.

• Compatible with MAFI CCR system.

• Compatible with IDM8000 CCR.

• Compatible with Backplane mount serial communication.

• Compatible with commercial and Defence aviation CCR system.

• Remote control system for accessing CCR and allied system over serial or TCP.

• Indigenized local Support/presence in India.

• Easy in configuration using DIP switches.

Recently uploaded (20)

Student information management system project report ii.pdf

Student information management system project report ii.pdf

Halogenation process of chemical process industries

Halogenation process of chemical process industries

Final project report on grocery store management system..pdf

Final project report on grocery store management system..pdf

Quality defects in TMT Bars, Possible causes and Potential Solutions.

Quality defects in TMT Bars, Possible causes and Potential Solutions.

Vaccine management system project report documentation..pdf

Vaccine management system project report documentation..pdf

CFD Simulation of By-pass Flow in a HRSG module by R&R Consult.pptx

CFD Simulation of By-pass Flow in a HRSG module by R&R Consult.pptx

Design and Analysis of Algorithms-DP,Backtracking,Graphs,B&B

Design and Analysis of Algorithms-DP,Backtracking,Graphs,B&B

Hybrid optimization of pumped hydro system and solar- Engr. Abdul-Azeez.pdf

Hybrid optimization of pumped hydro system and solar- Engr. Abdul-Azeez.pdf

Final poster

- 1. RISE OF THE NANOWIRE TRANSISTOR Compound-semiconductor nanowire to keep smartphones charged longer Chalamaneni Jeevan Prasad (154M1A0419) Department of E.C.E, VEMU Institute of Technology, Chittoor 517124 ABSTRACT 1. Superior gate control (minimize channel effects). 2. High drive current. 3. Less sensitive to process variations. 4. Improved transport property. 5. Ultimate limit on the current trend of down Scaling transistors and integrated circuits to achieve faster speeds and lower power consumption INTRODUCTION NANO WIRE Nanowires are microscopic wires that have a width measured in Nano meters. Typically their width ranges from forty to fifty Nano meters, but their length is not so limited. Since they can be lengthened by simply attaching more wires end to end or just by growing them longer, they can be as long as desired. FEATURES SIZE IMPRESSION ON NANO WIRE REFERENCES CONCLUSION RESULT Reduction in lattice thermal conductance as high as 30% obtained by 20% atom removal. Weak material depend Si & Ge nanowire show similar reduction. Node reduction in lattice thermal conductance. RTDs is much faster than any other conventional trans. Very good rectifier low leakage current. Much research needs to be done to improve the output power and also to integrate them with conventional transistors. Volume inversion dominant until dnw=4nm. Surface phonon and back scattering dominant below dnw=4nm. We cherish our smartphones for delivering entertainment and information on the go but their need for daily charging is a problem. So when new smartphone models come on the market with Microprocessors based on the latest foundry process, the increase in the number of transistors in the chips should be balanced by a reduction in the power. https://ieeexplore.ieee.org/abstract/document/4419093 GSDSAT VI Sung Dae Suk, et al., “Investigation of nanowire size dependency on TSNWFET,” IEDM 2007, pp. 891-894. Kyoung Hwan Yeo, et al., “Gate-All-Around (GAA) Twin Silicon Nanowire MOSFET (TSNWFET),” IEDM 2006. ▪ At around 10 nanometres from the interface, the quality of the material is very good, so we can grow the. Channel layers. ▪ The total thickness for the layers bridging the difference in lattice spacing is just 150 nm, compared with roughly 1μm. ▪ Traditional buffer layers, meaning less material, lower costs, and faster production. ▪ It avoids many complications of crystal growth. ▪ The nanowire devices also yielded a trans conductance of 1,057 μS/μm, which is a record for electron-transporting germanium nanowire FETs.