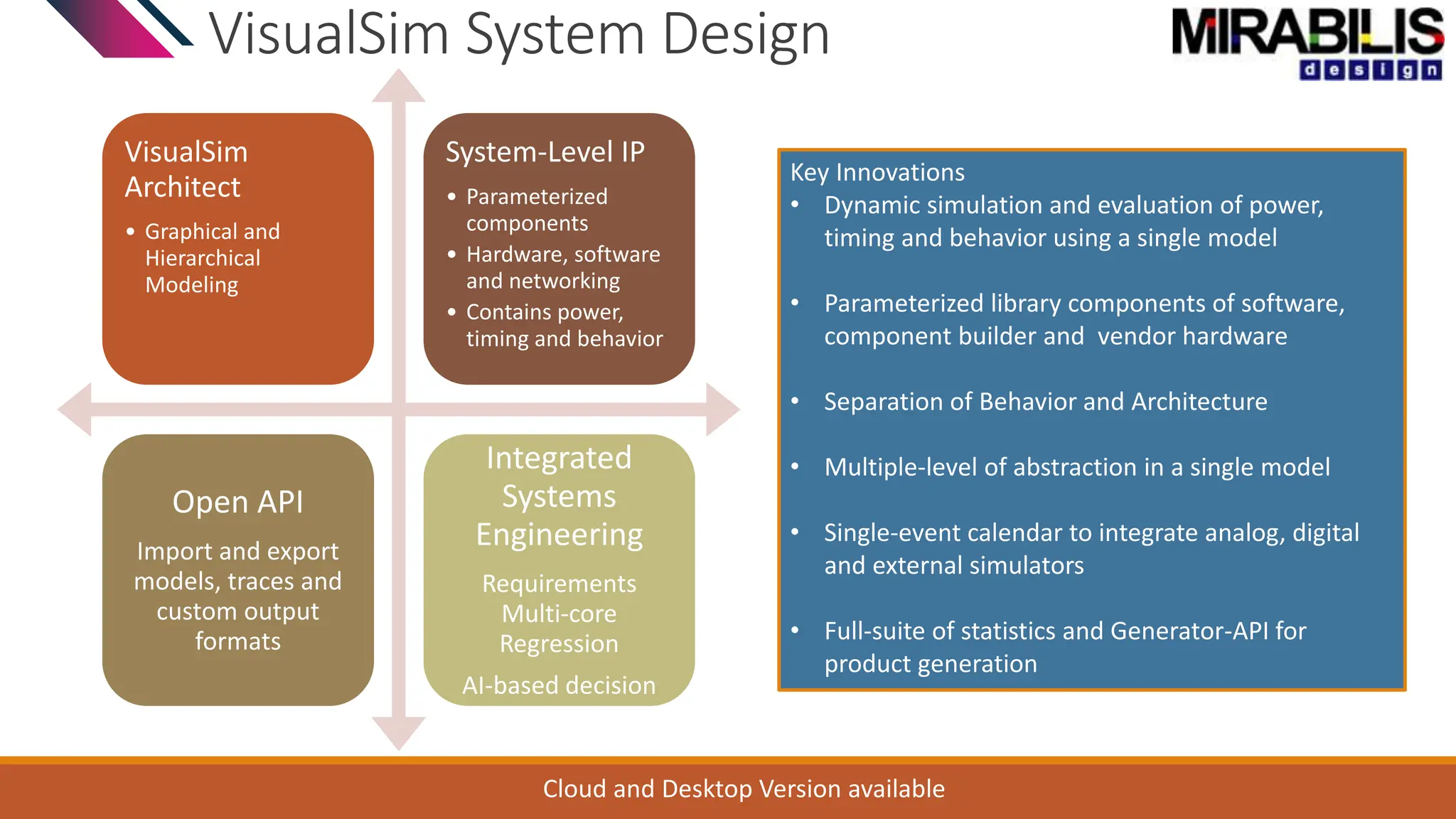

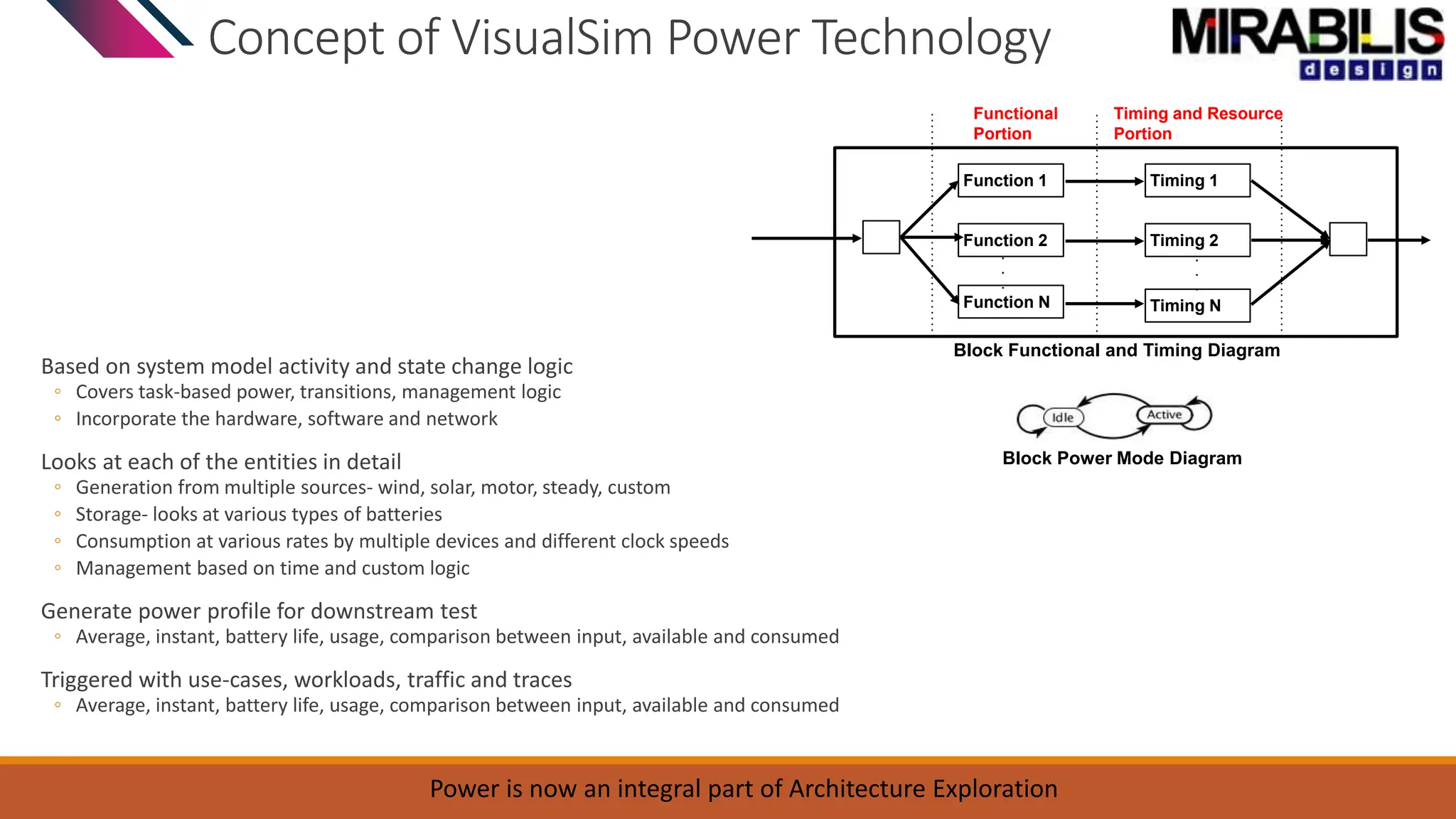

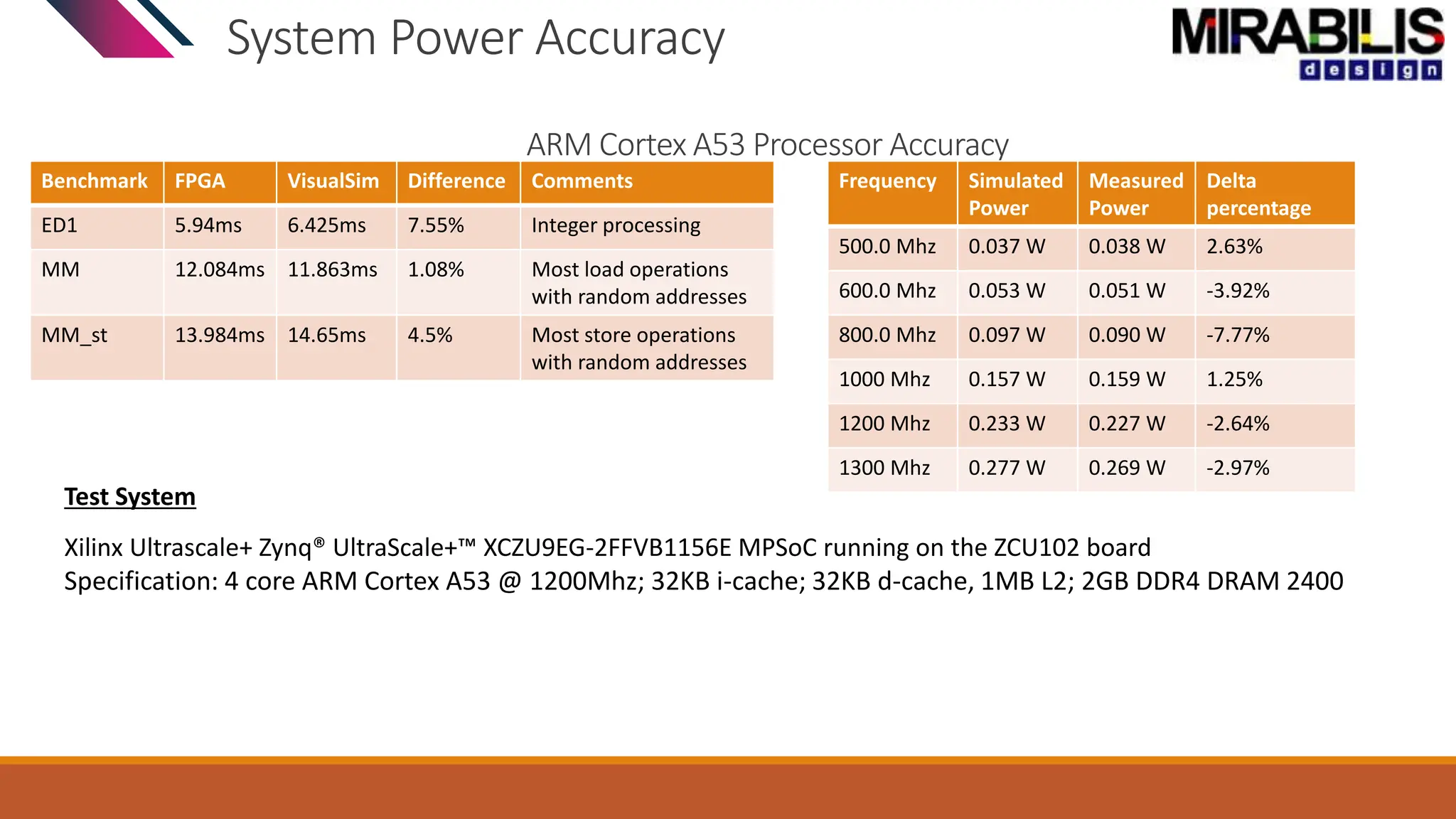

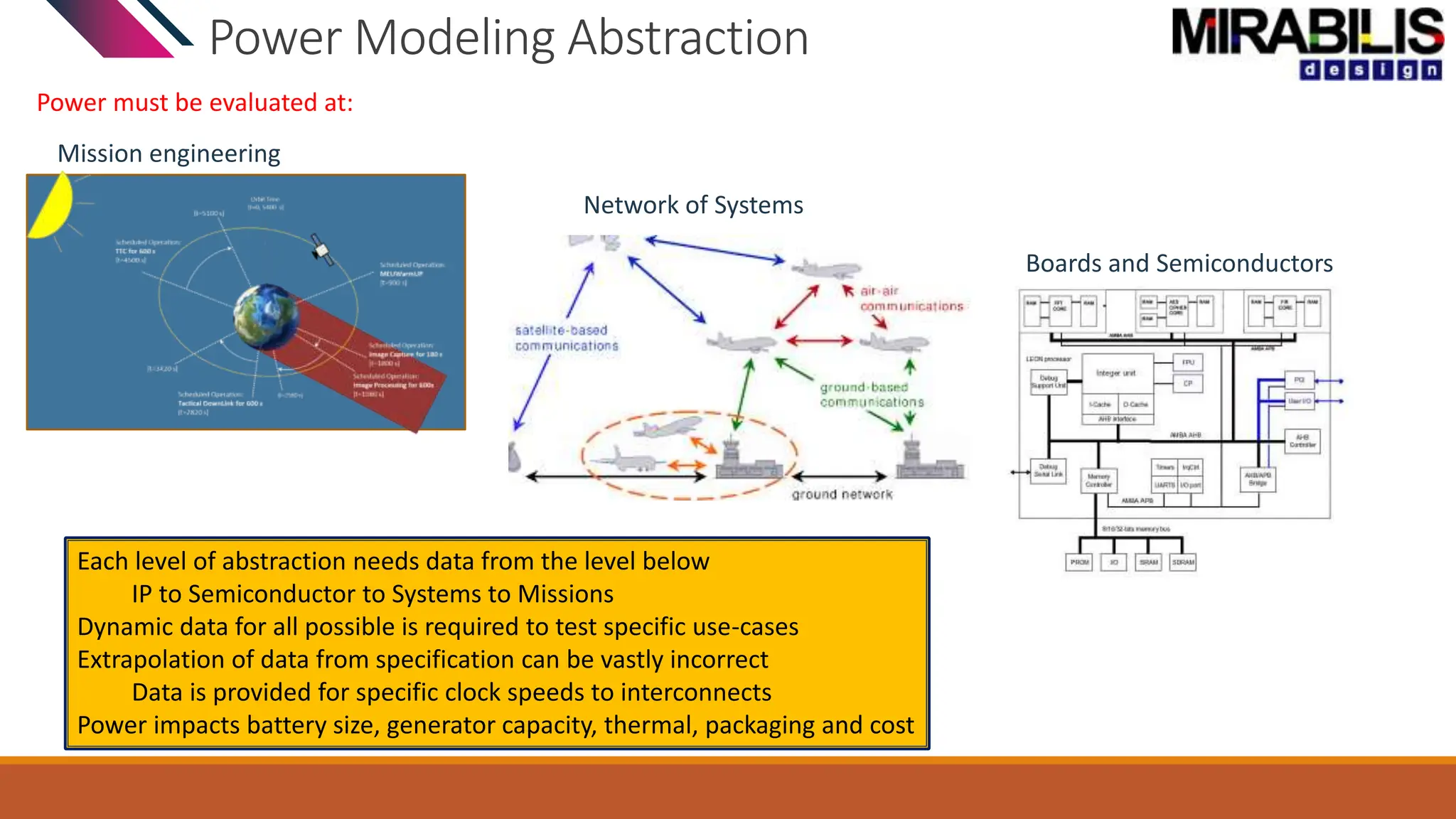

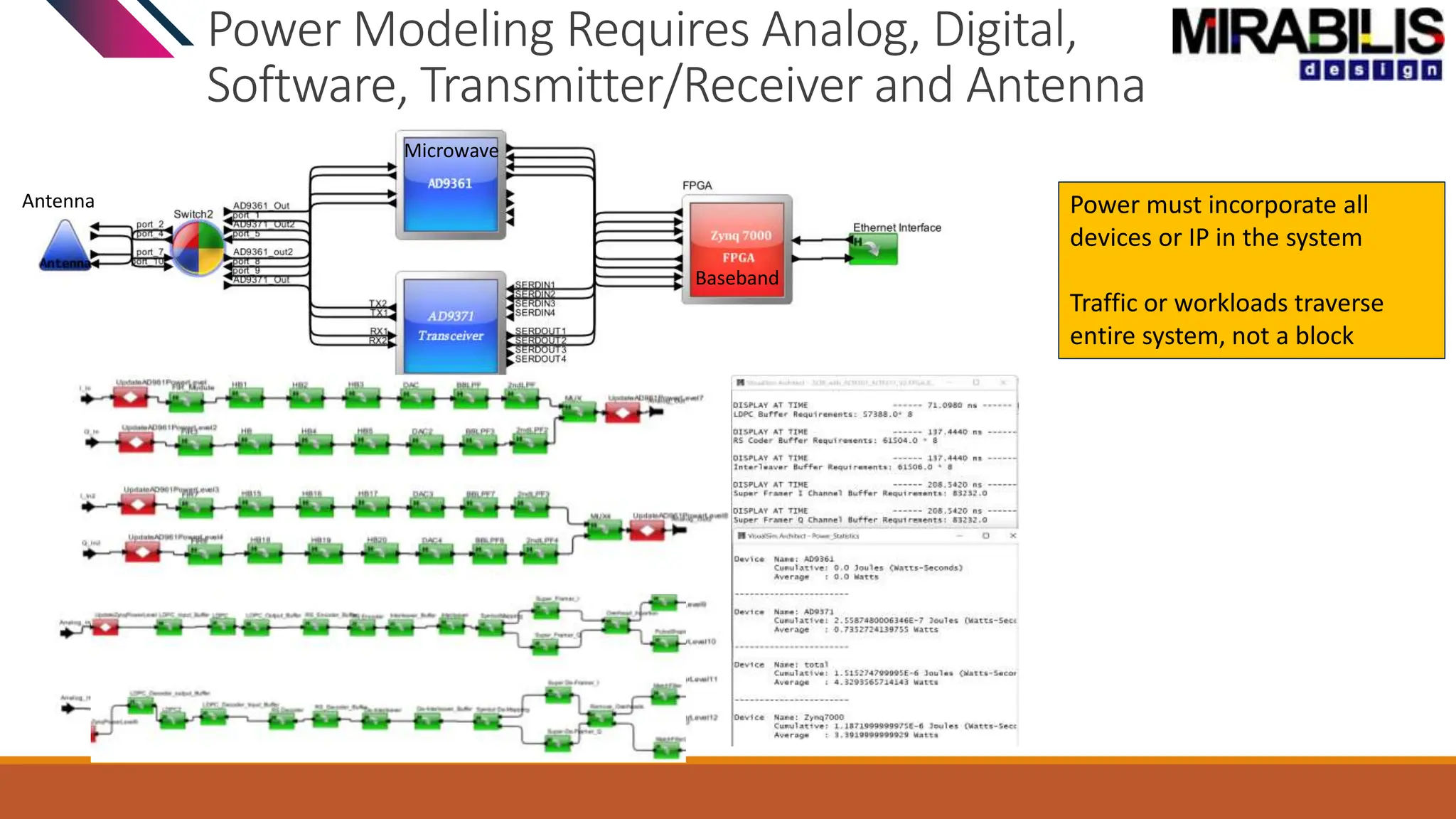

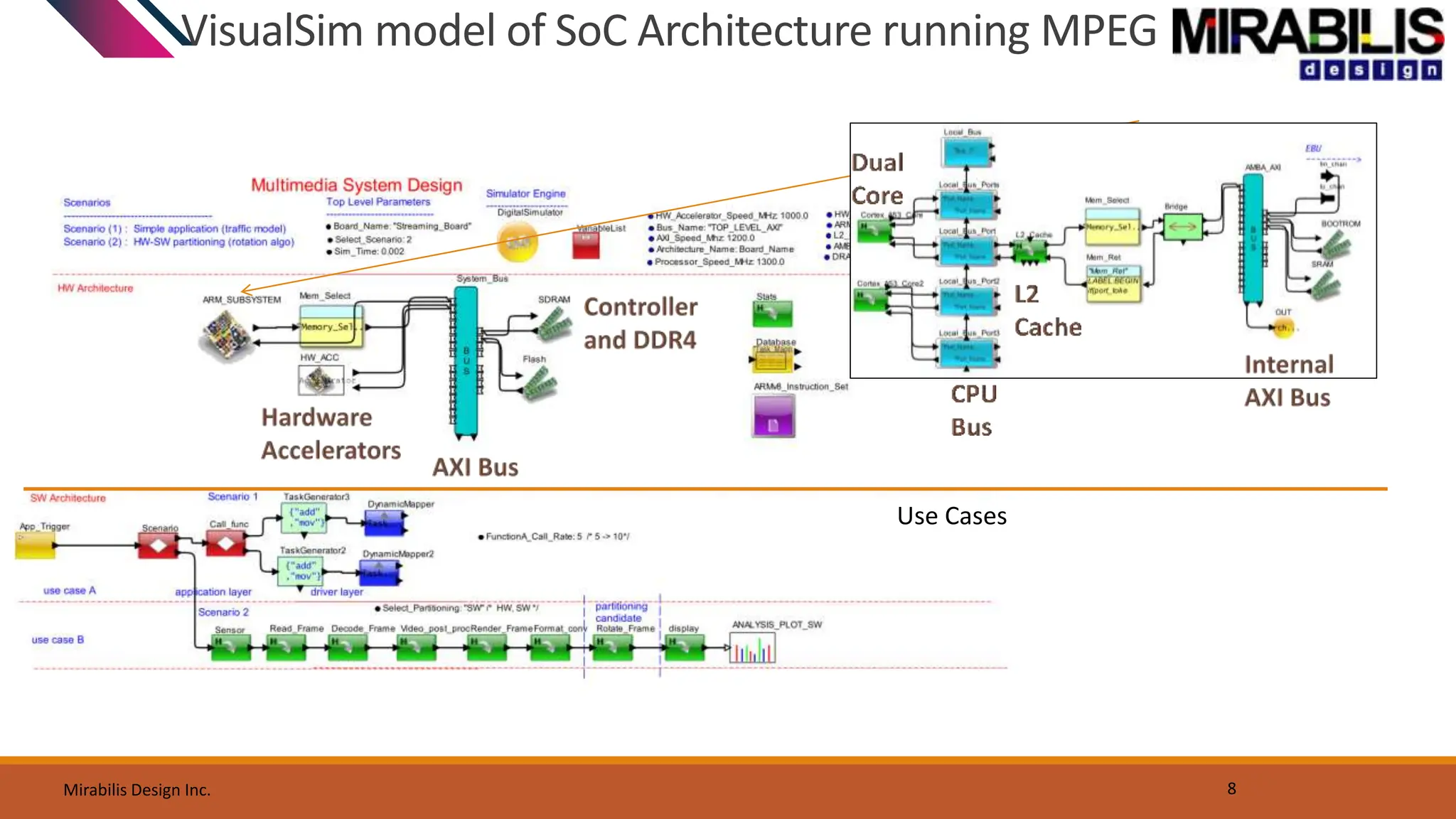

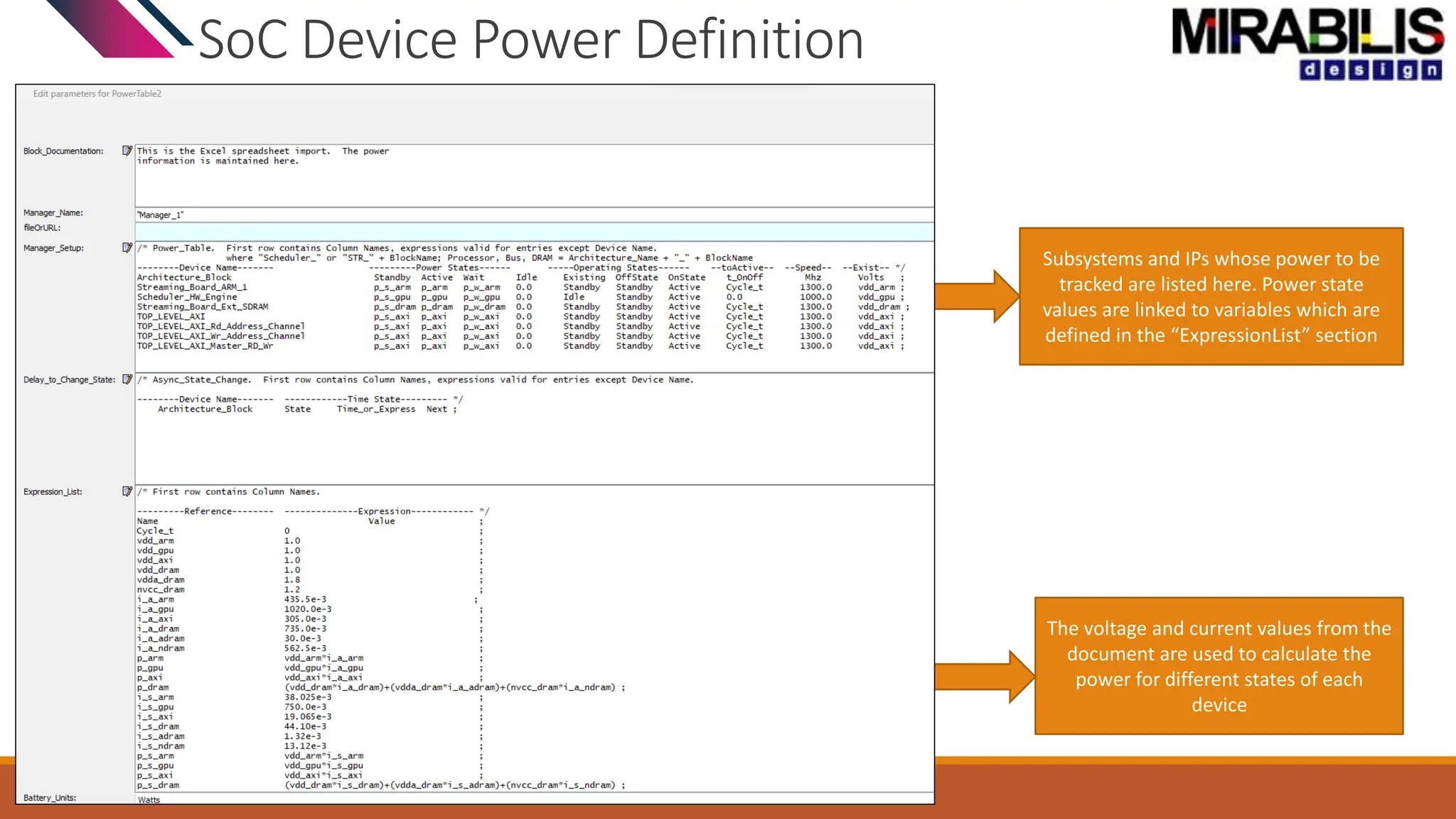

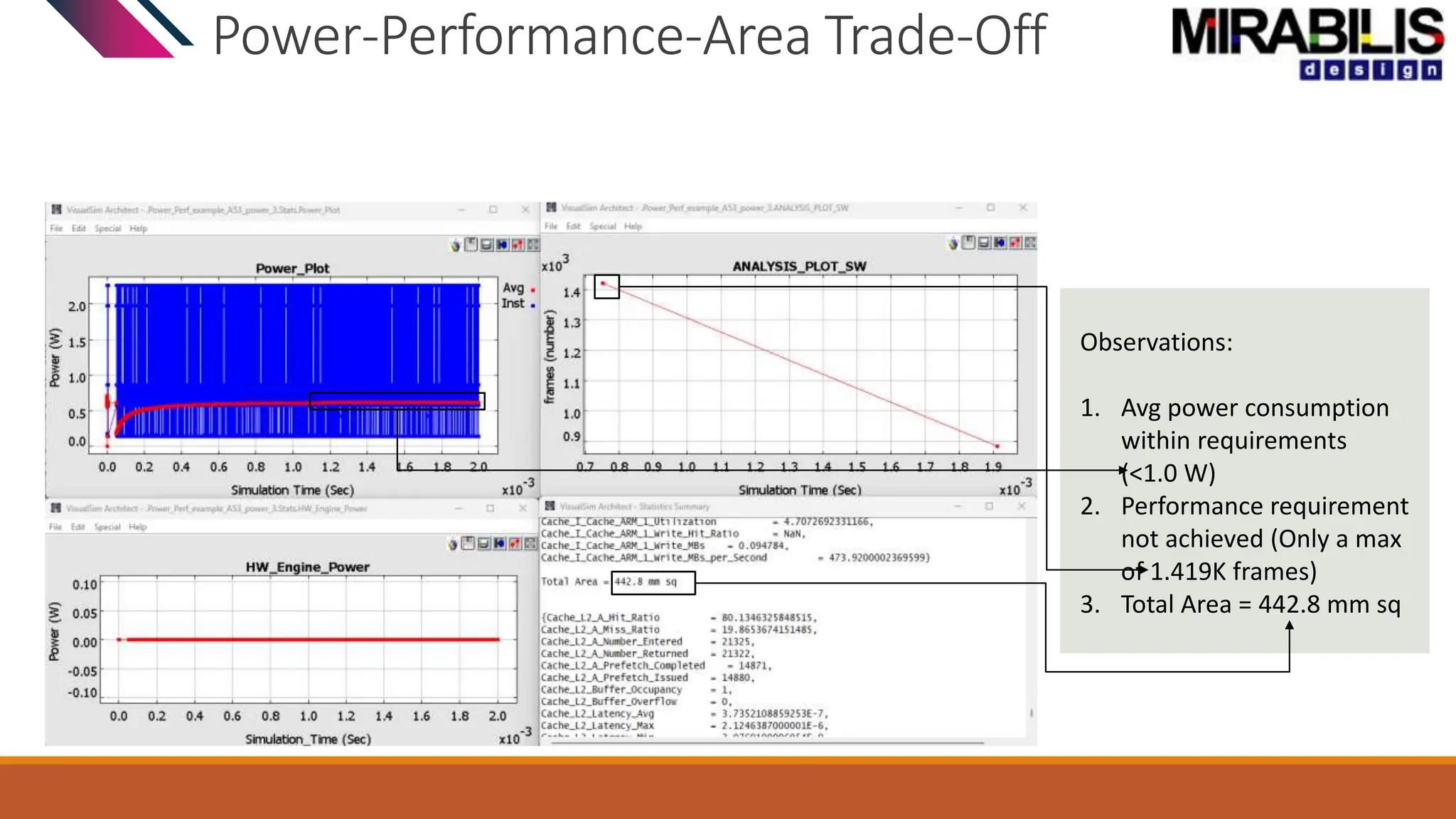

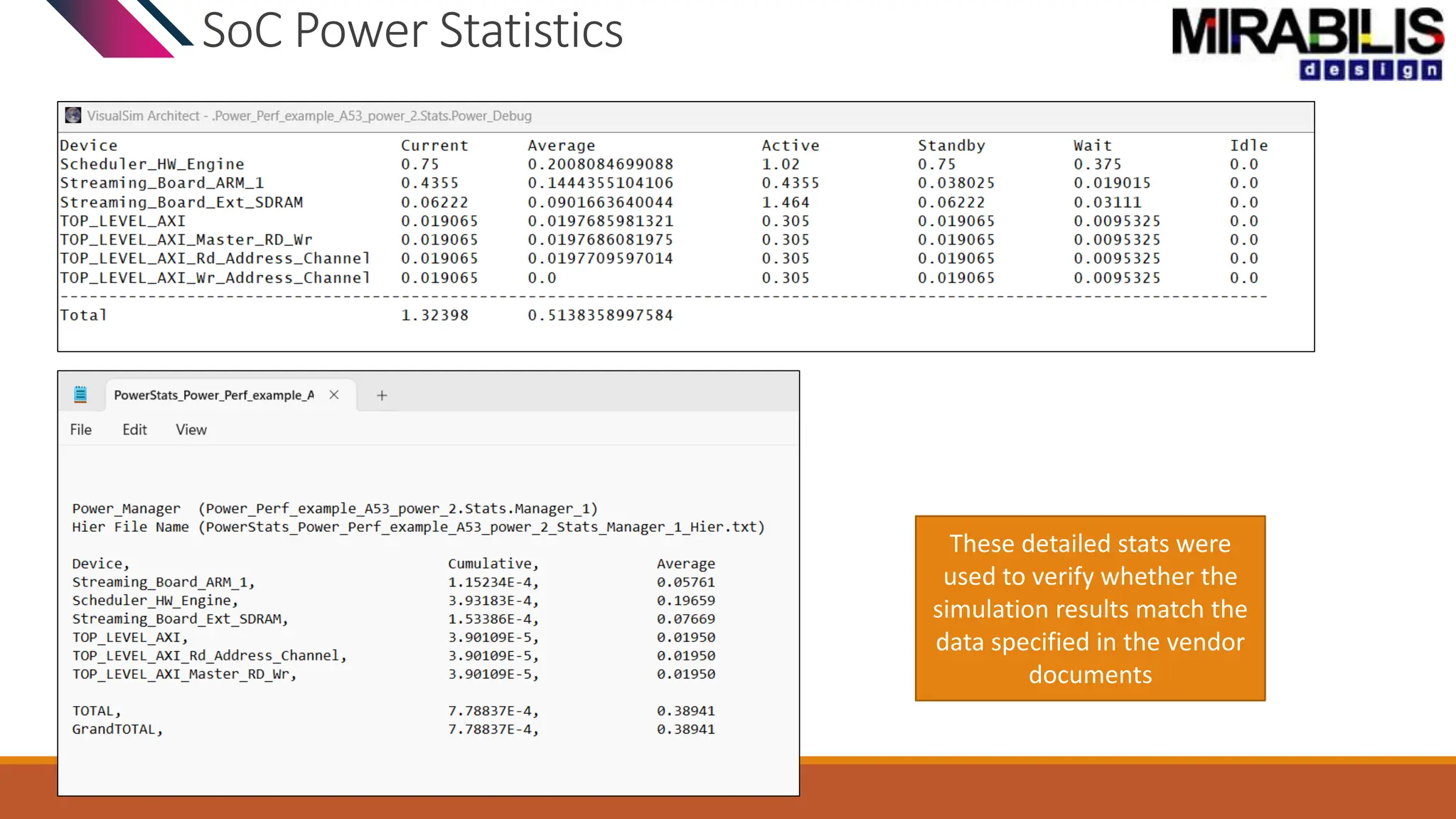

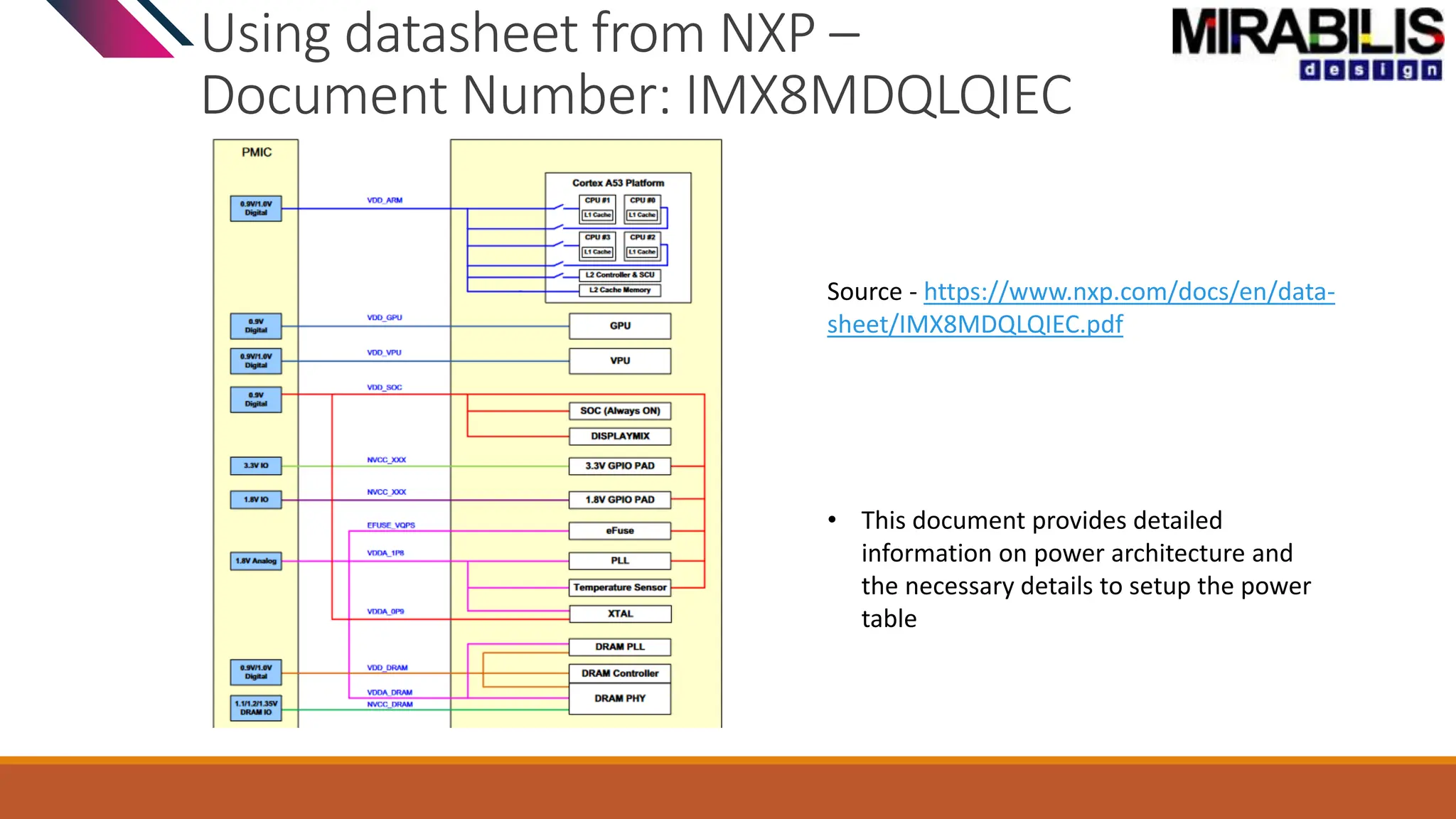

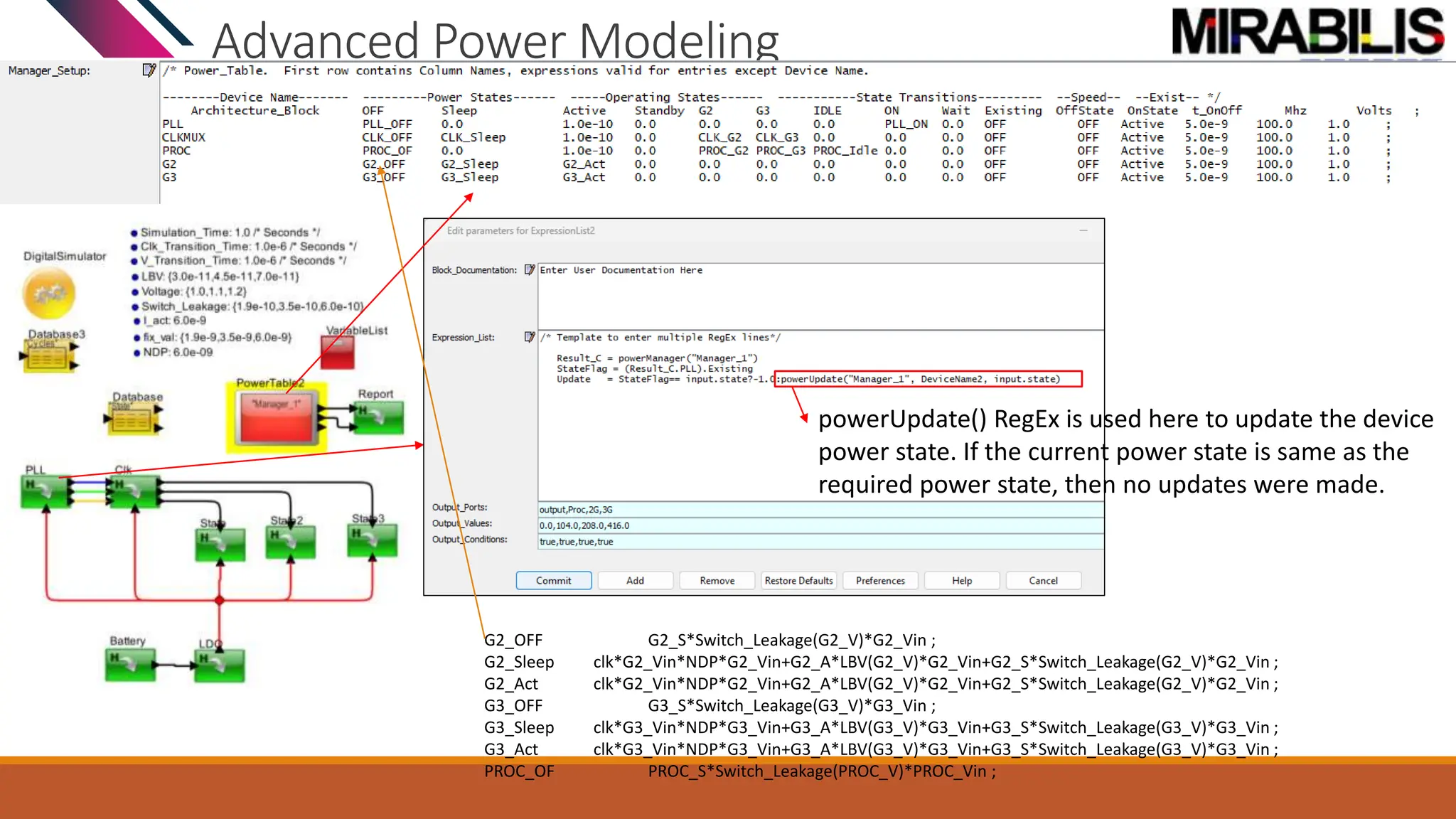

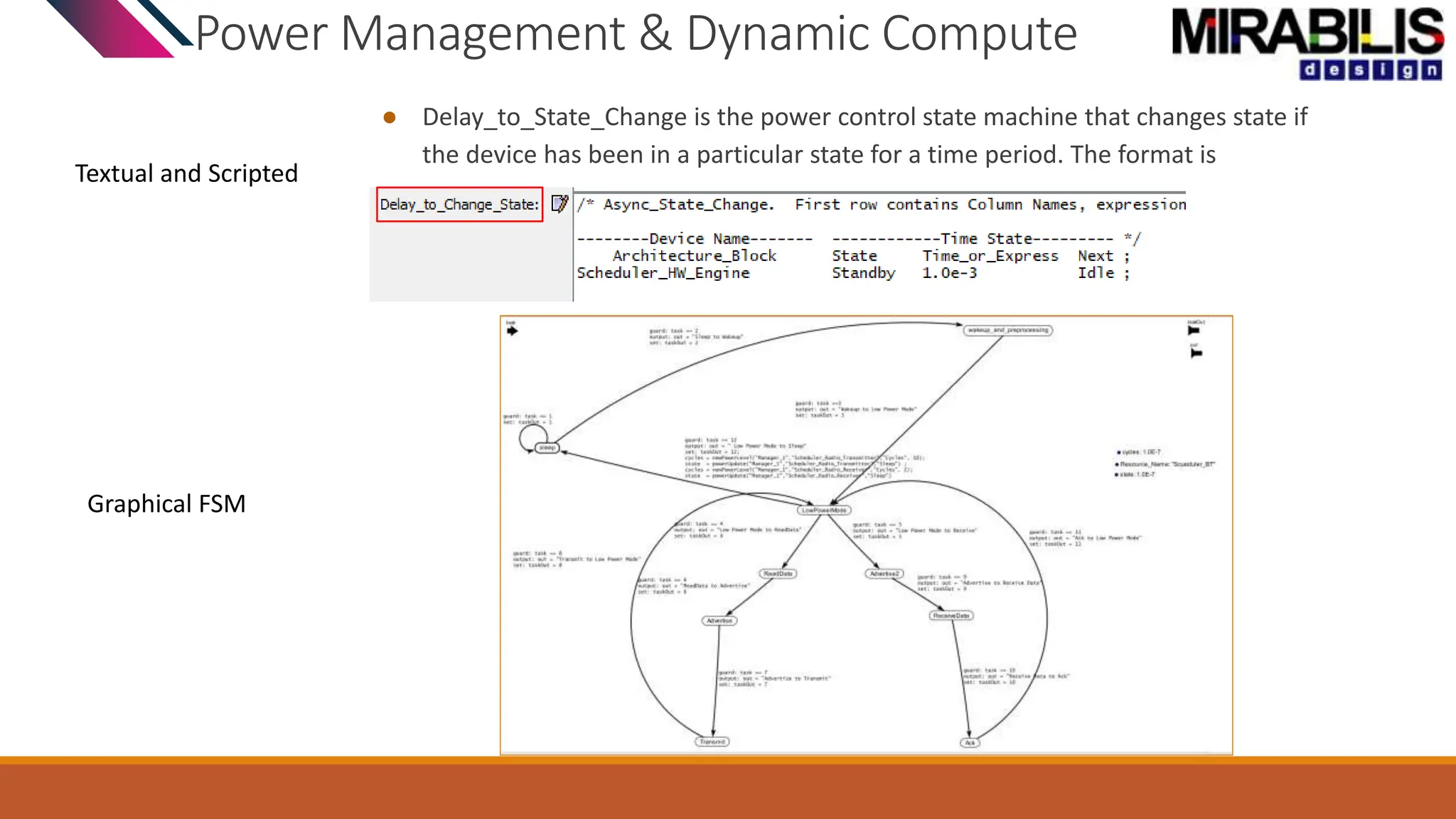

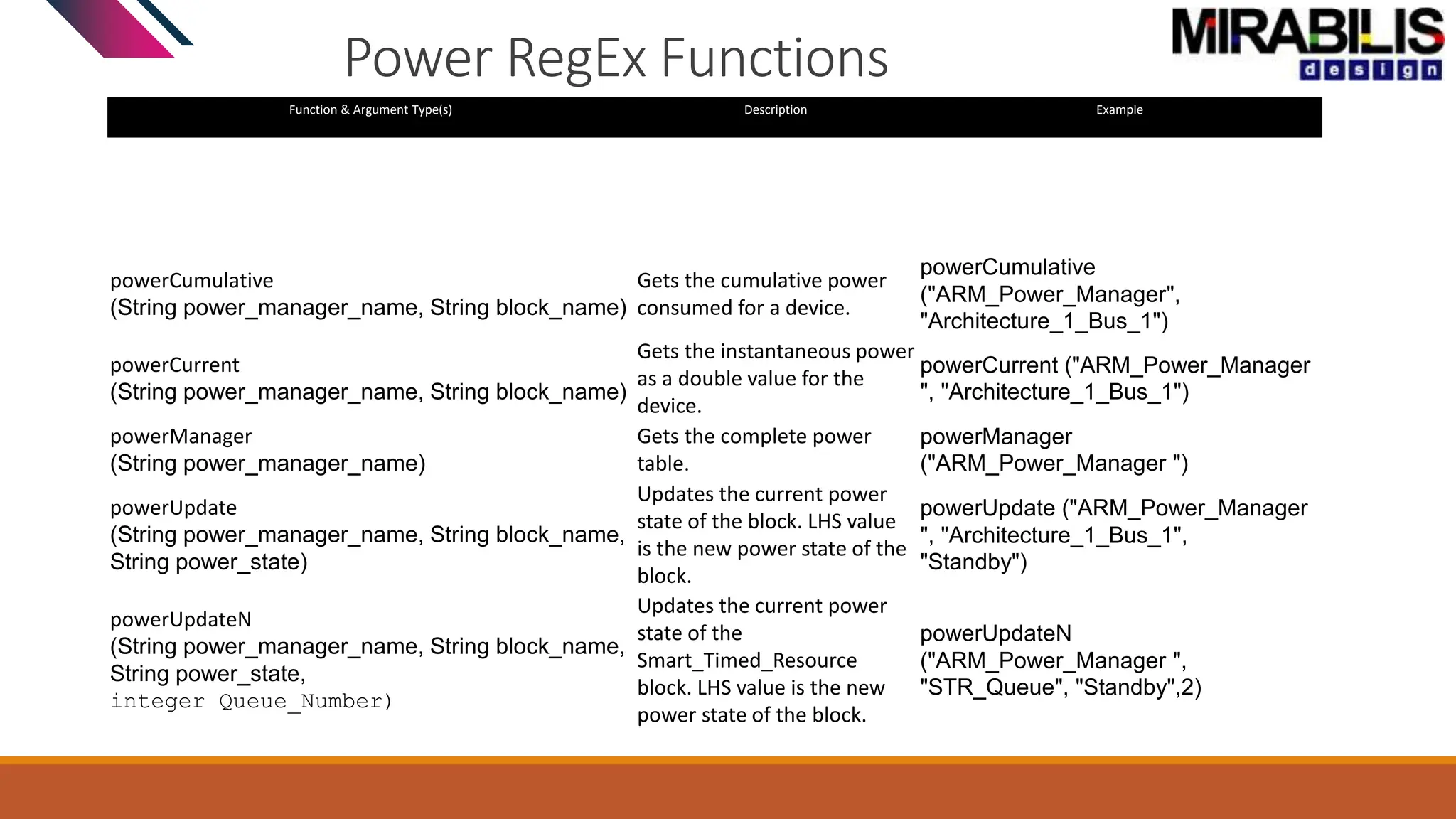

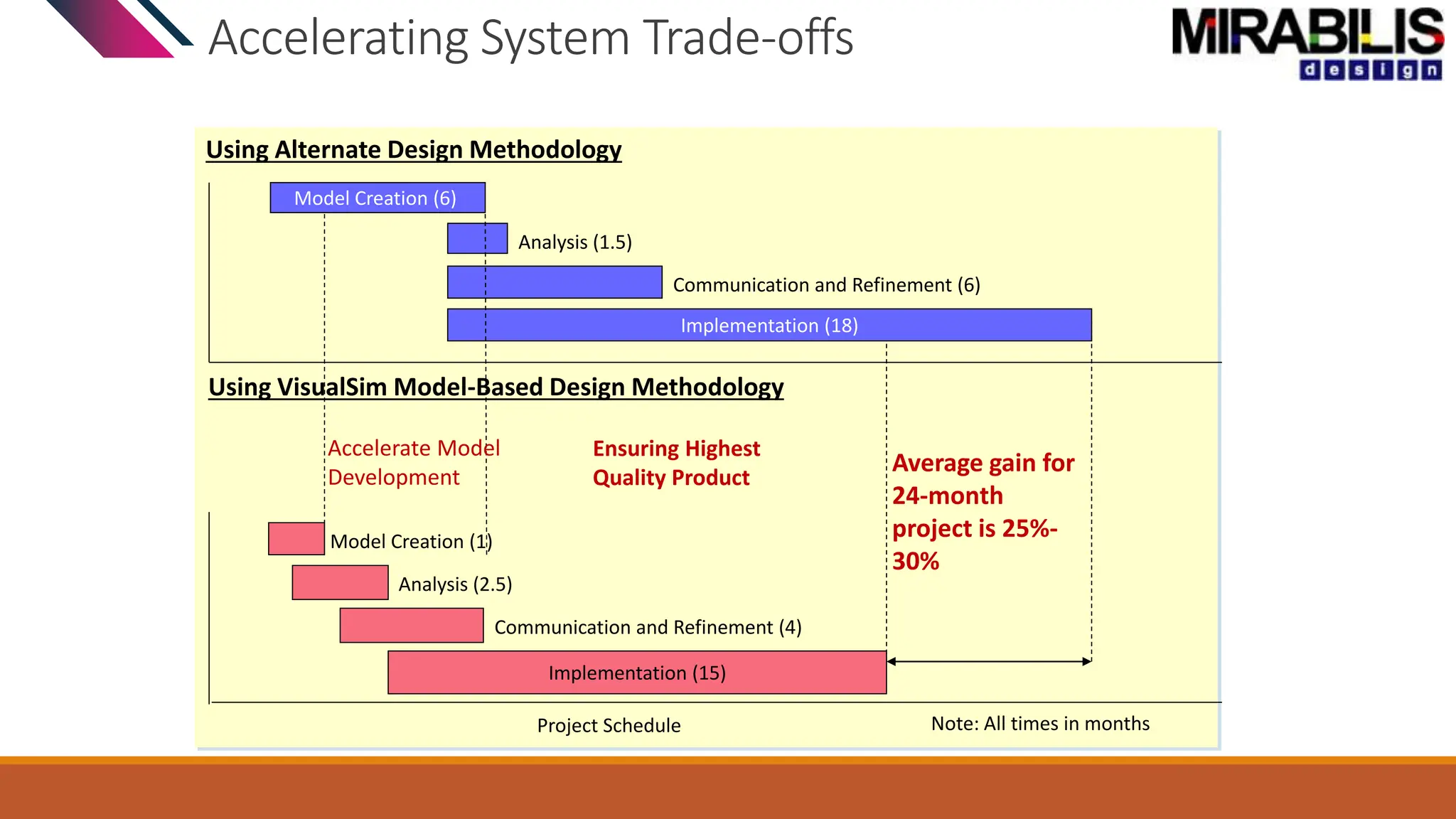

Mirabilis Design is a software company that develops VisualSim Architect modeling and simulation software to optimize system specifications prior to development. The software enables power-performance-area modeling and simulation of semiconductor systems and software. It uses dynamic simulation and evaluation of power, timing, and behavior using a single system model. This achieves 95%+ accurate power measurement during architecture exploration. The software separates behavior and architecture and supports multiple abstraction levels in a single model to optimize system designs early in the development process.