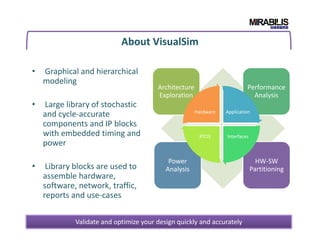

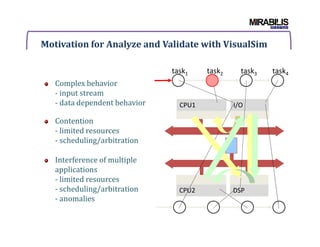

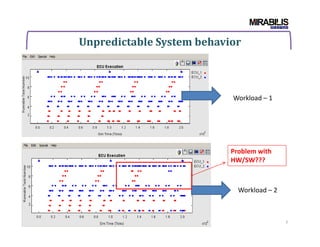

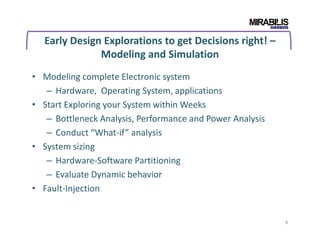

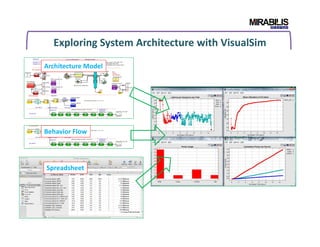

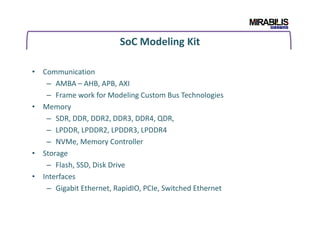

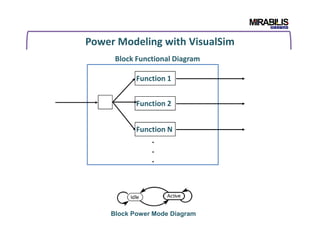

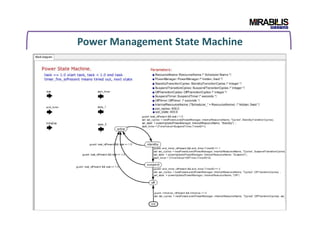

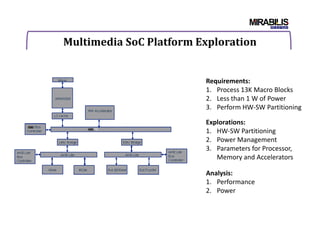

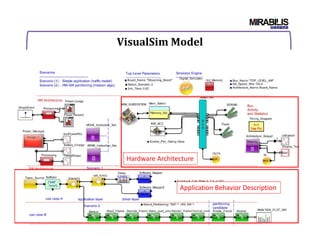

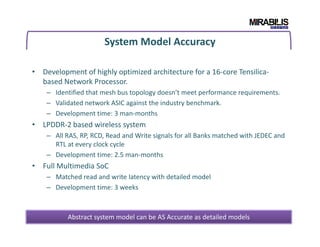

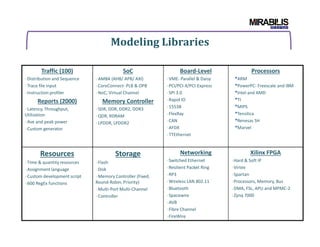

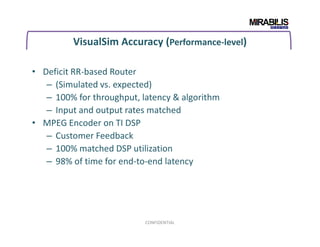

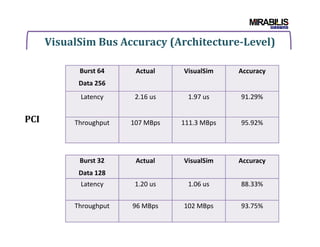

The document discusses how to create innovative architecture using VisualSim, emphasizing the importance of system-level modeling and simulation for analyzing complex electronic systems. It outlines the capabilities of Mirabilis Design's software, including performance and power analysis, hardware-software partitioning, and the extensive library of modeling components. Additionally, it highlights the accuracy and development efficiency achieved through VisualSim in various applications and architectures.