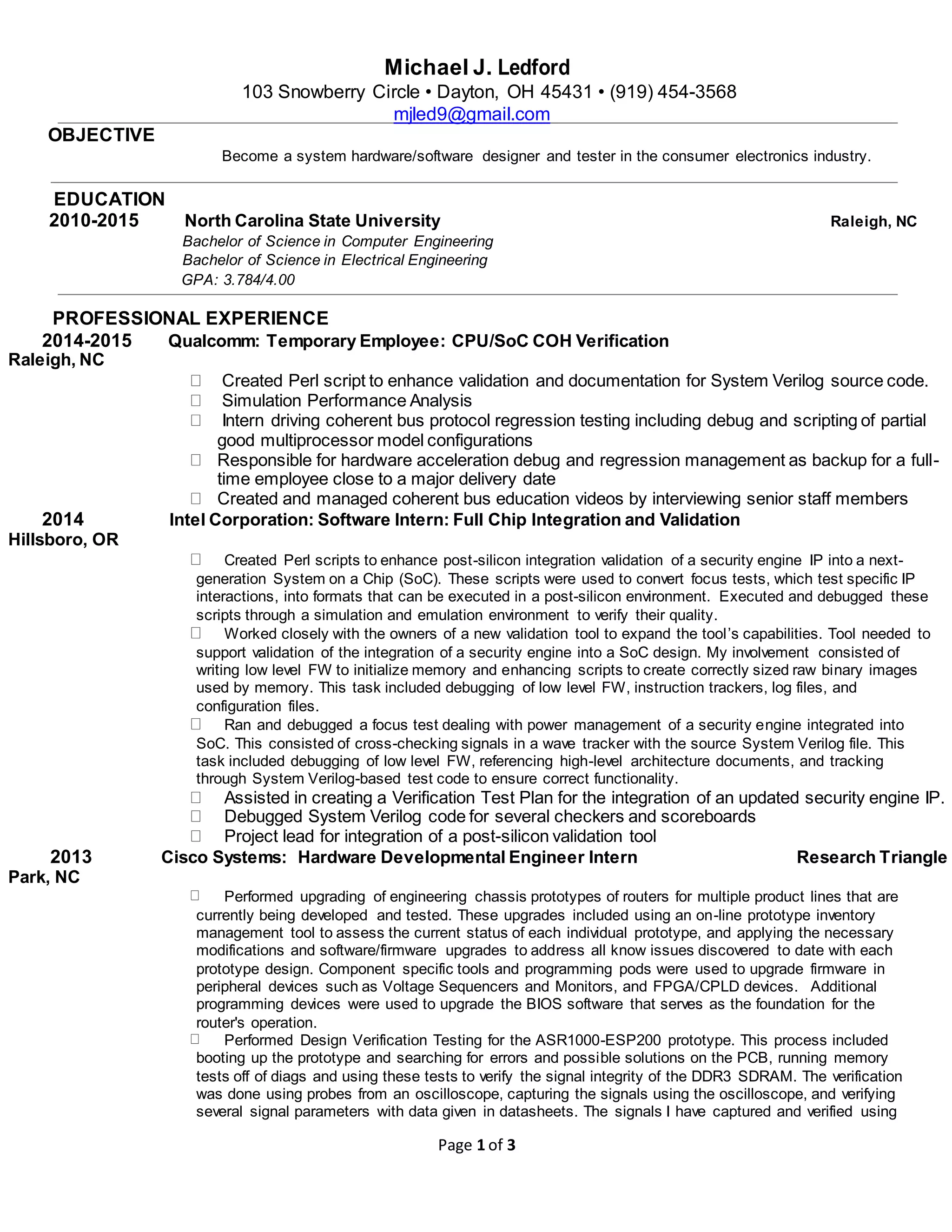

Michael J. Ledford has a Bachelor of Science in Computer Engineering and Electrical Engineering from North Carolina State University. He has experience in hardware and software design, verification, and testing roles at Qualcomm, Intel, and Cisco. His skills include SystemVerilog, Perl/Python scripting, hardware debugging, and signal integrity analysis. He is looking for a role as a system hardware/software designer and tester in the consumer electronics industry.