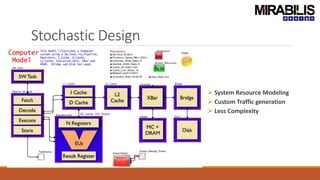

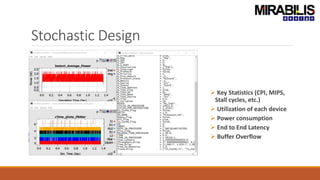

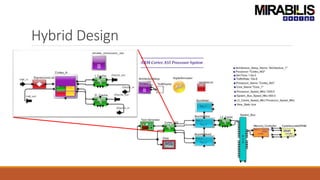

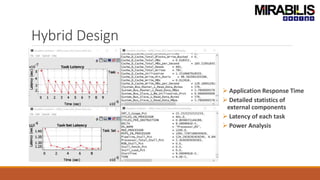

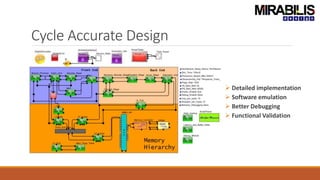

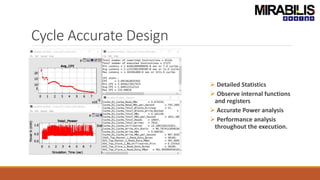

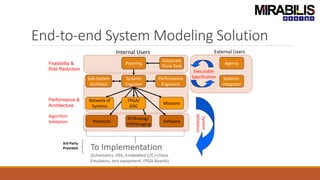

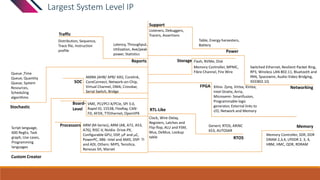

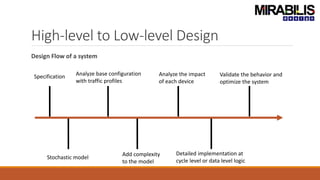

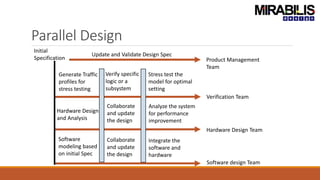

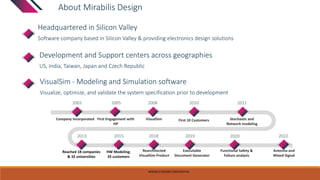

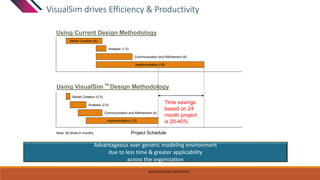

The webinar presented by Akash from Mirabilis Design focuses on modeling abstraction, covering system design methodologies, and the implications of stochastic and hybrid modeling approaches on performance and validation. It emphasizes the importance of detailed analysis at various abstraction levels to optimize design and resource usage while improving system stability and performance. Mirabilis Design, headquartered in Silicon Valley, specializes in electronic design solutions and offers the VisualSim software for efficient modeling and simulation.