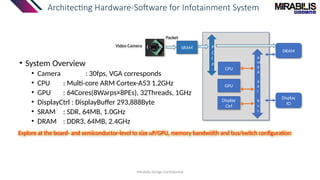

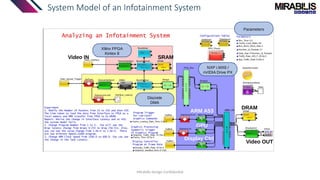

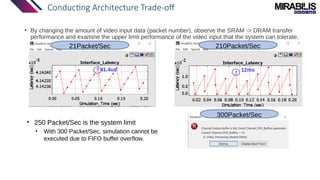

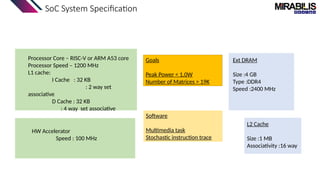

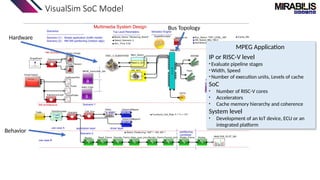

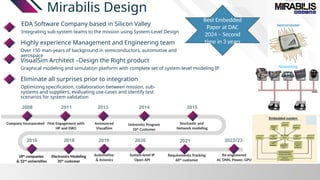

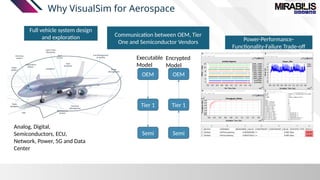

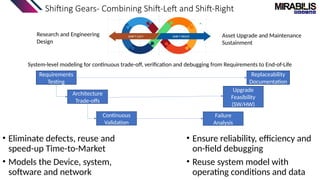

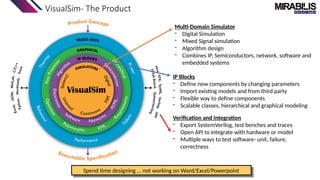

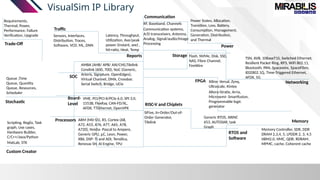

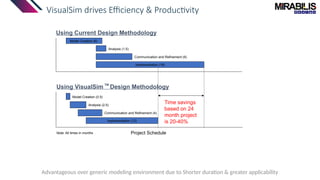

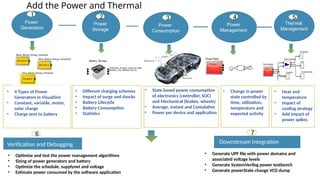

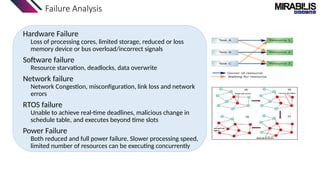

Mirabilis Design is an EDA software company based in Silicon Valley that specializes in system-level design integration for automotive, aerospace, and semiconductor sectors. Their flagship product, VisualSIM, allows for graphical modeling and simulation to optimize specifications and validate system performance across various applications. The company has developed advanced capabilities in power management, modeling, and embedded systems, alongside a comprehensive library for verification and integration in complex designs.

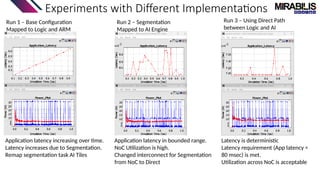

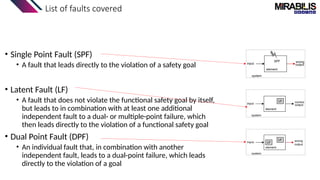

![Mapping Algorithm to Multi-Resources

Standard HW

Library

Component

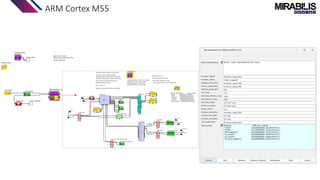

Basic/Starting Configuration

Grayscale_Conversion - PS [A72 Core 1]

IIR – Logic (PL)

FFT – AI Engine Tile

Edge_Image - Logic (PL)

iFFT – AI Engine Tile

Edge_Image_Enhancement – Logic (PL)

Segmentation – PS [A72 Core 2]

Image

Processing

Algorithm](https://image.slidesharecdn.com/mirabilispresentationsccjuly2024-240828093554-b06e0872/85/Mirabilis_Presentation_SCC_July_2024-pptx-24-320.jpg)