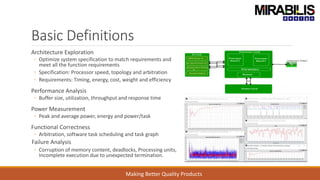

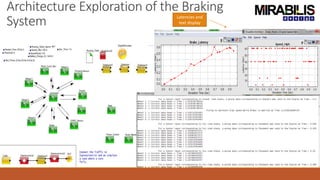

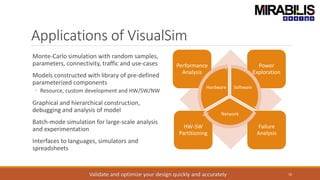

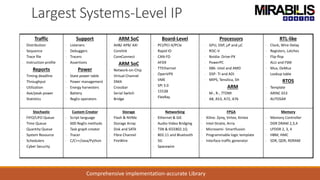

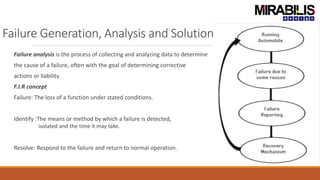

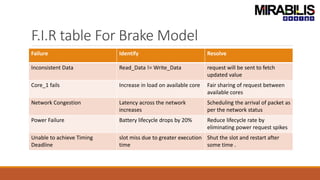

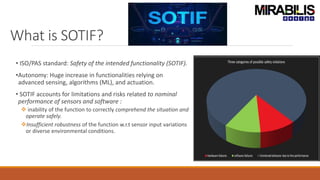

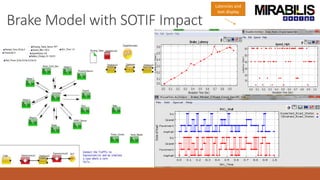

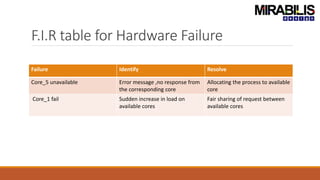

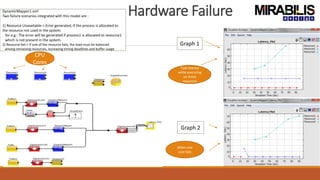

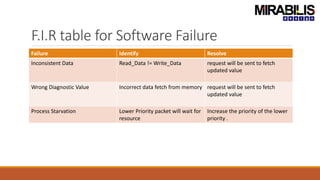

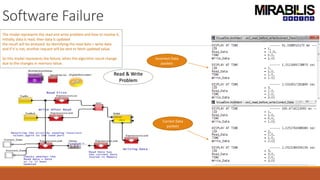

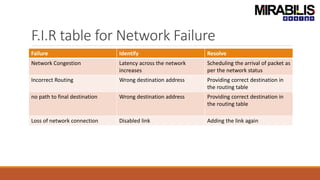

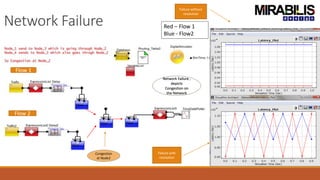

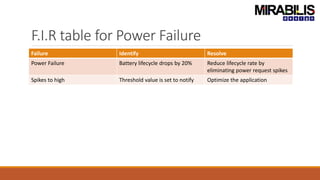

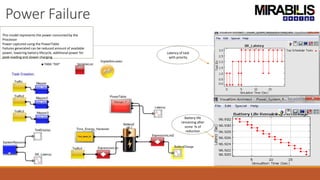

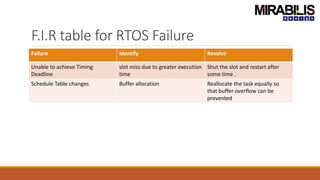

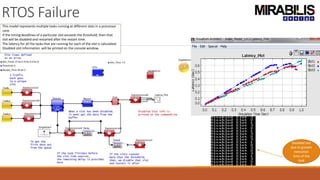

The document discusses a webinar on functional safety failure analysis, particularly for electronics and software systems, presented by Mohini Yadav from Mirabilis Design Inc. Key topics include failure identification and resolution in systems like brake models, showcasing the use of VisualSim for architecture exploration and performance analysis. The meeting also covers various types of failures including hardware, software, and network issues, along with the importance of ensuring functional safety and compliance with standards like SOTIF.