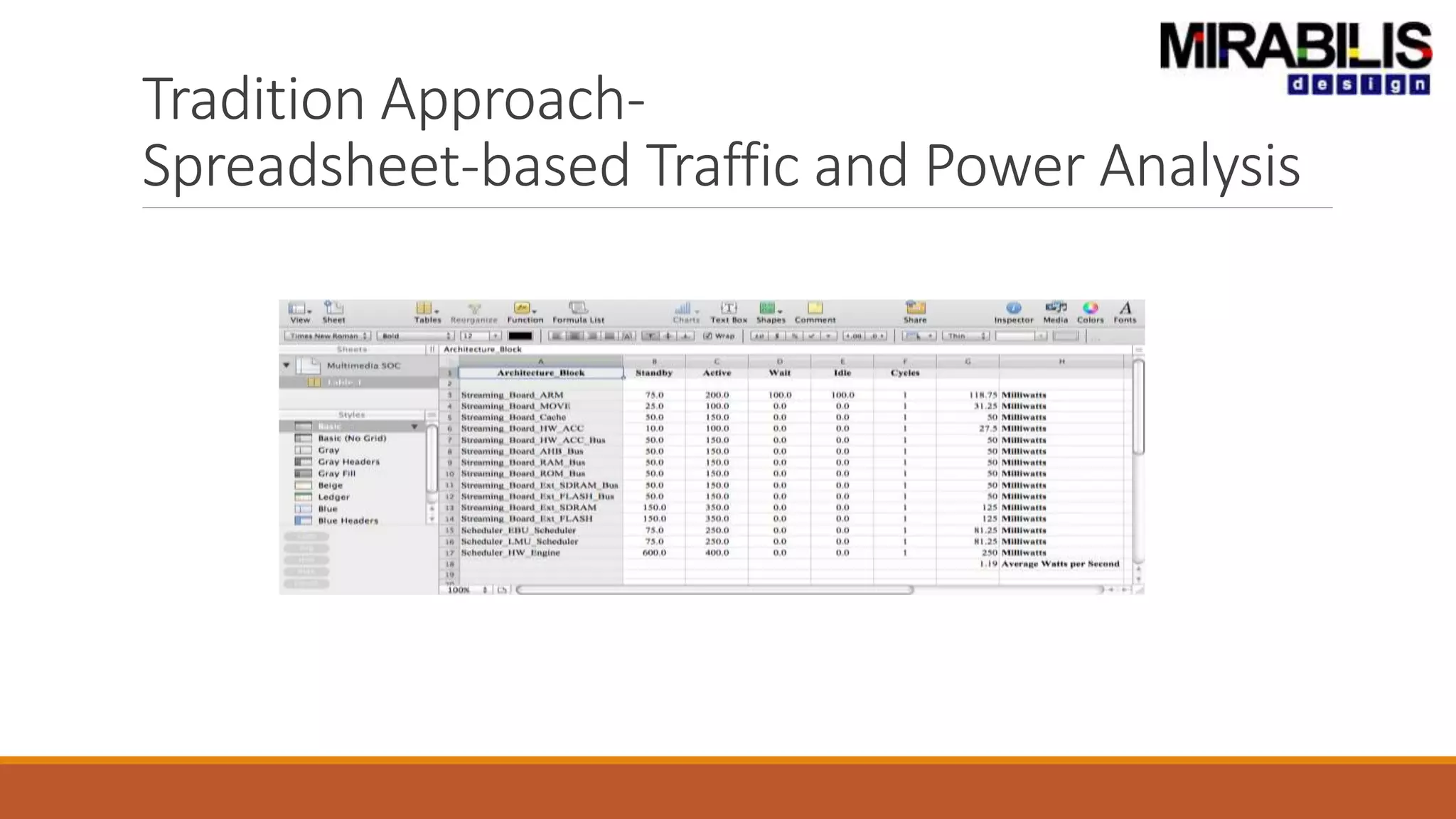

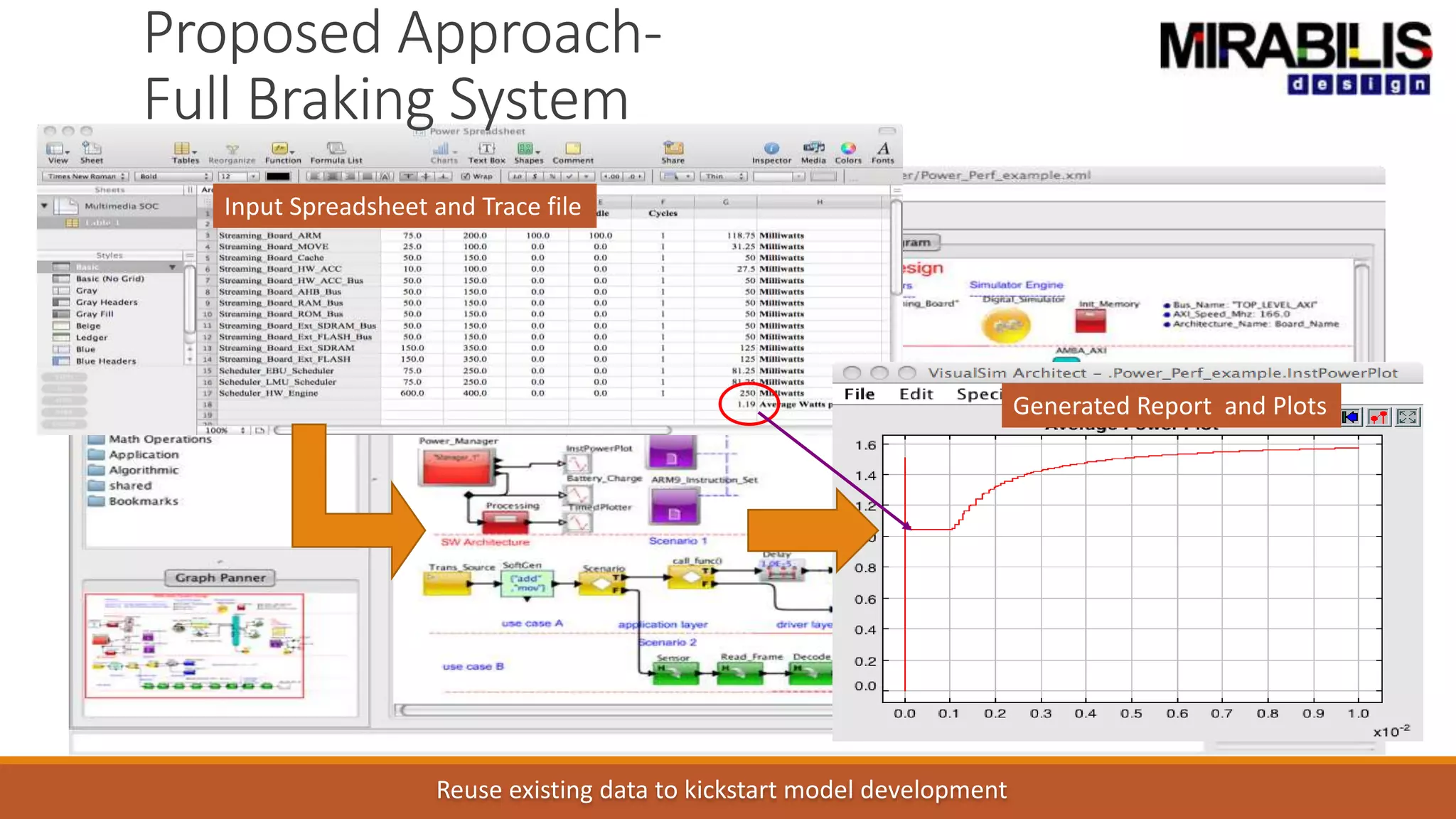

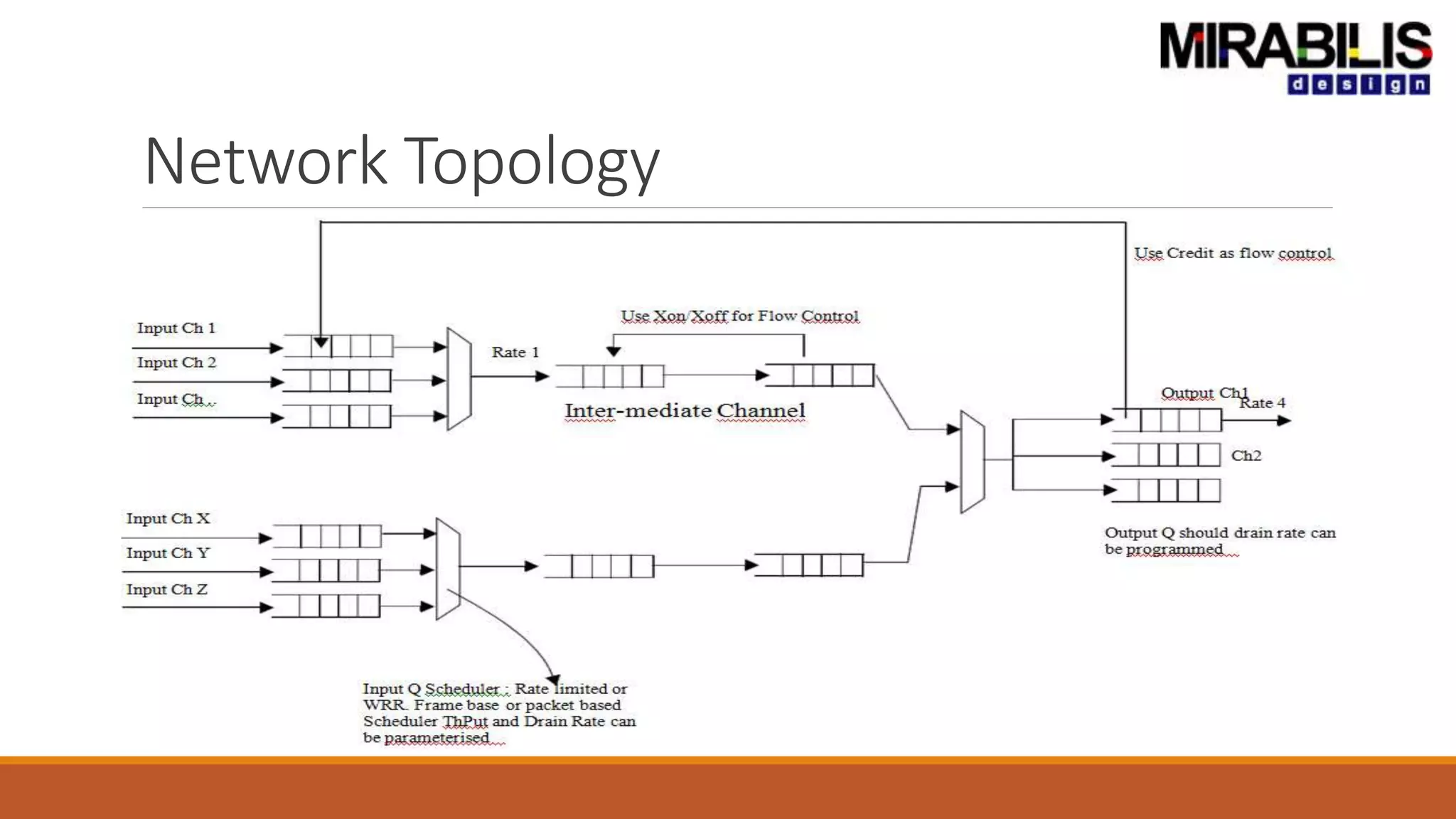

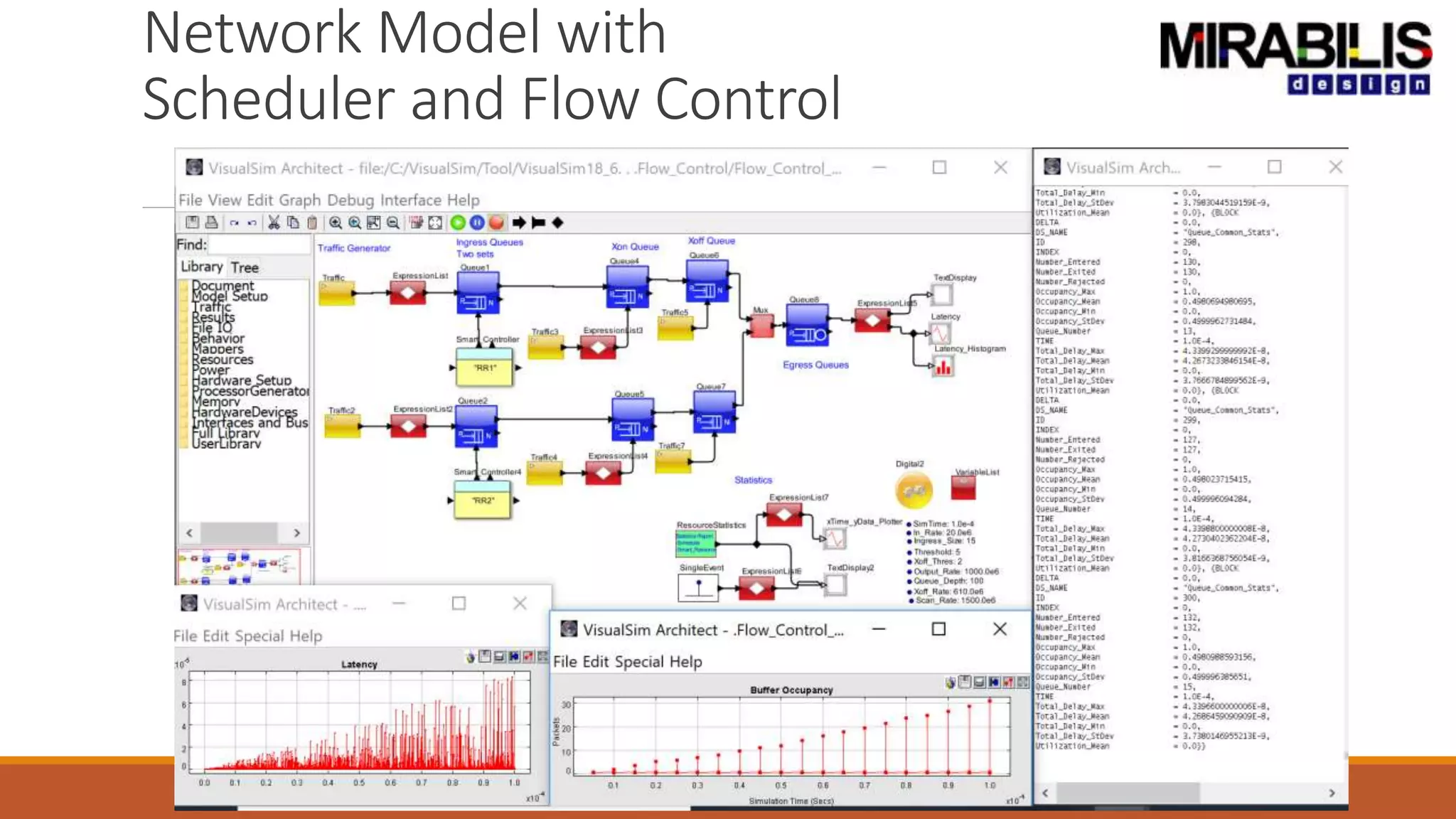

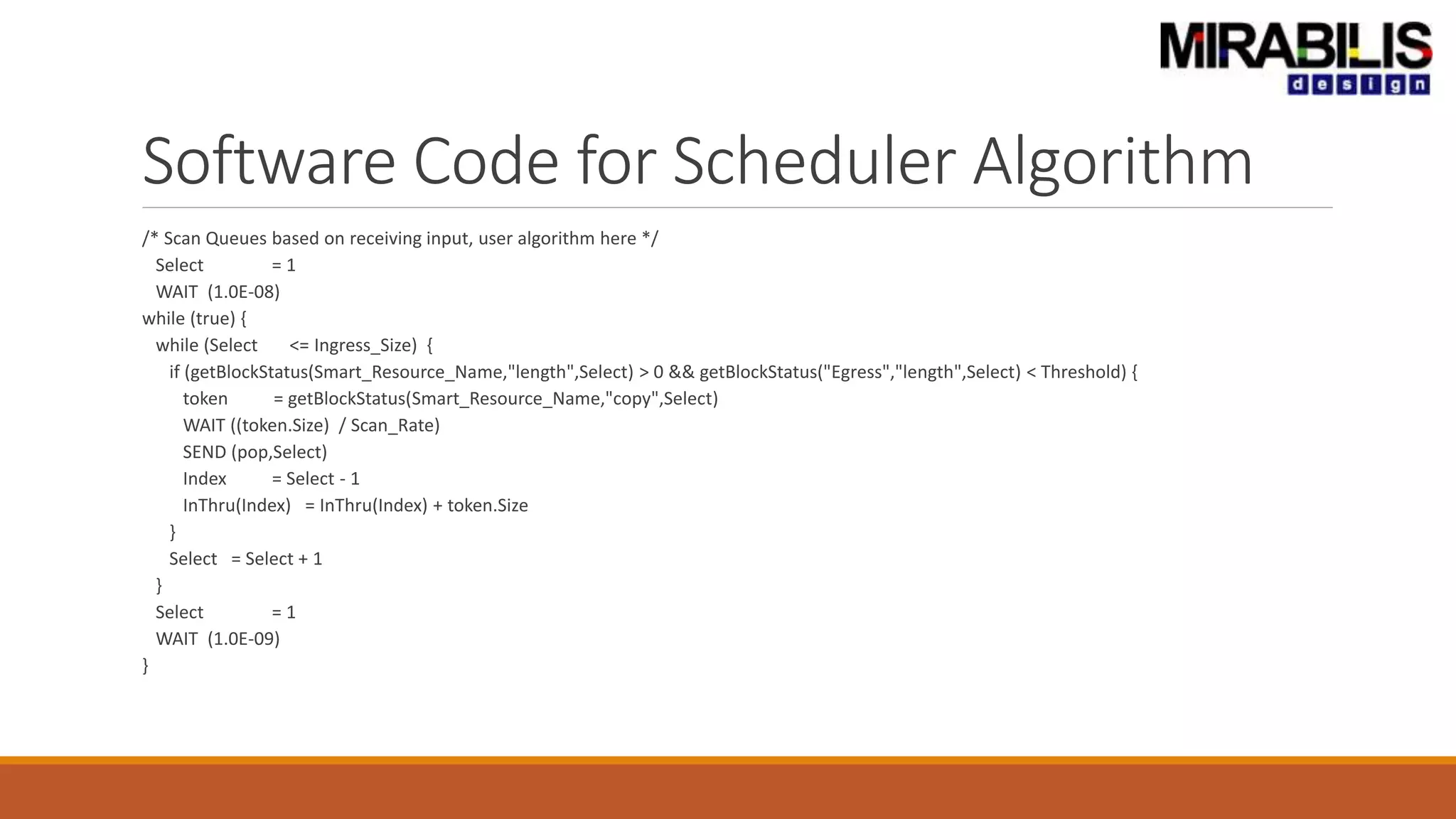

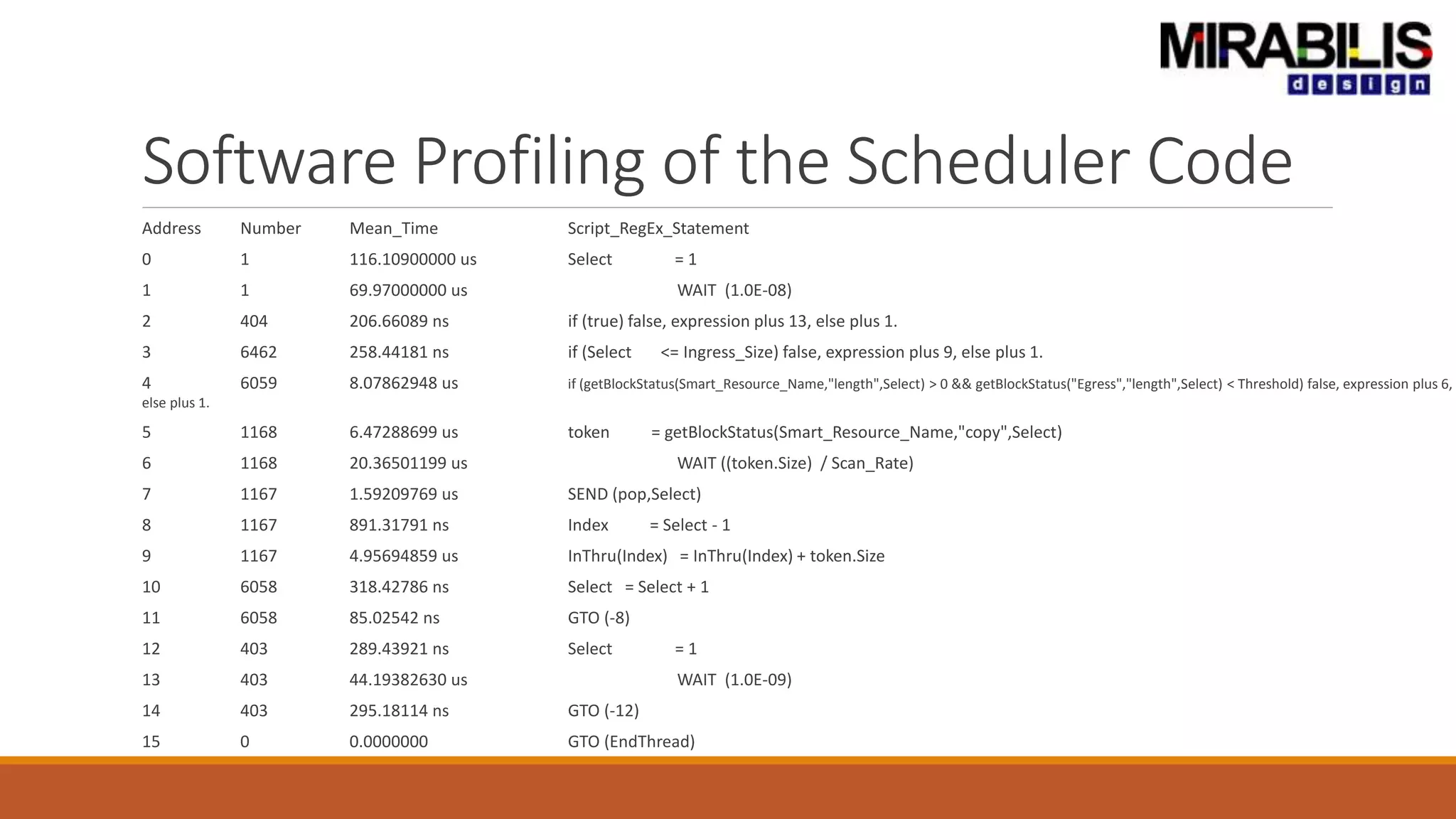

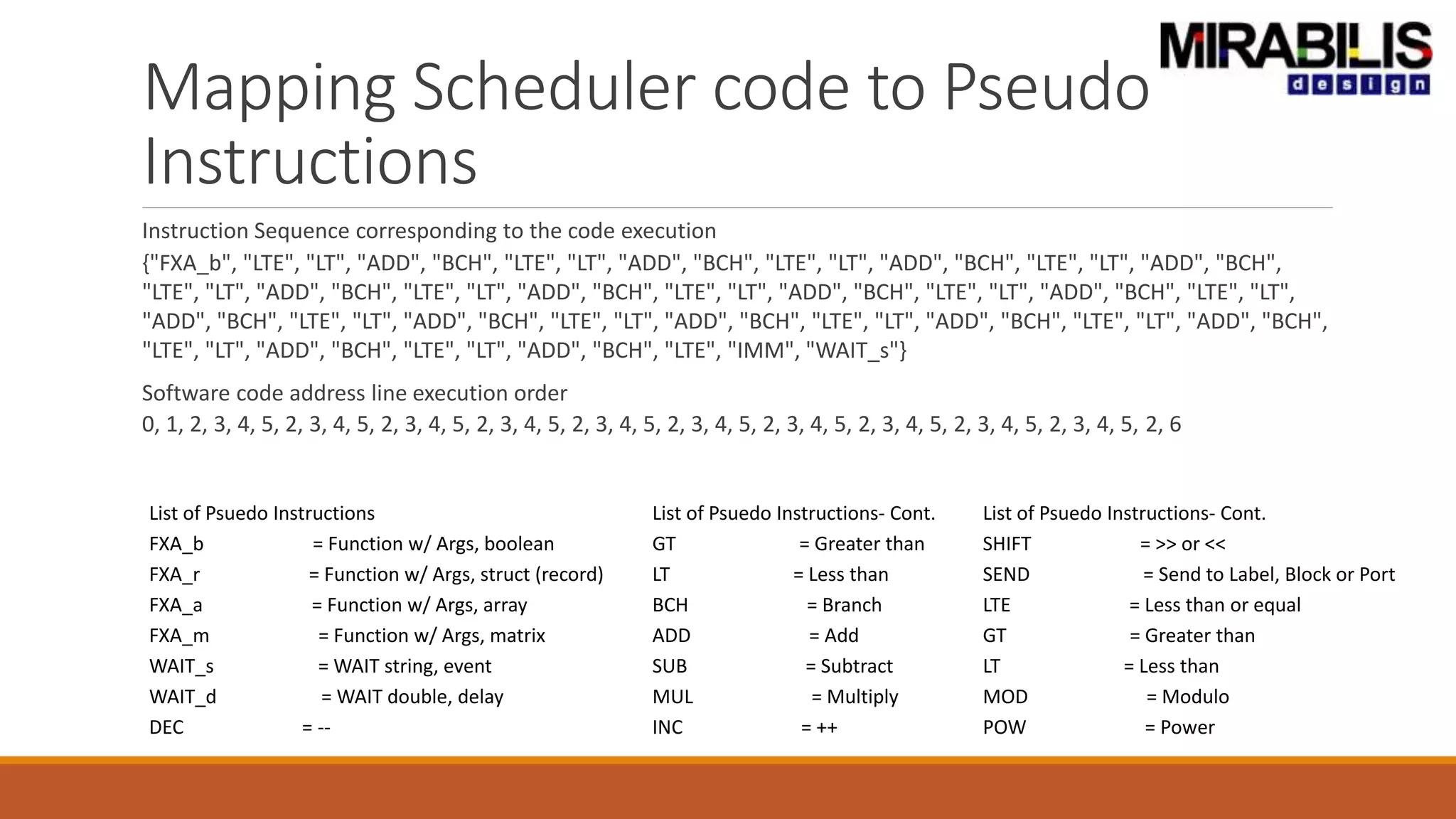

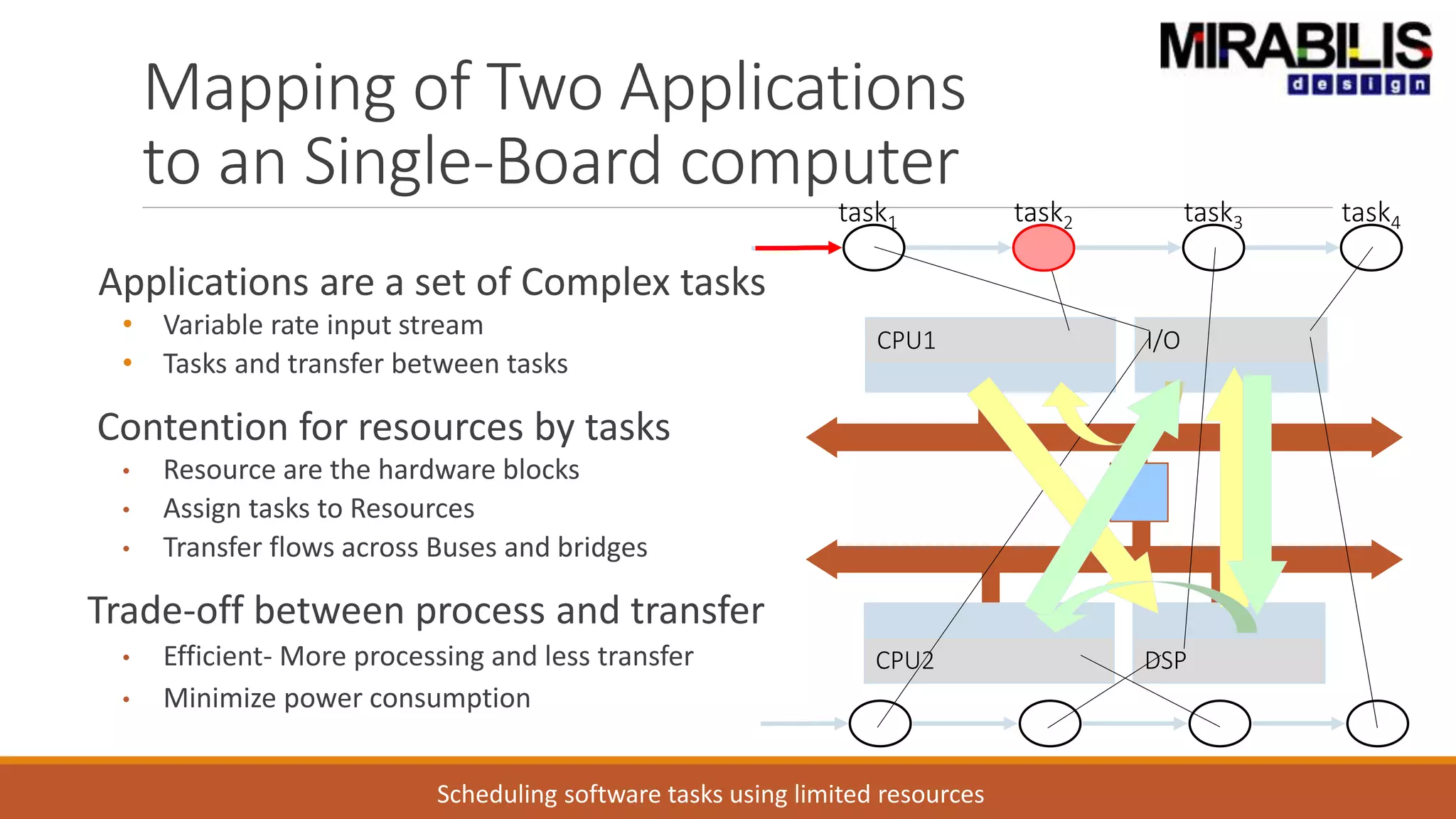

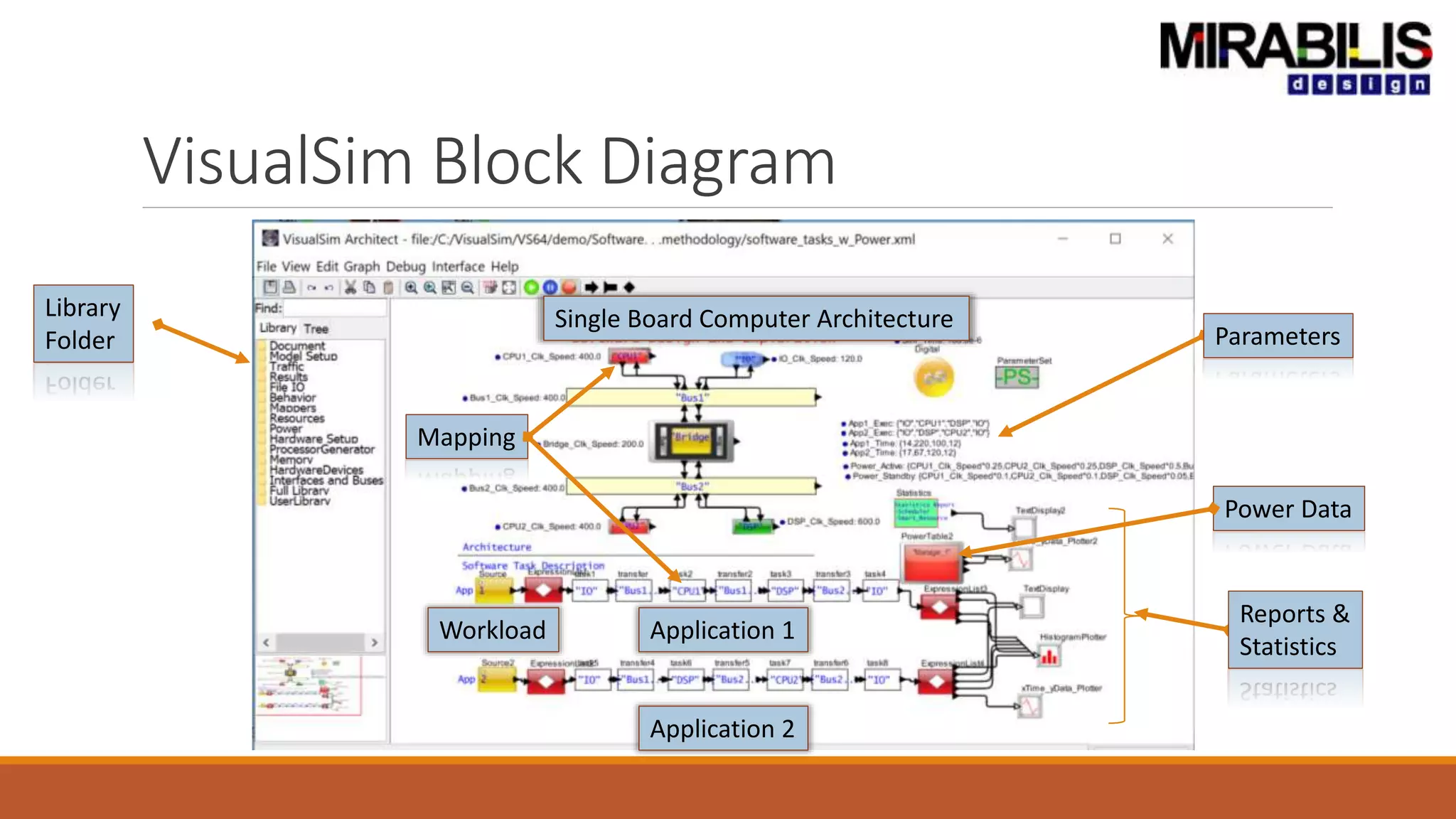

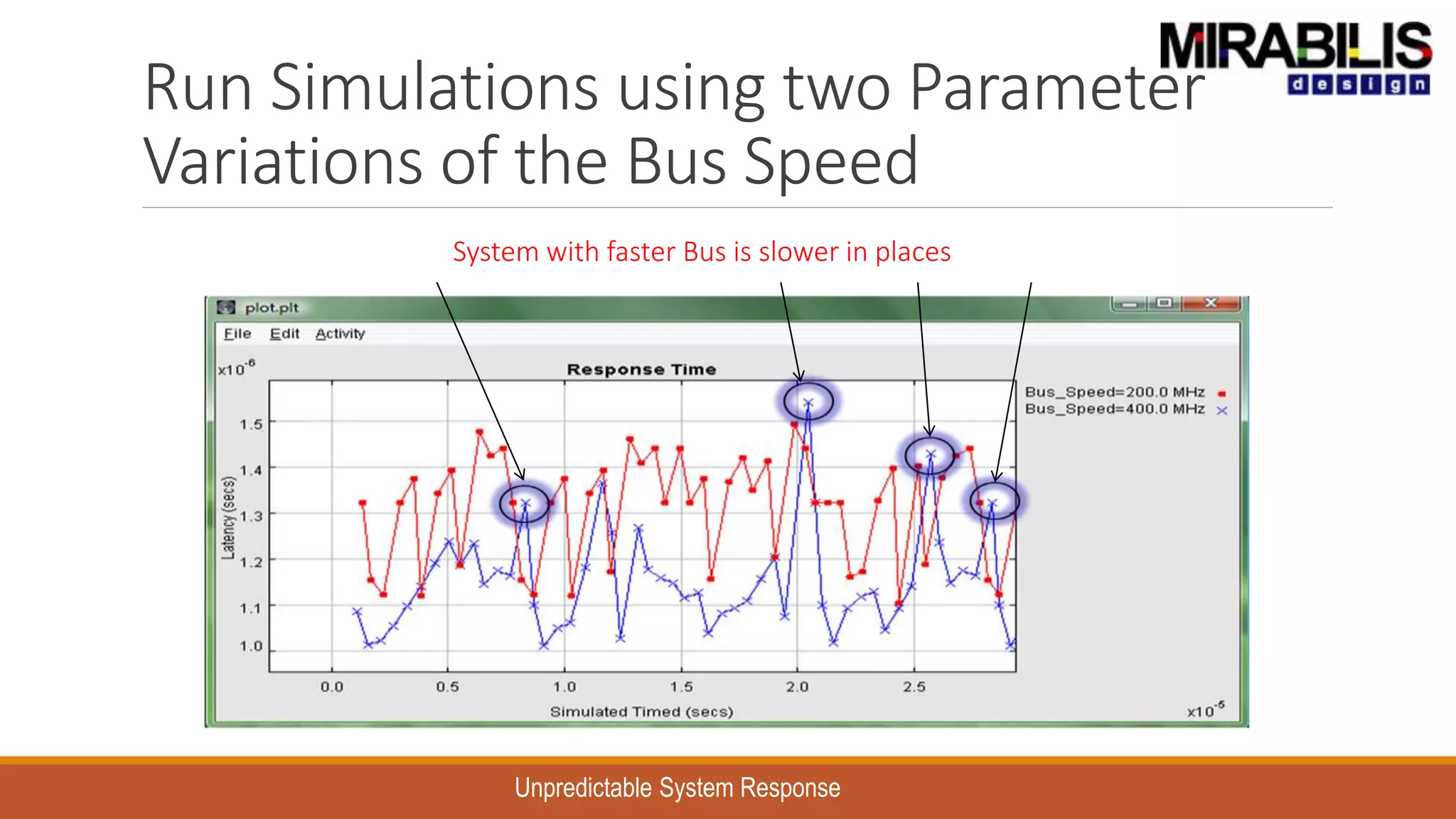

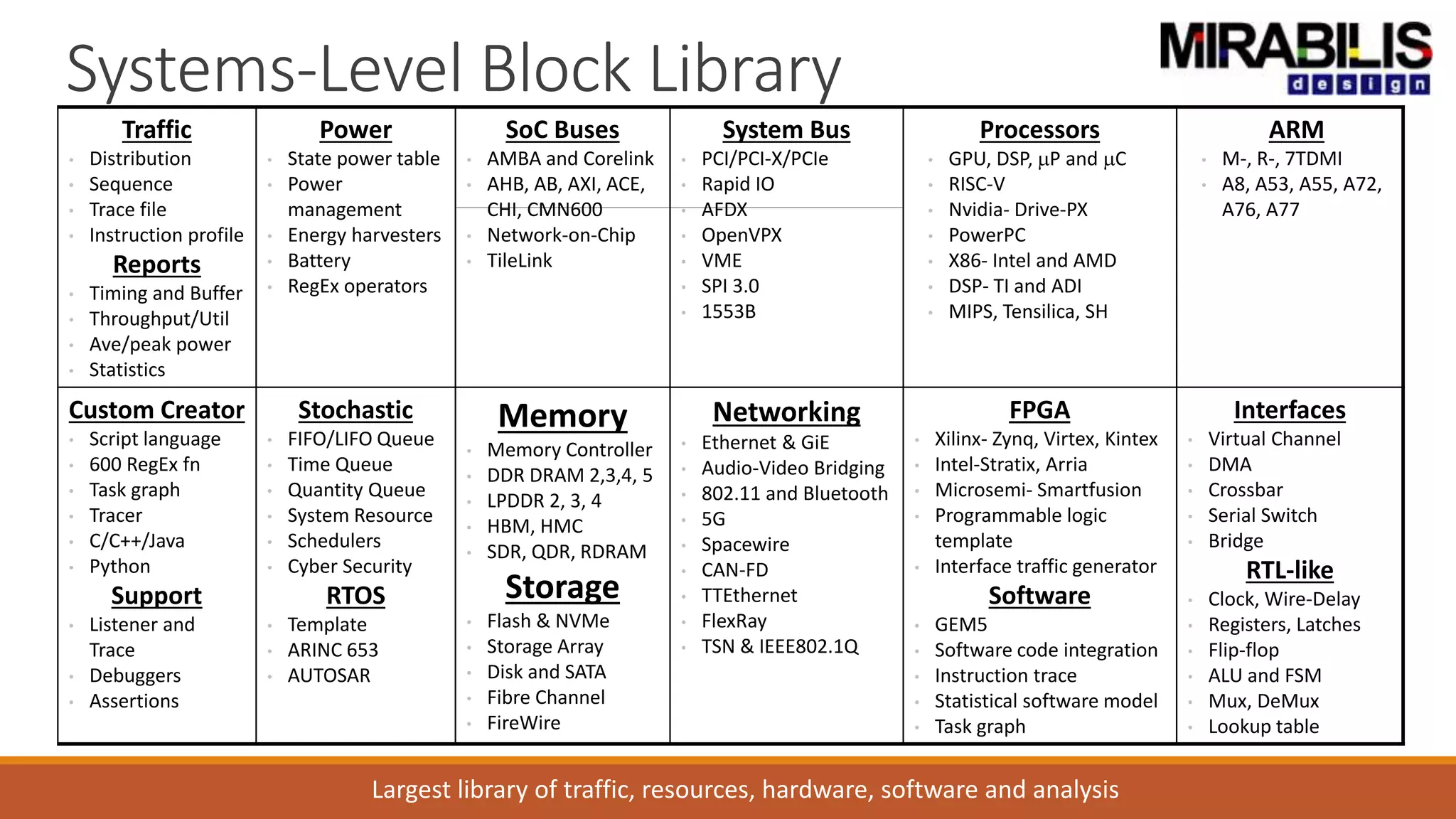

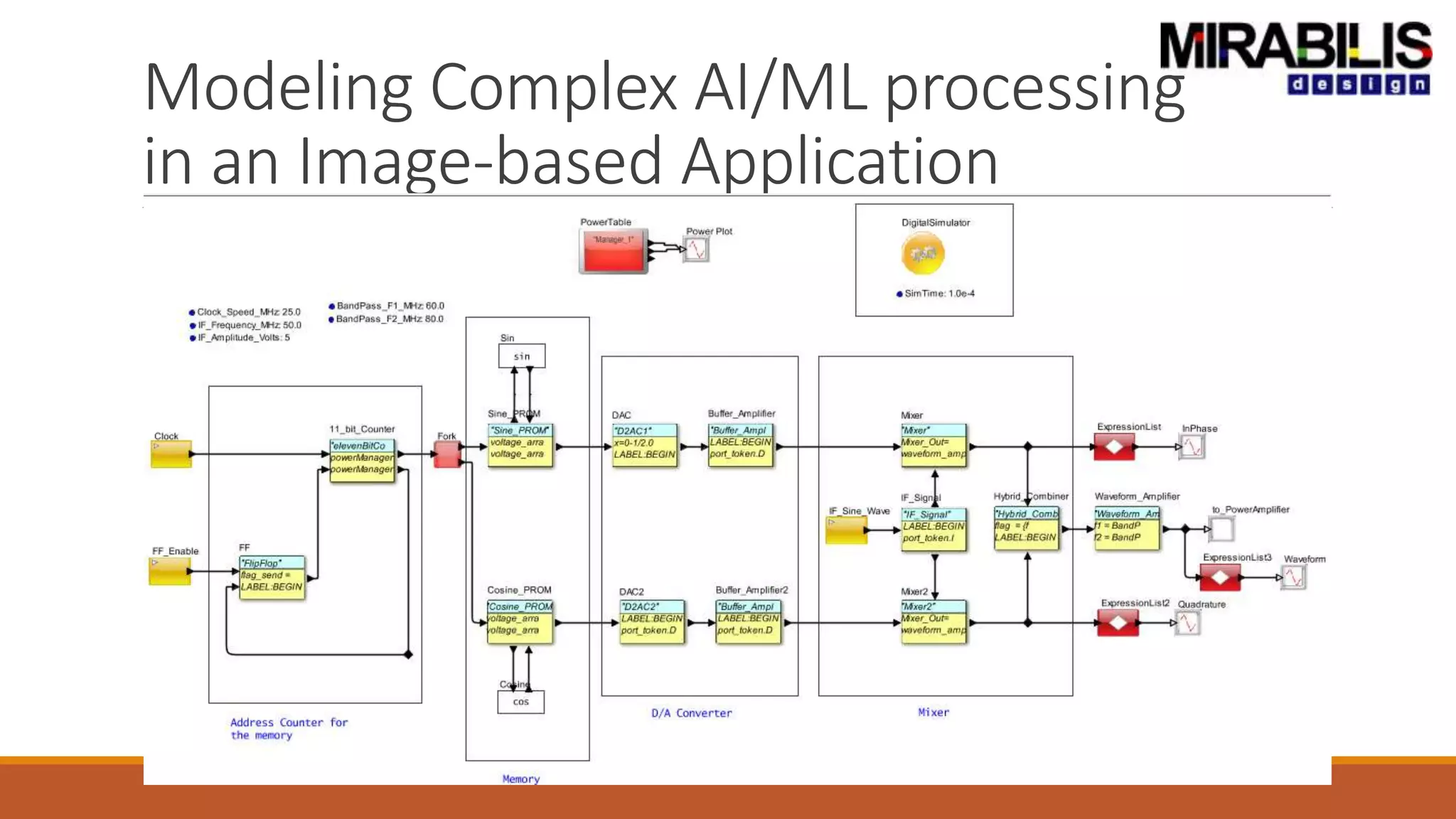

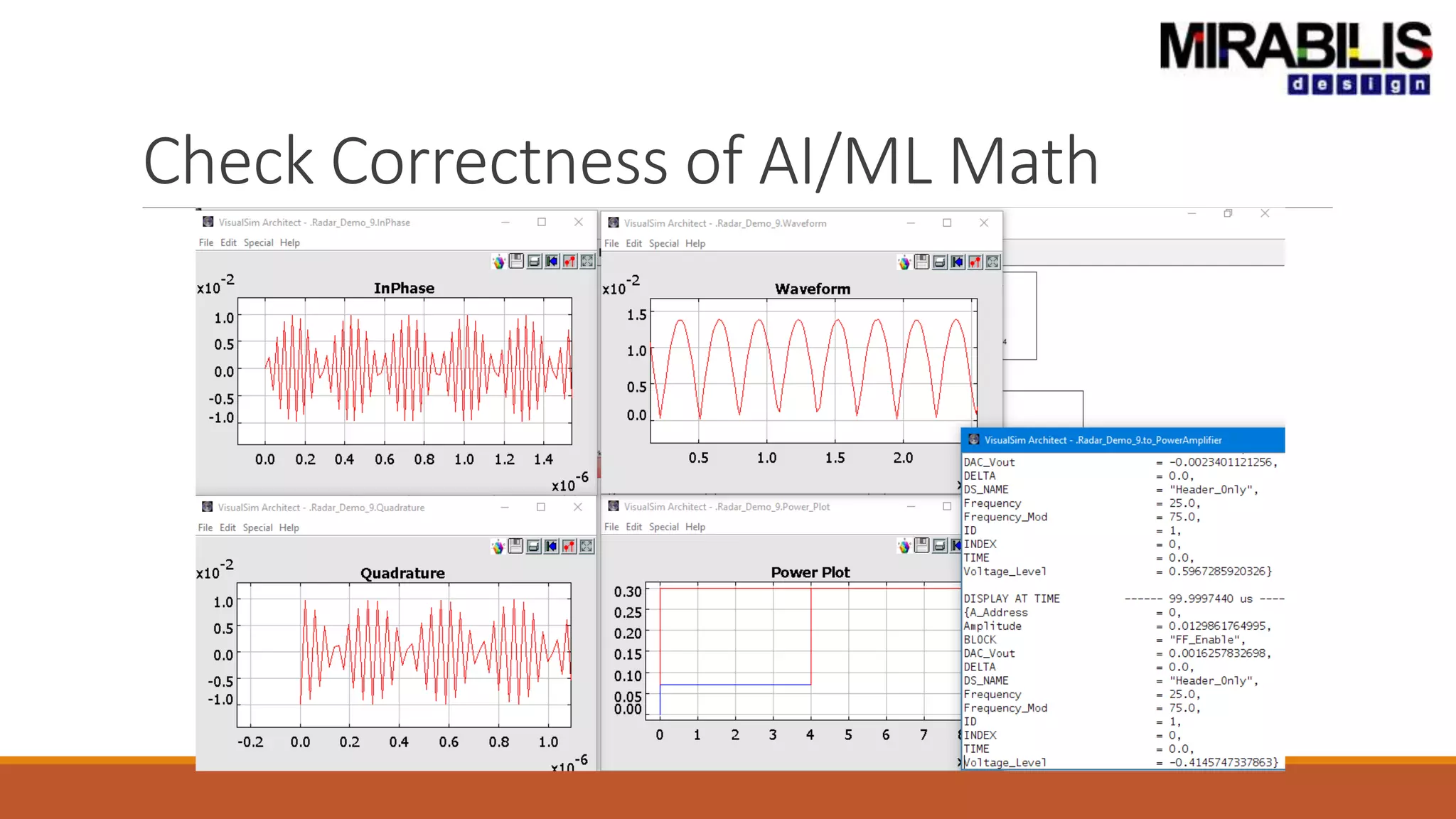

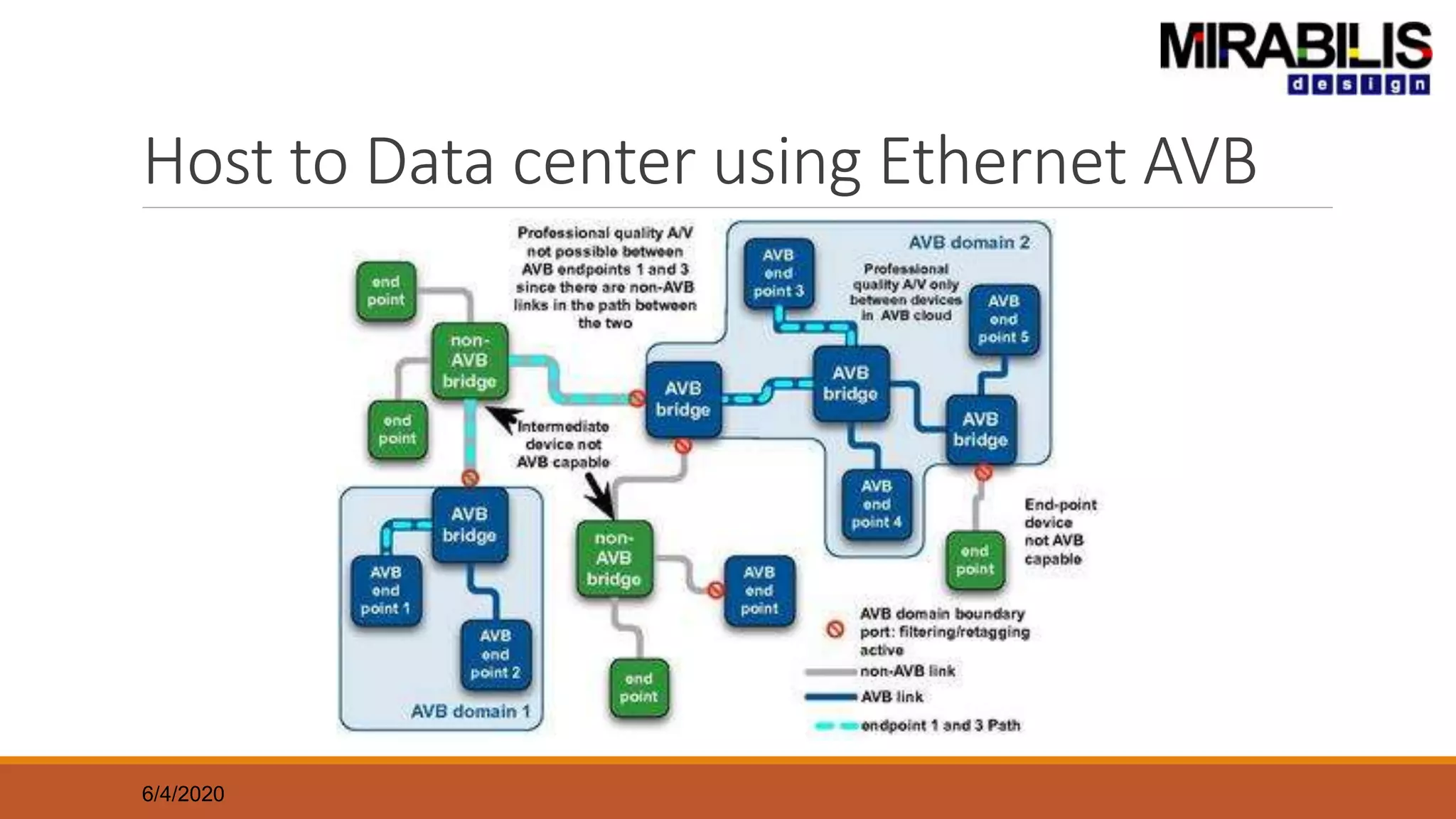

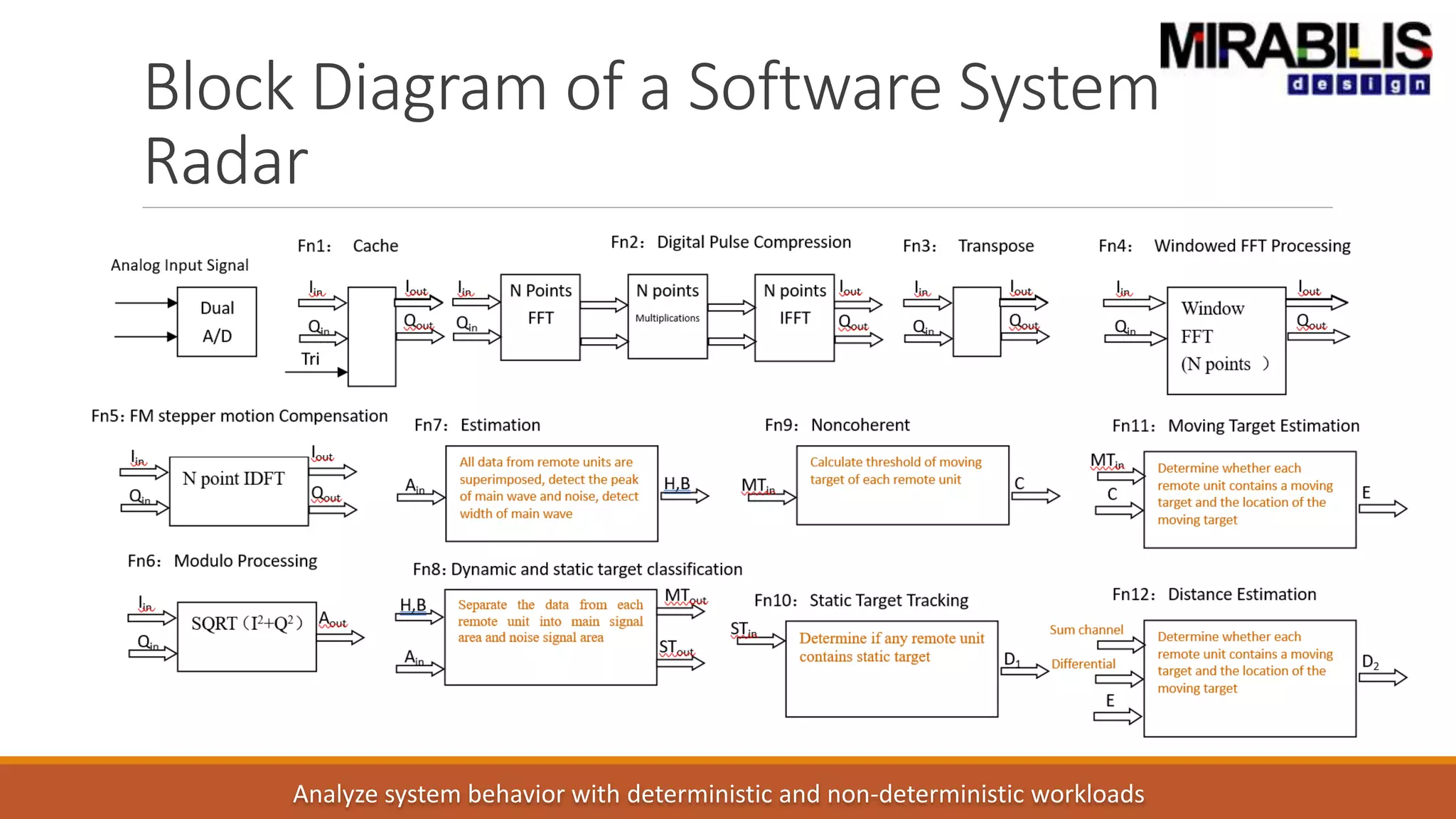

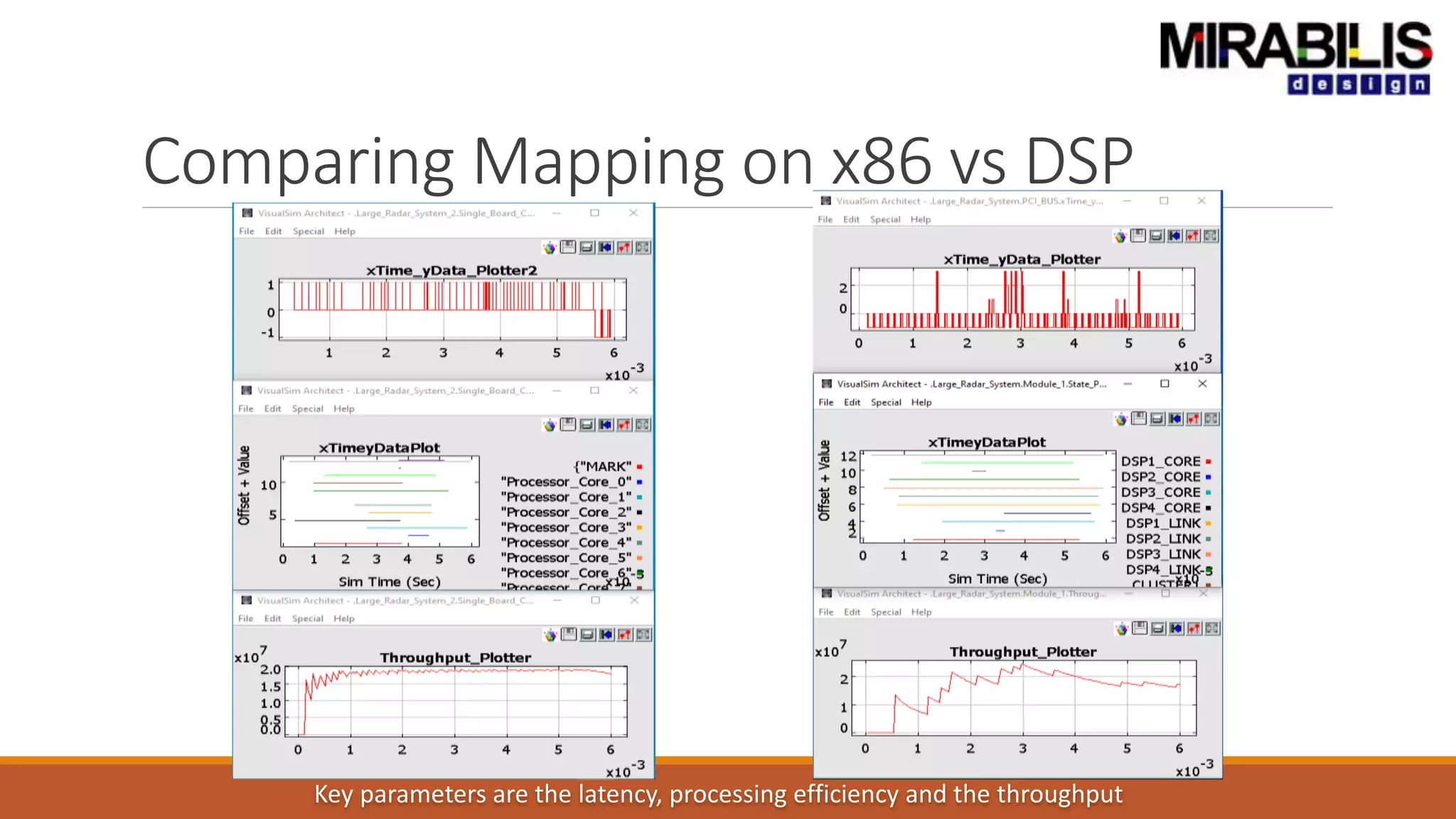

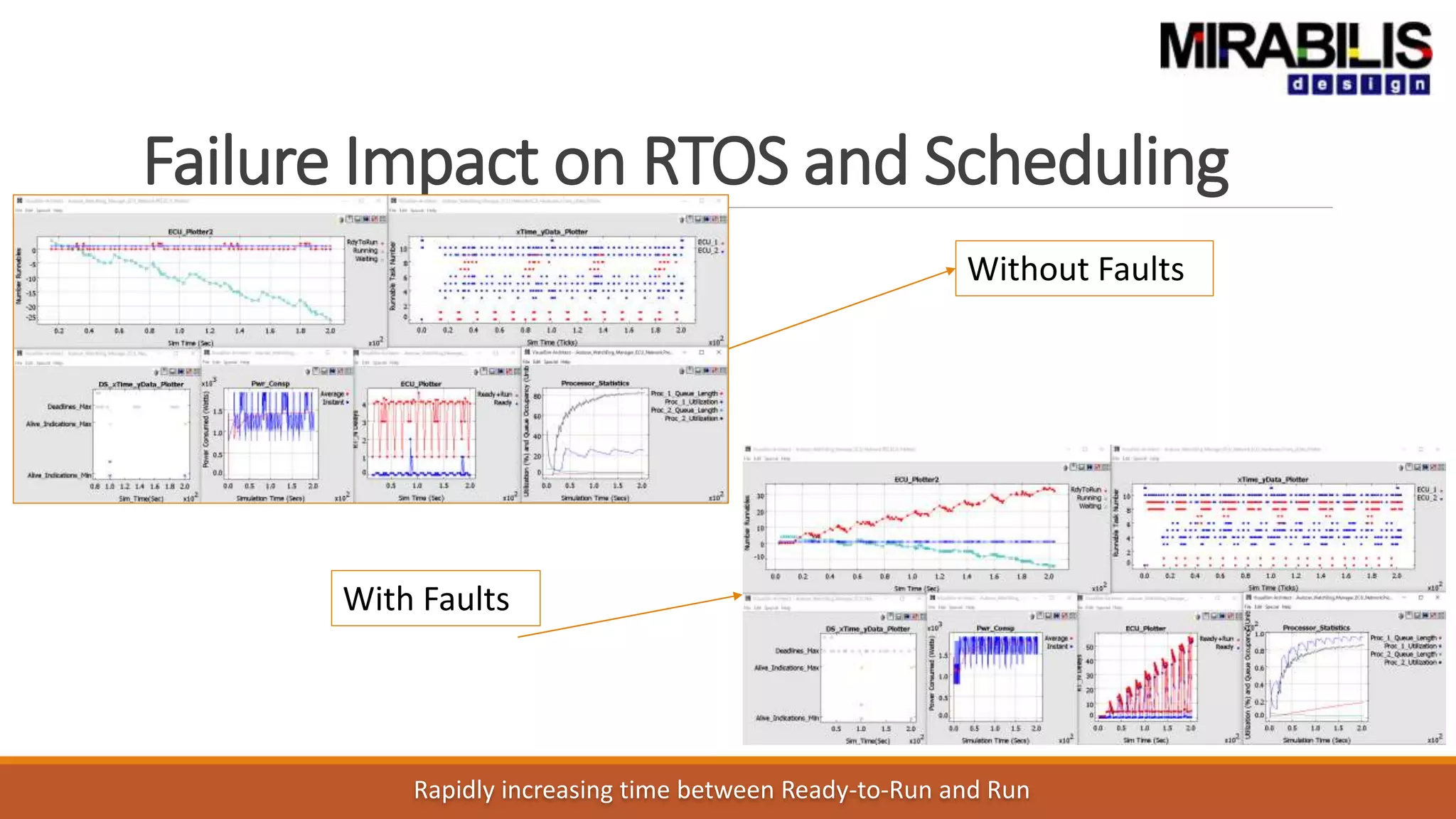

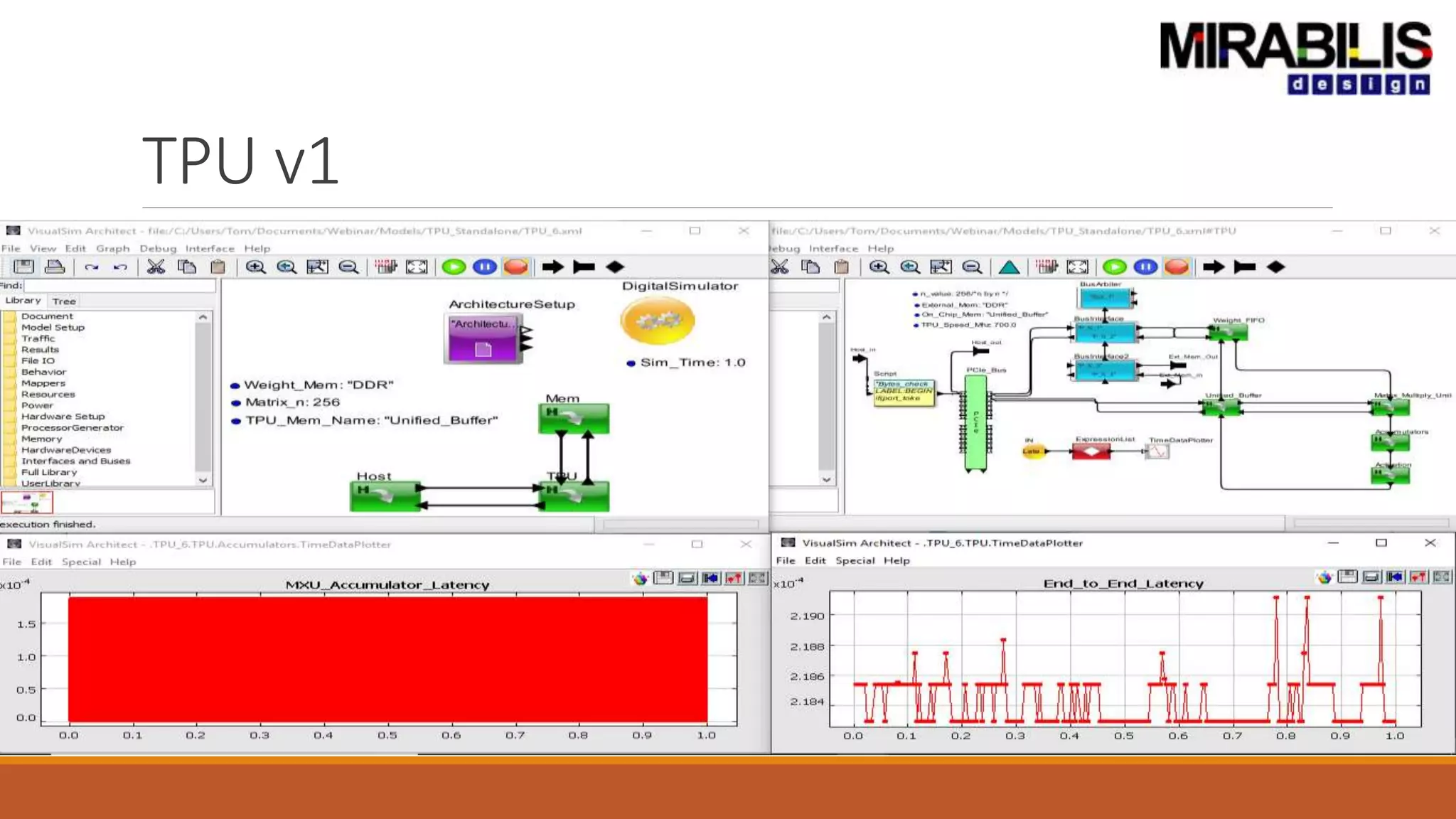

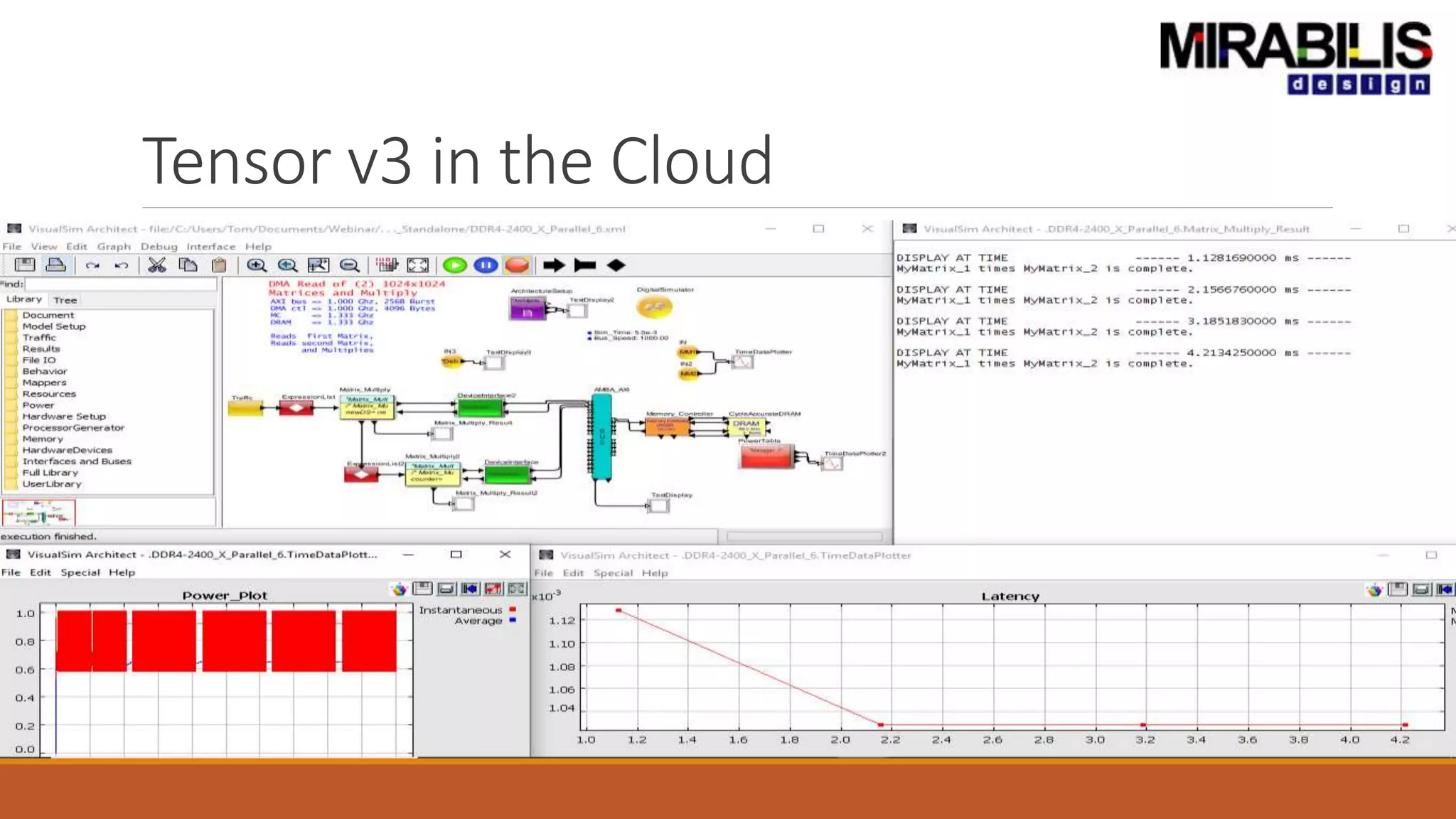

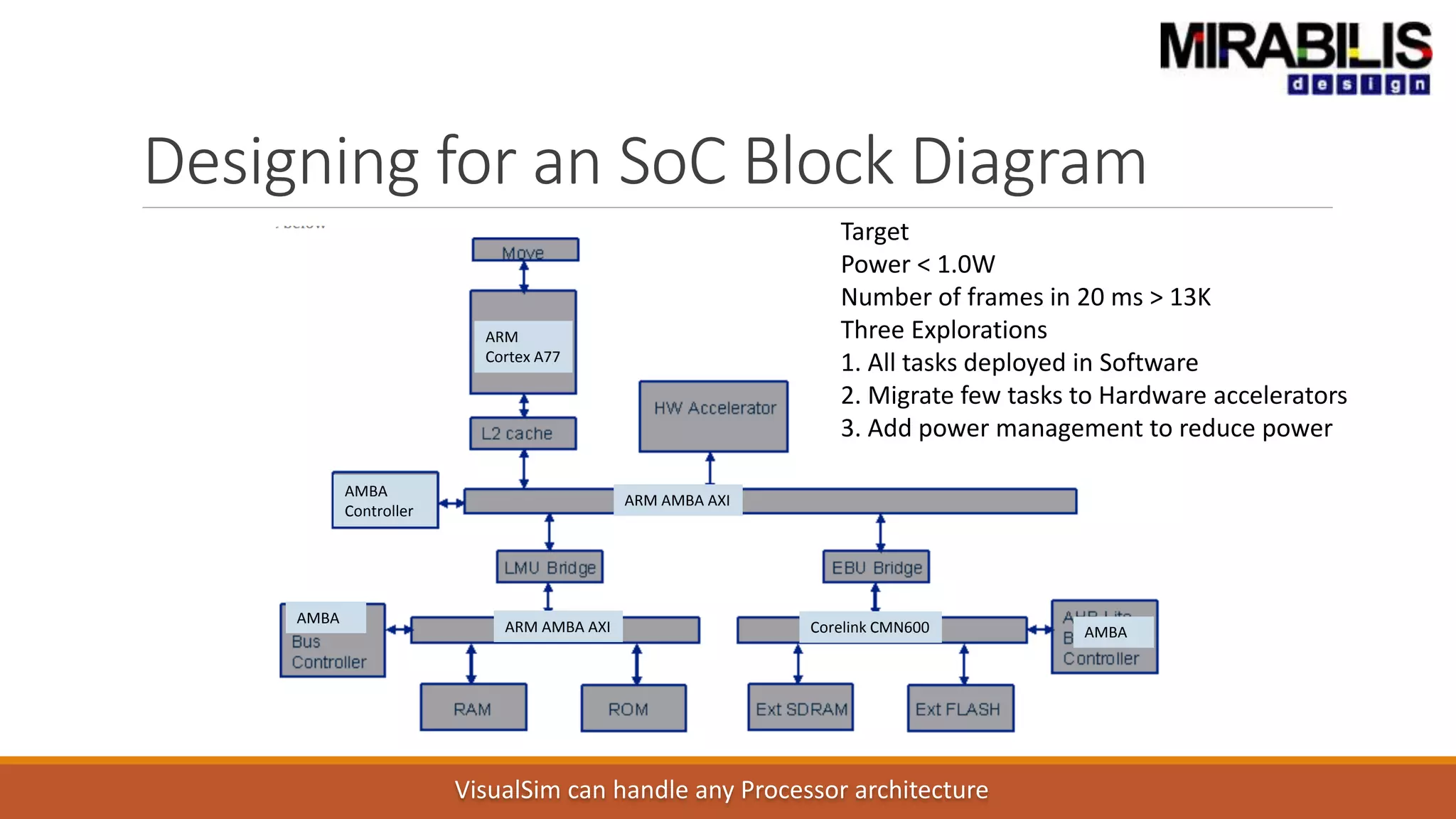

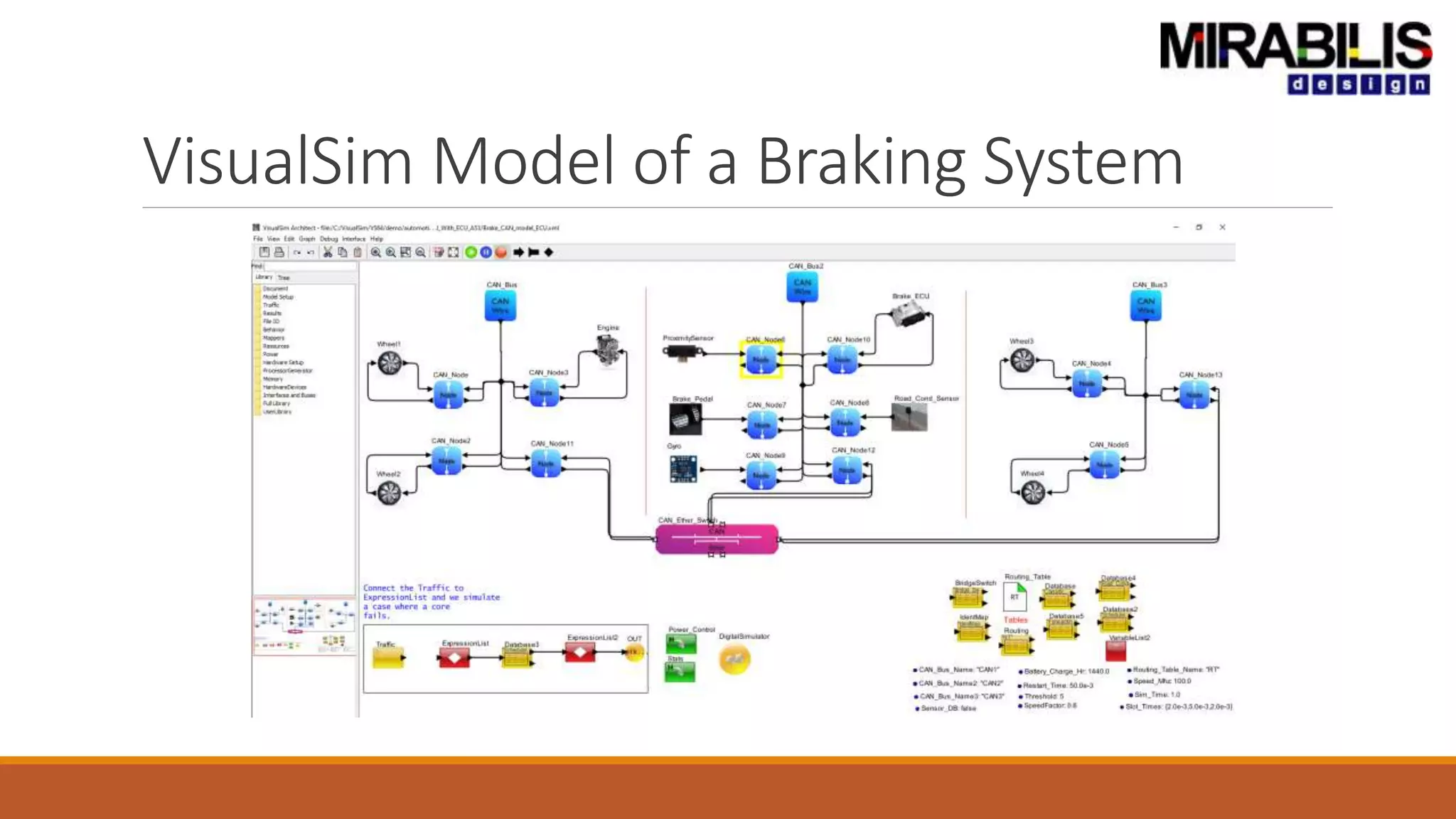

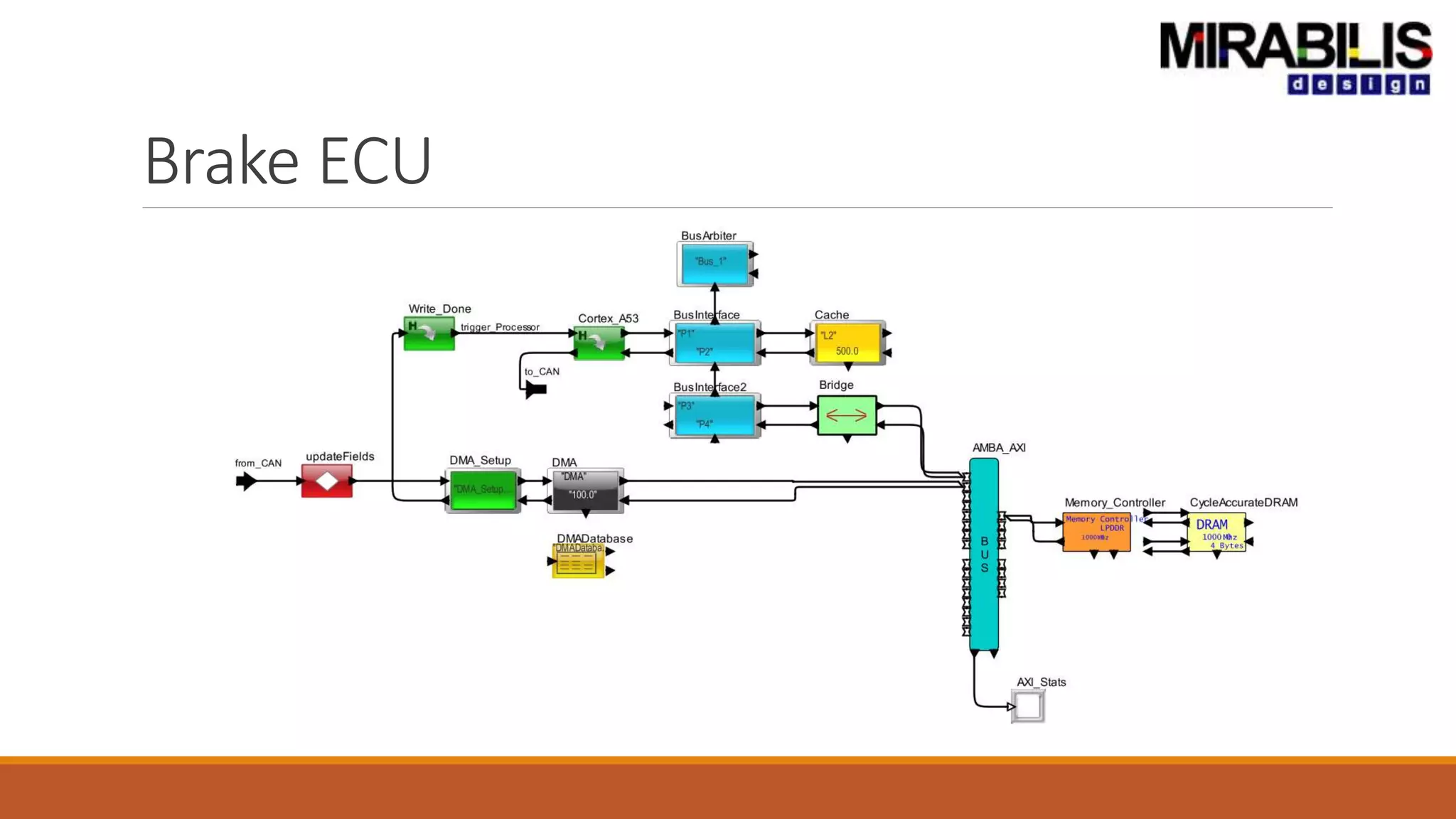

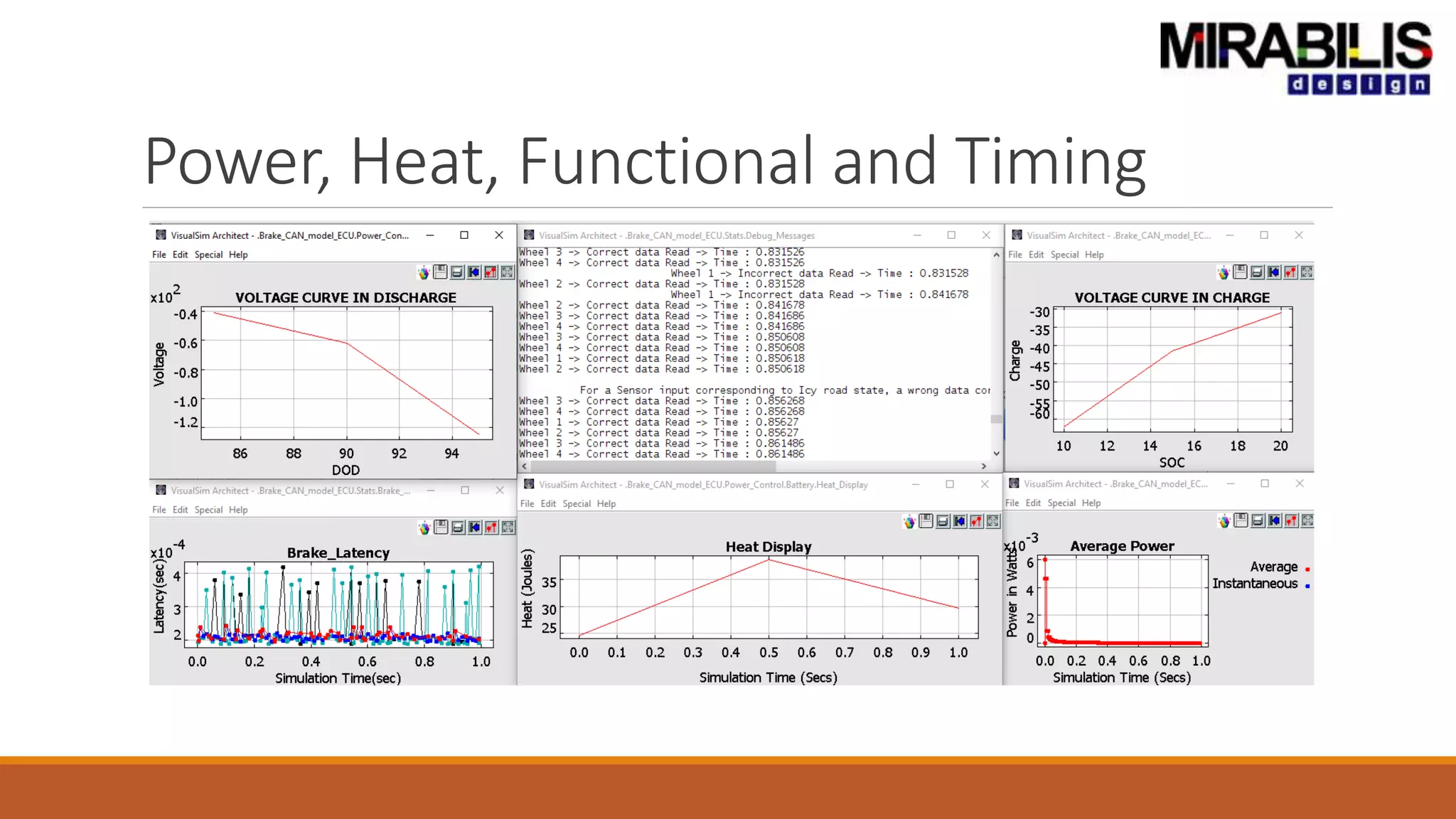

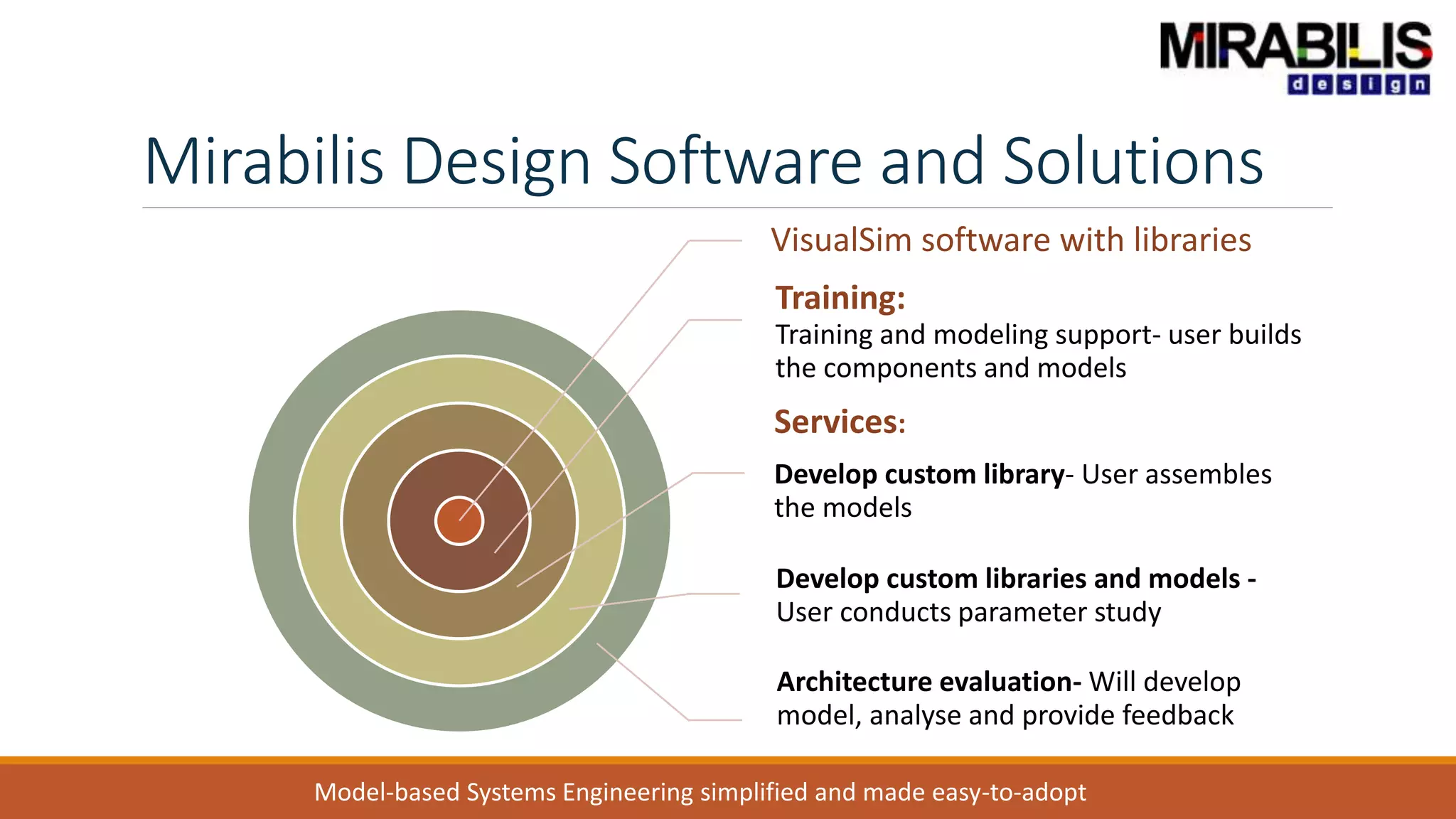

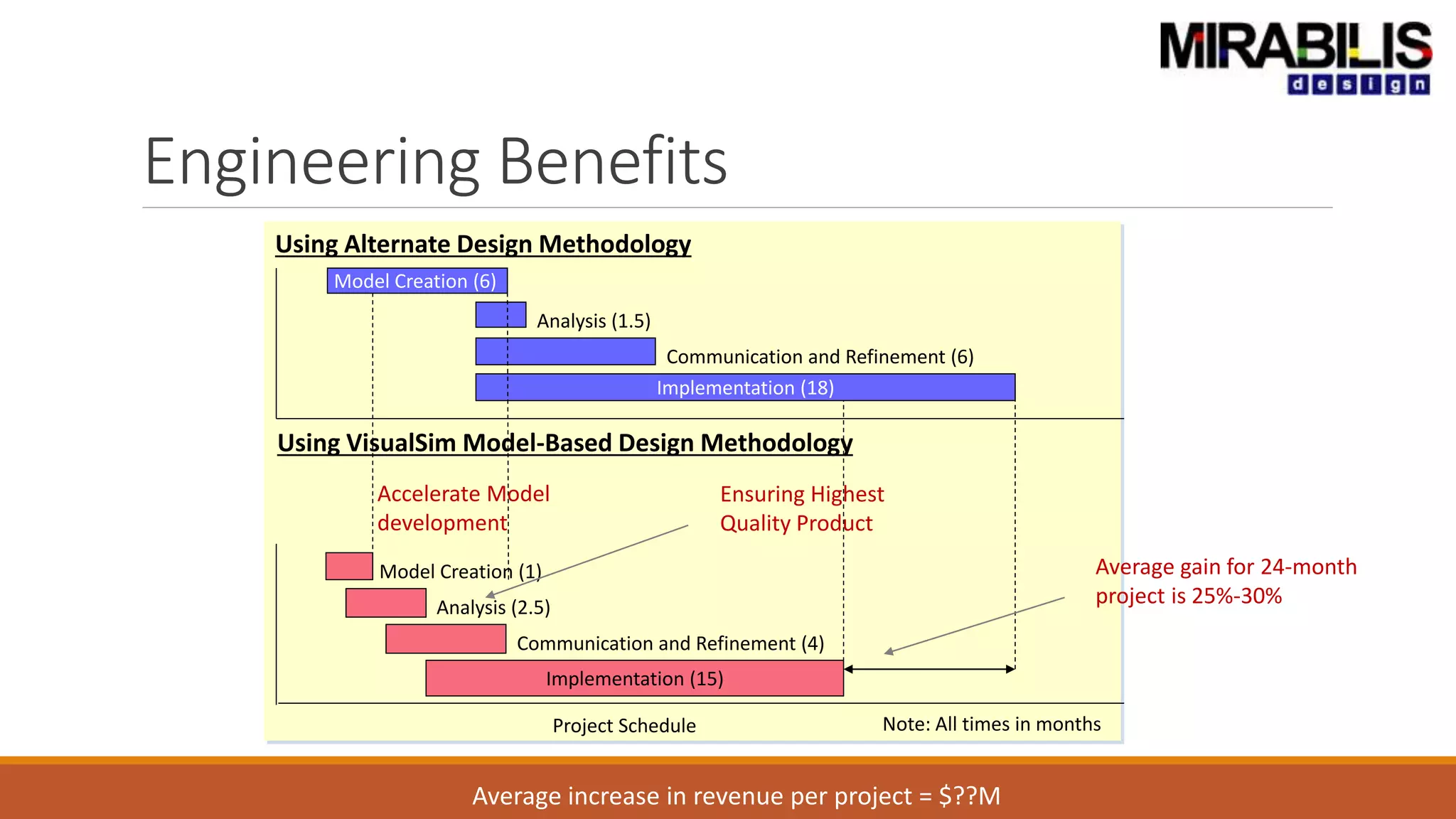

The document outlines a presentation by Deepak Shankar, the founder of Mirabilis Design Inc., focused on developing high-bandwidth and low-latency electronic systems for AI/ML applications. It covers traditional vs. proposed approaches to system modeling, emphasizing the use of virtual prototypes and early trade-off analysis to enhance design efficiency and accuracy. Additional topics include software performance profiling, hardware-software selection, and the capabilities of VisualSim modeling software in managing complex electronic system challenges.