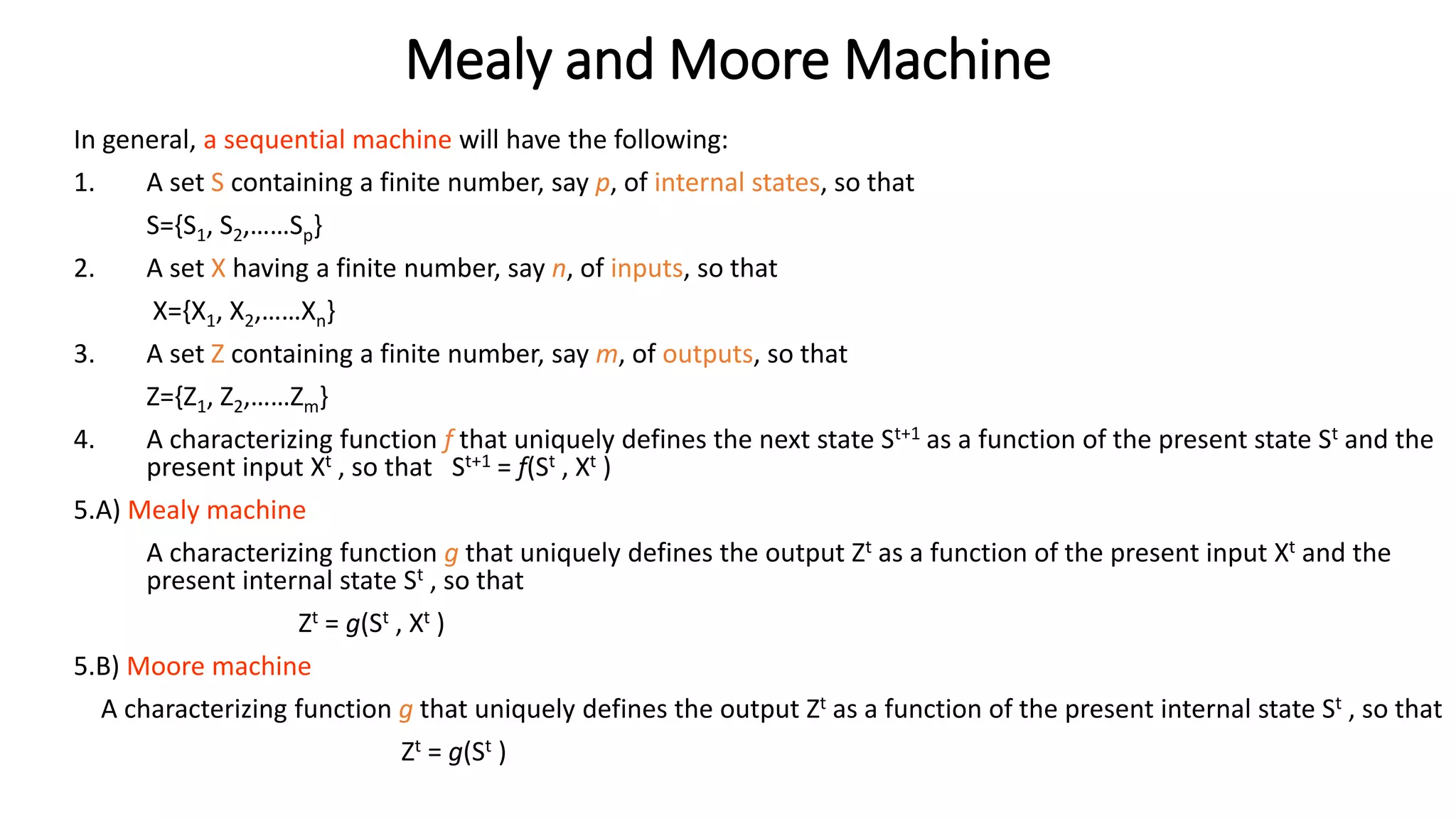

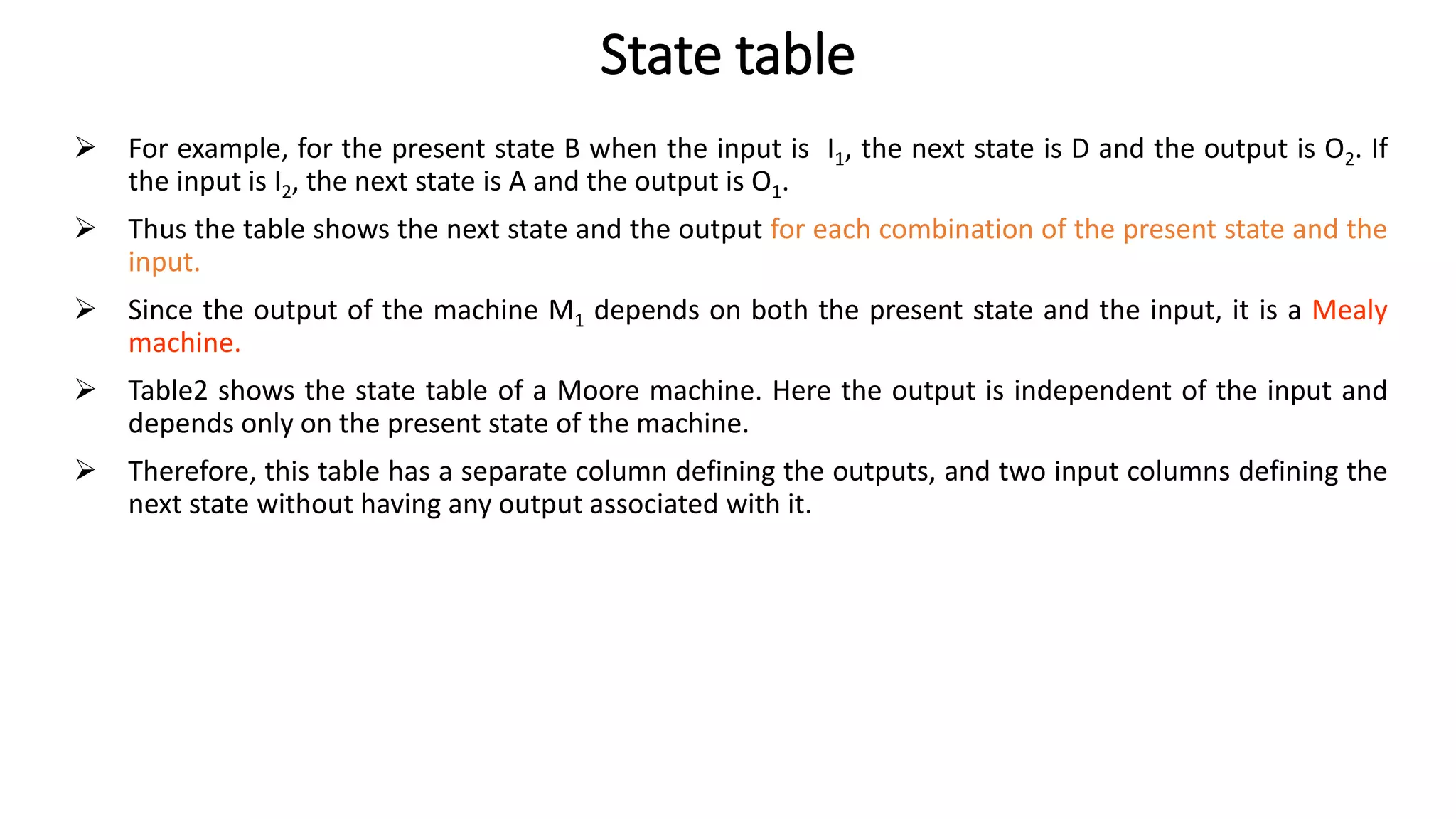

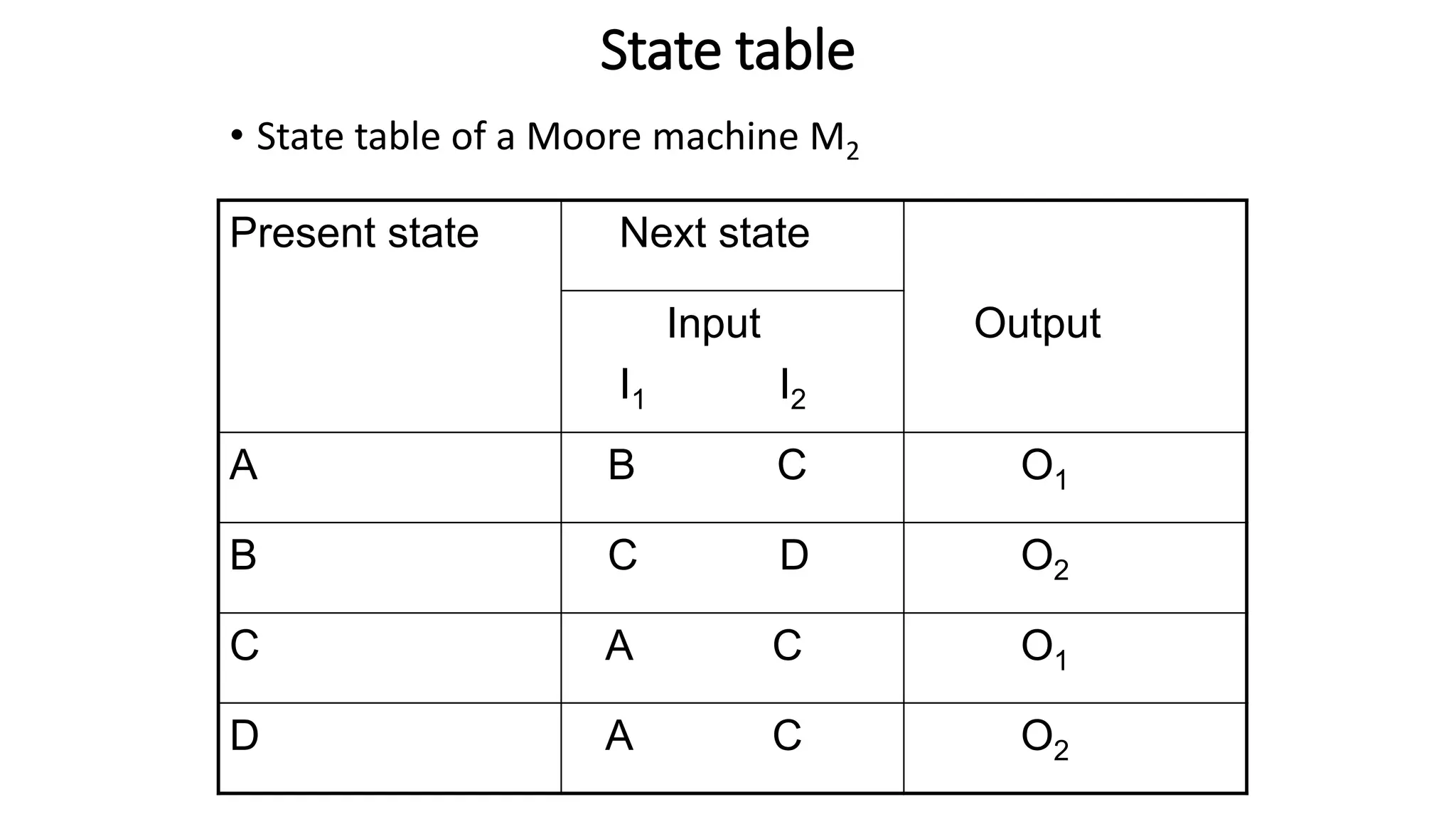

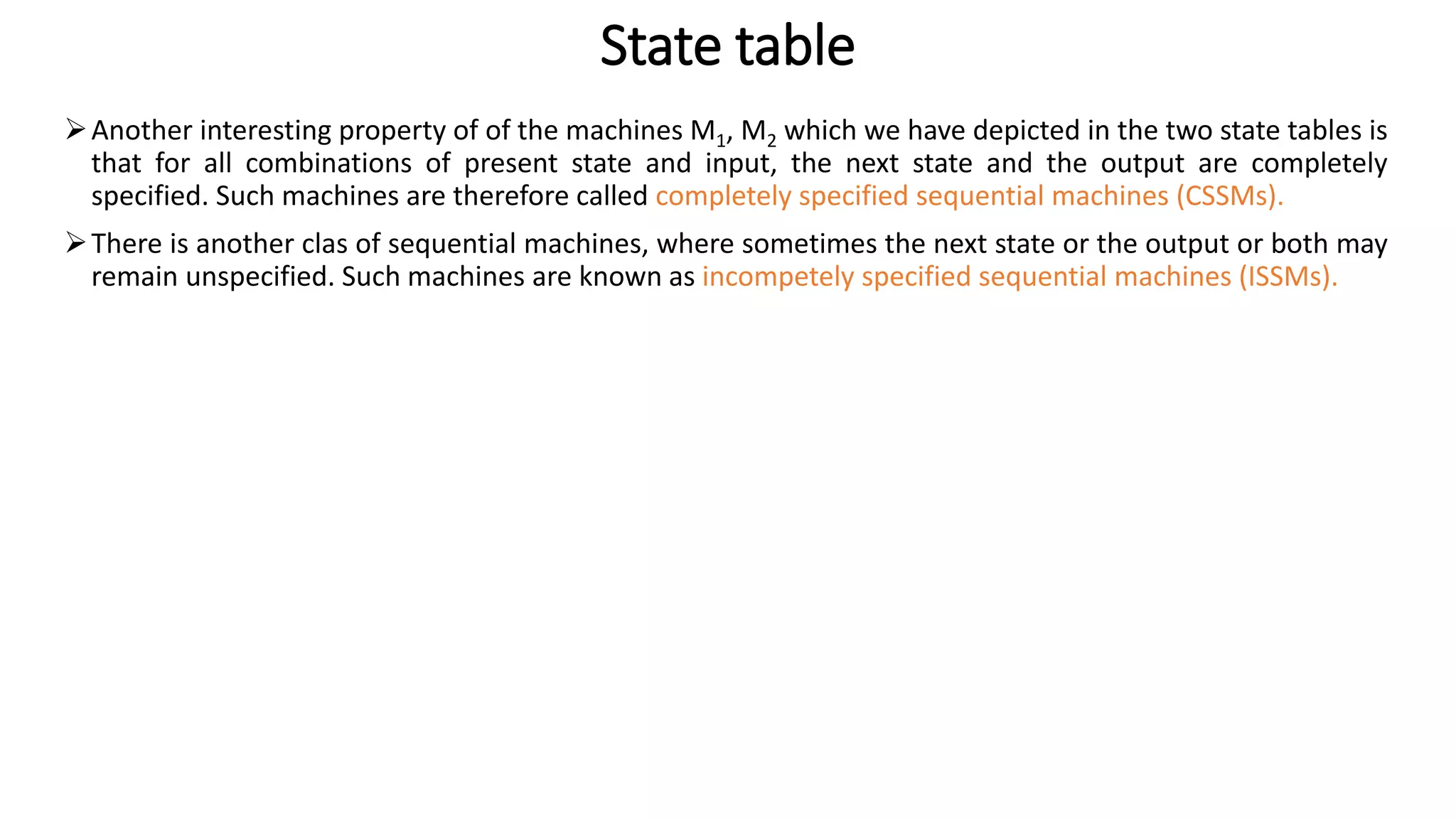

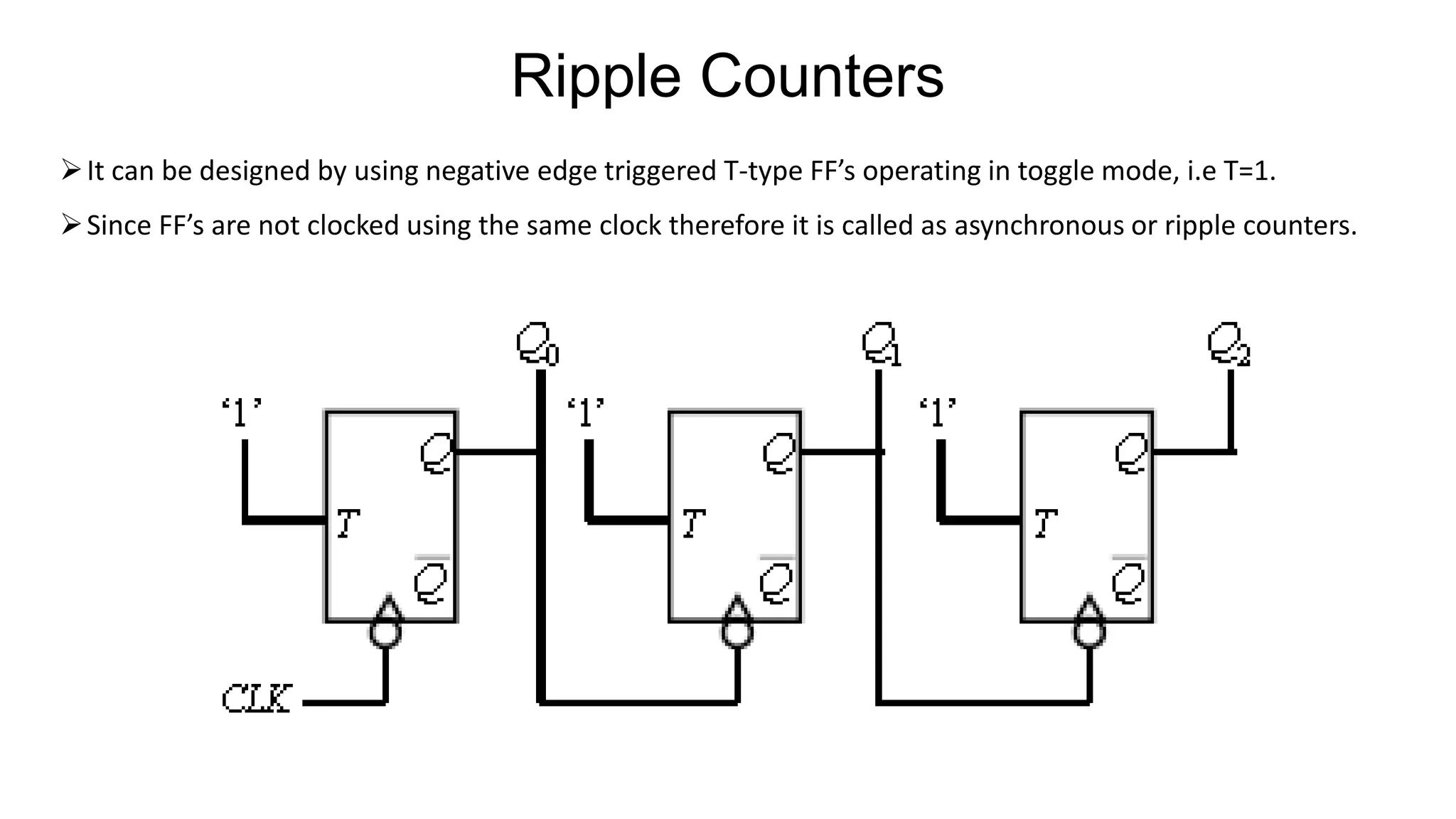

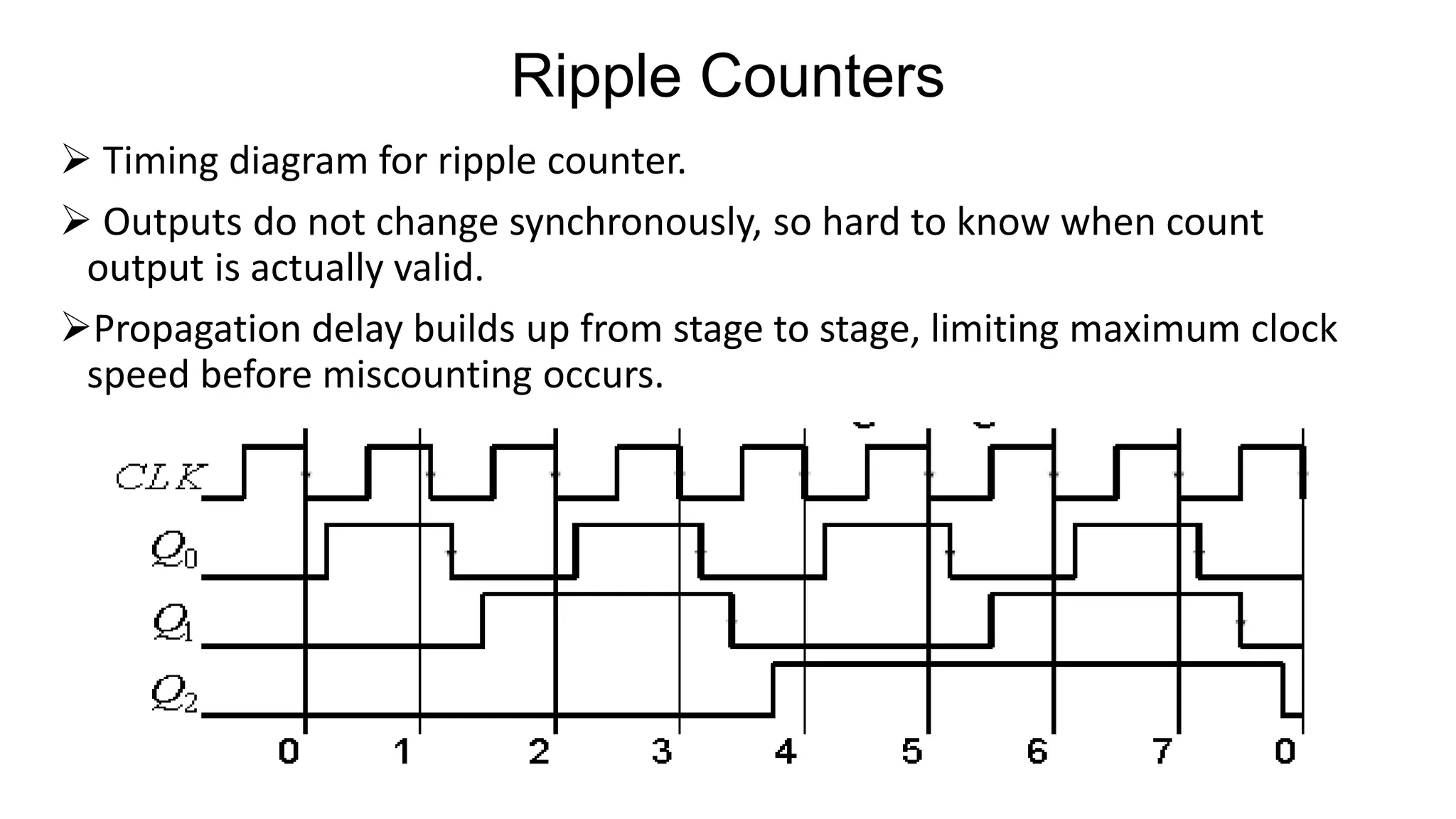

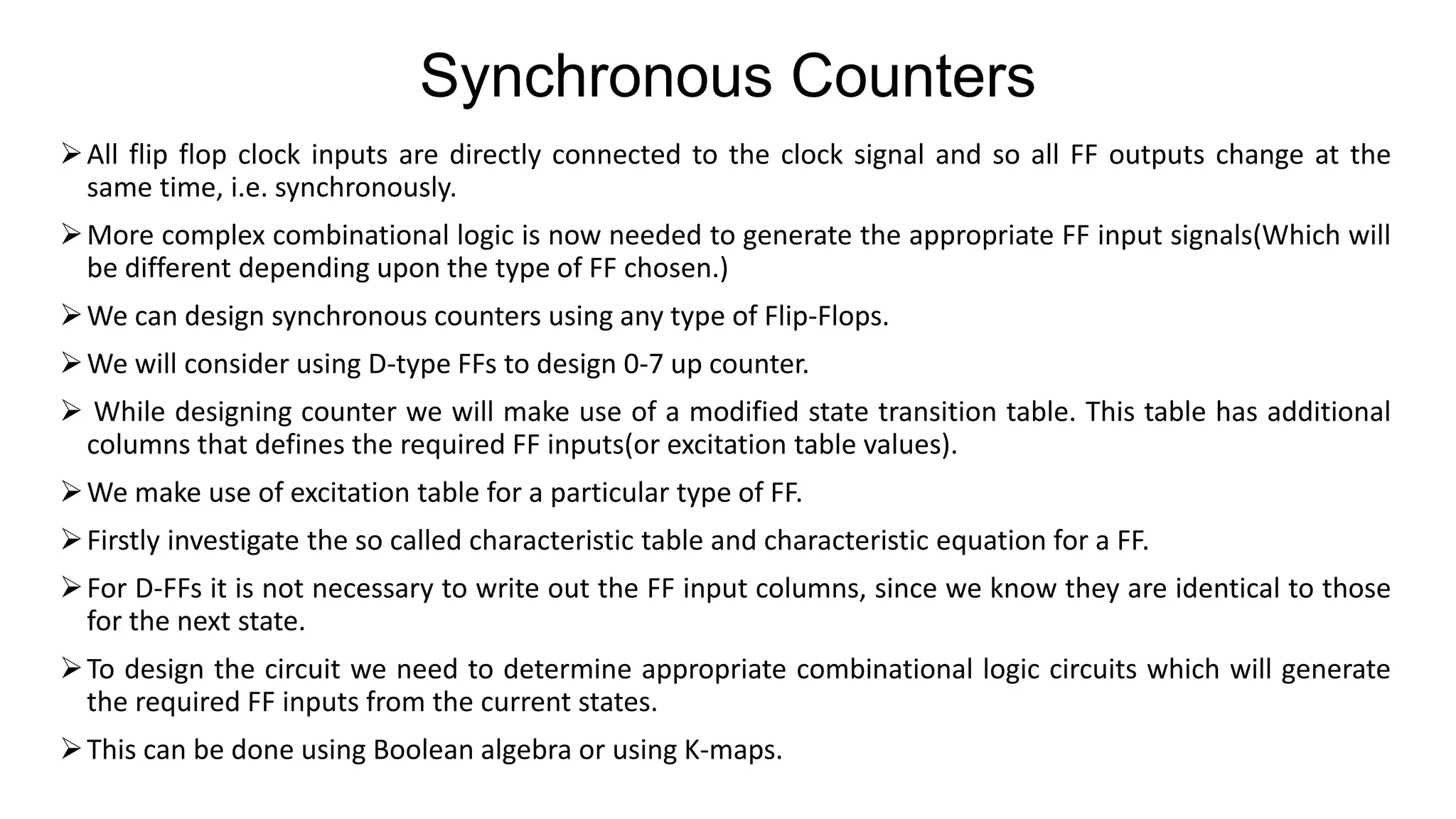

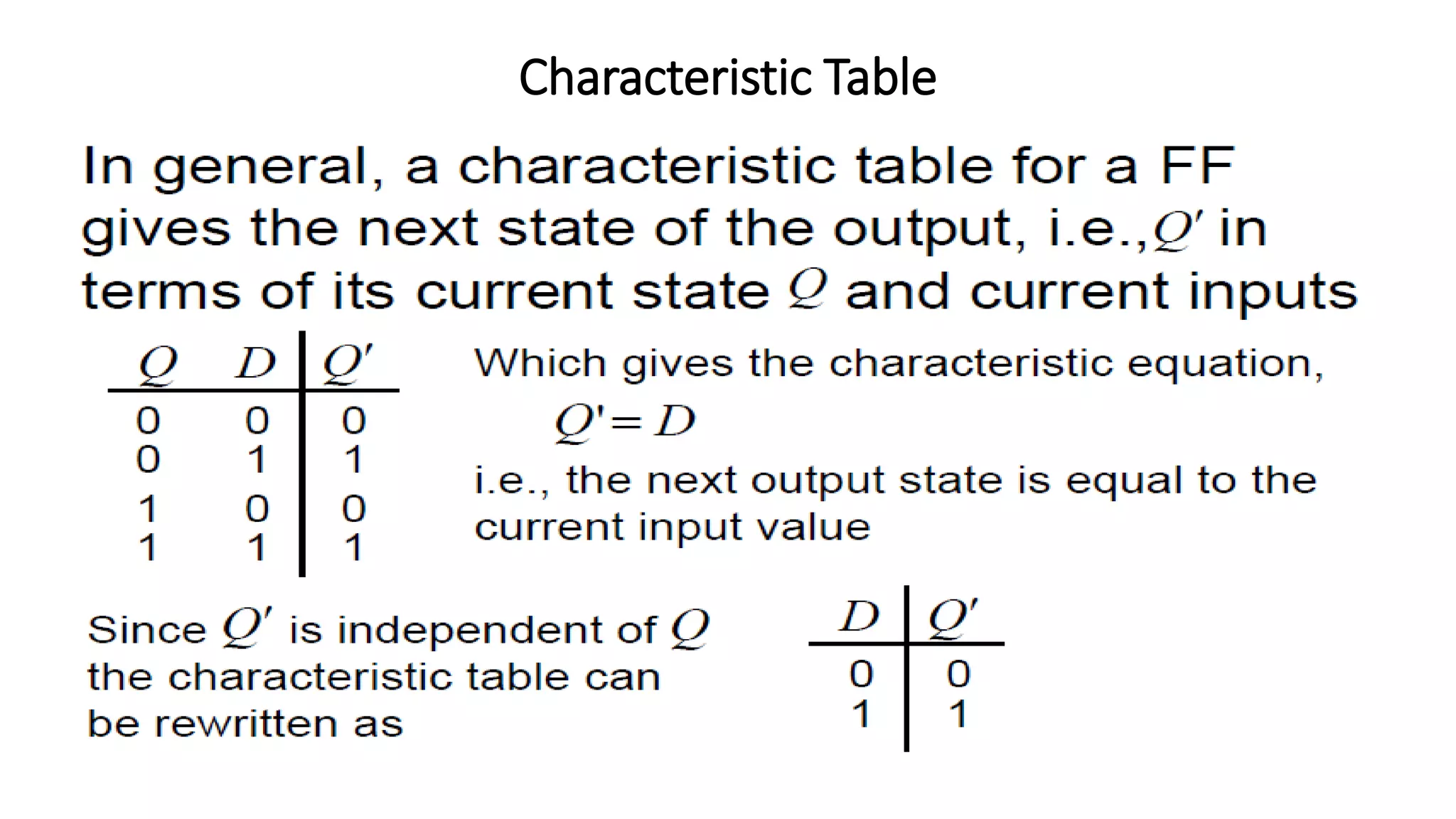

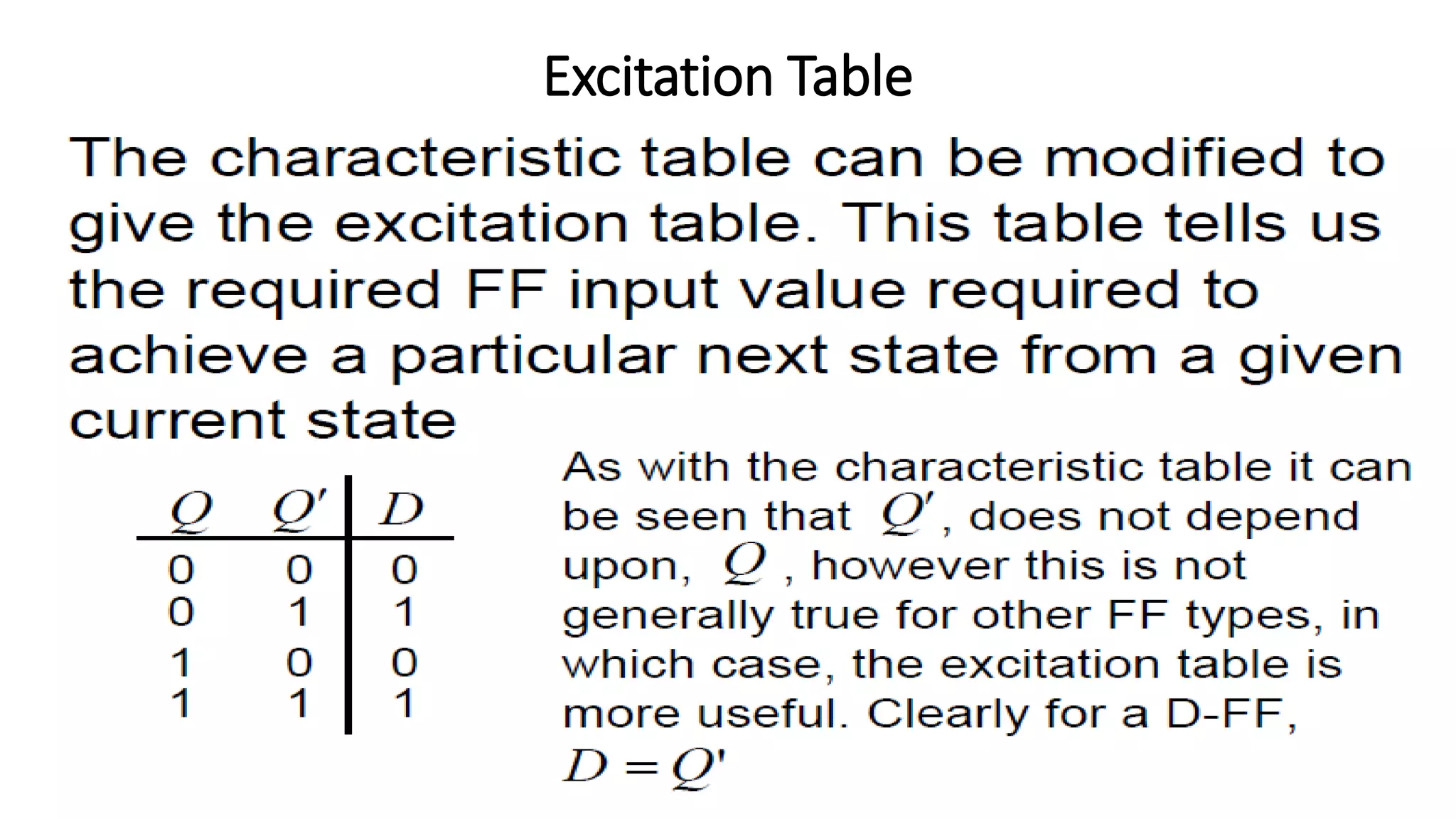

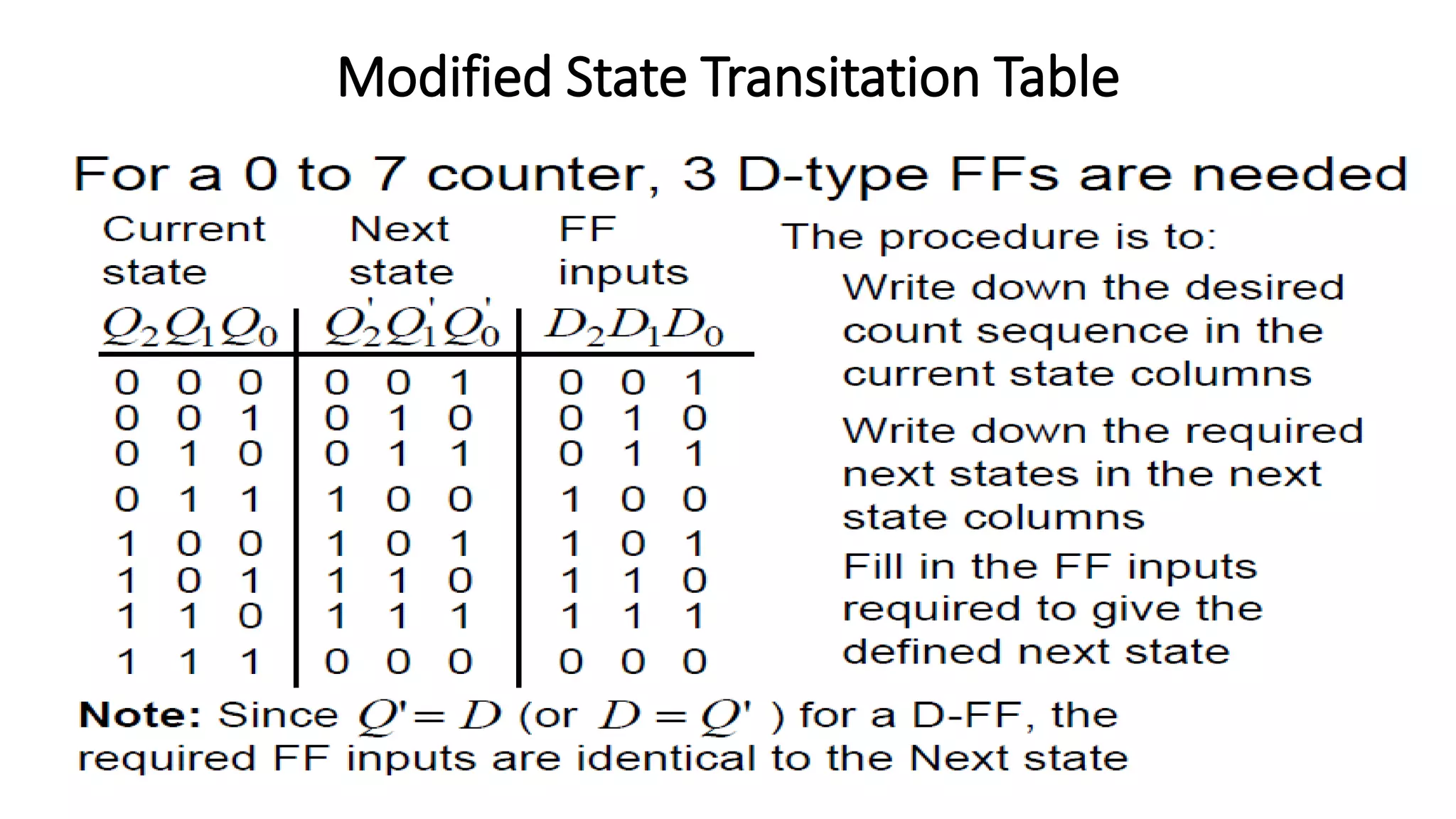

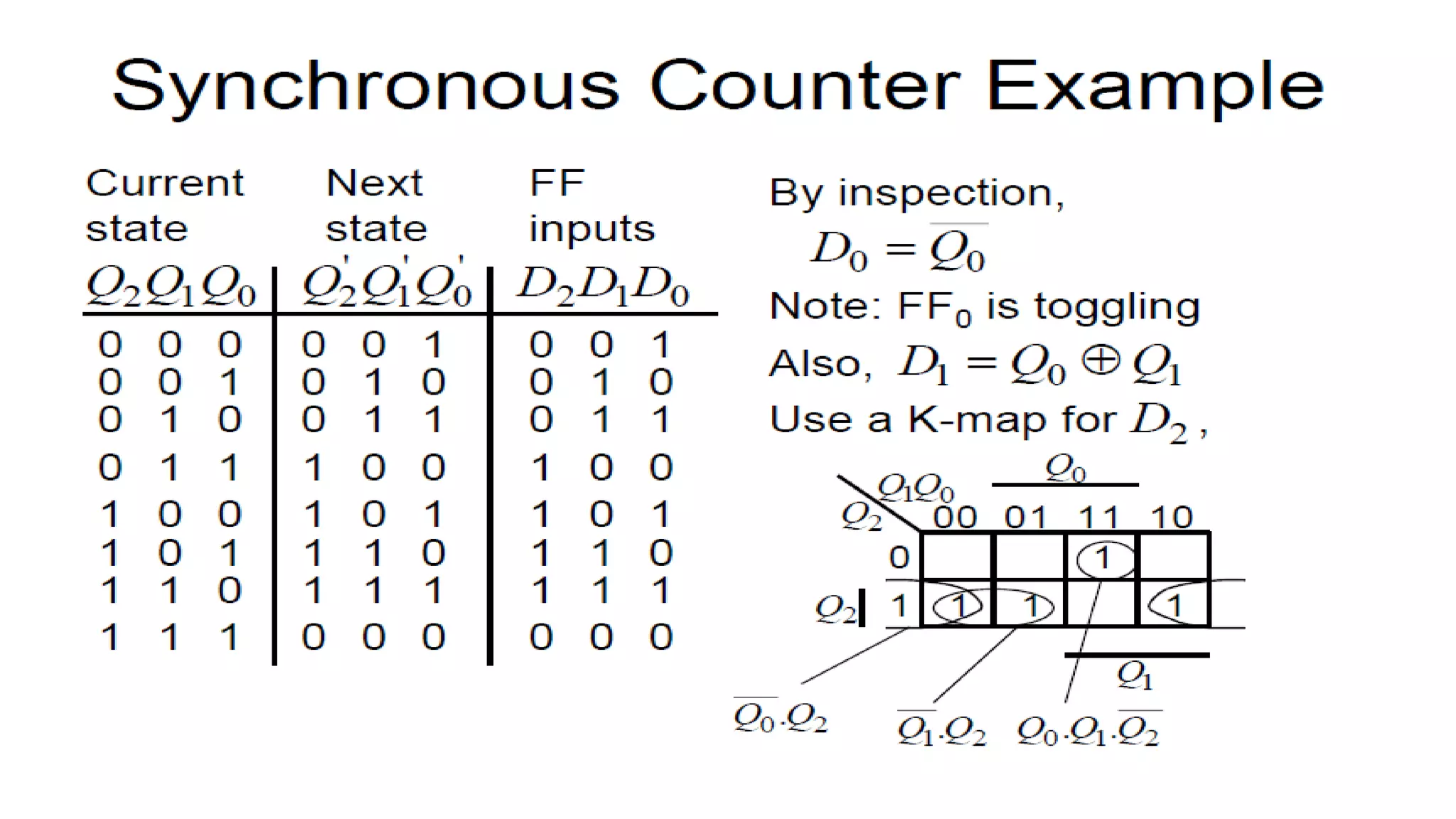

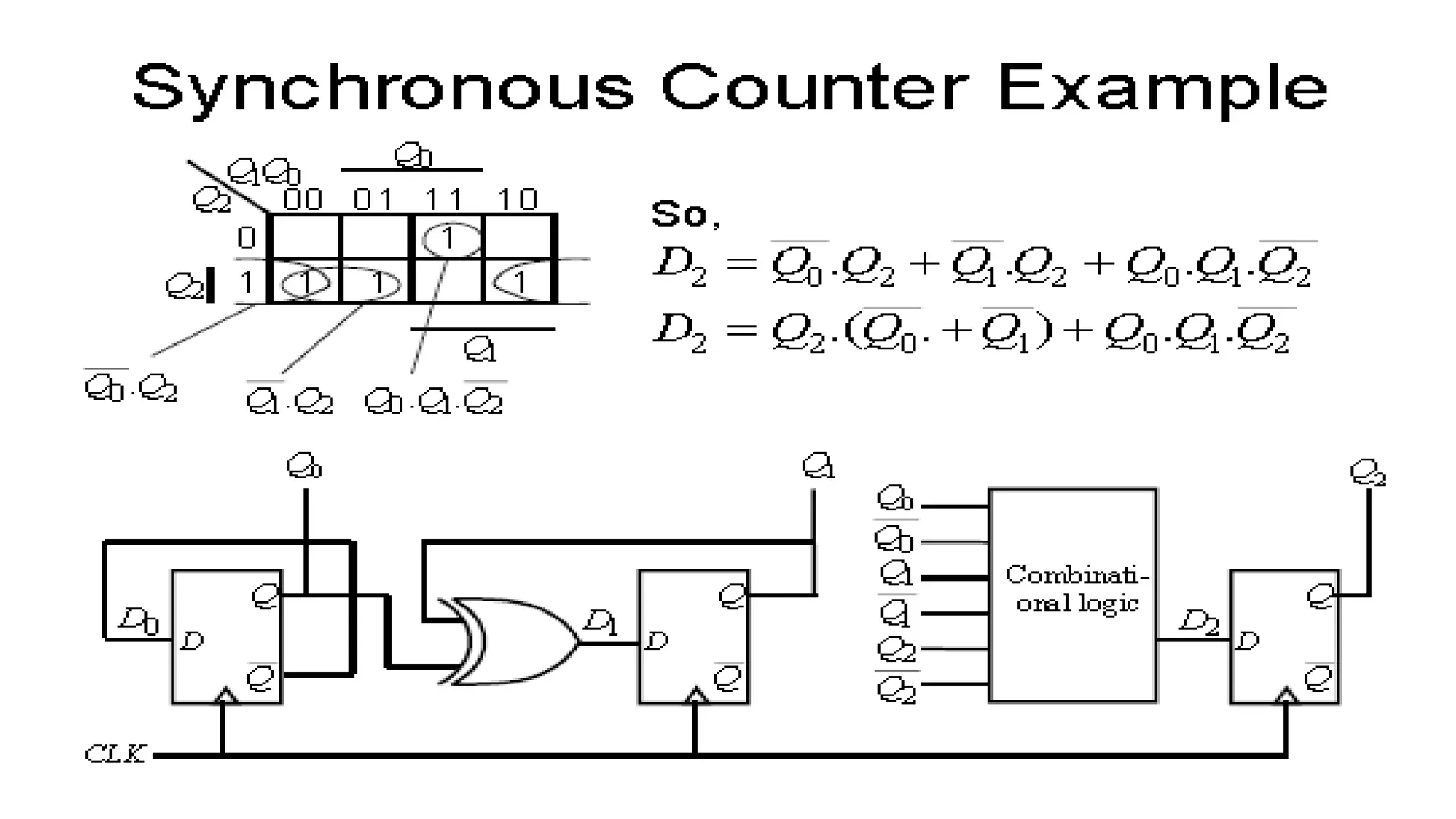

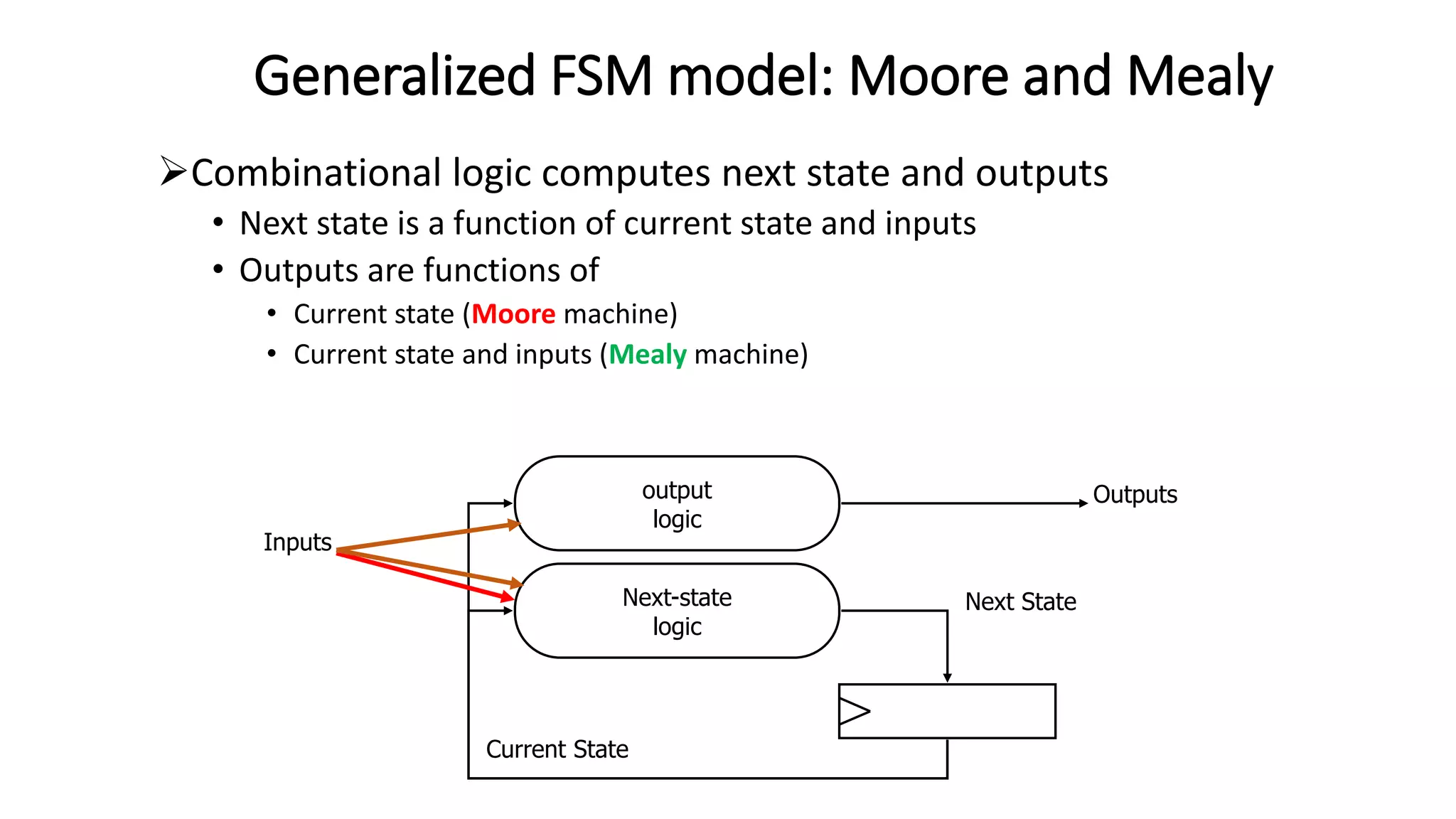

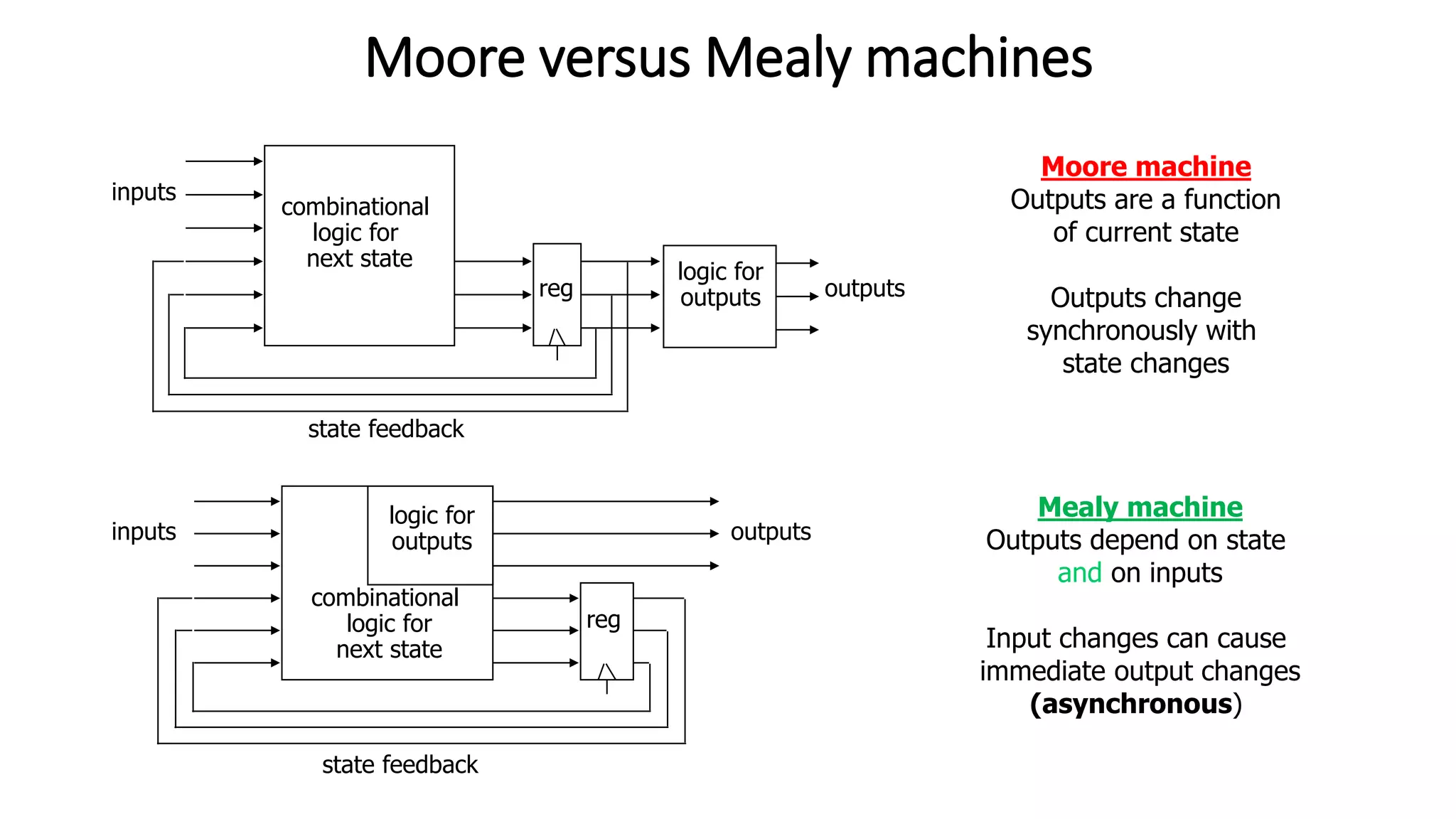

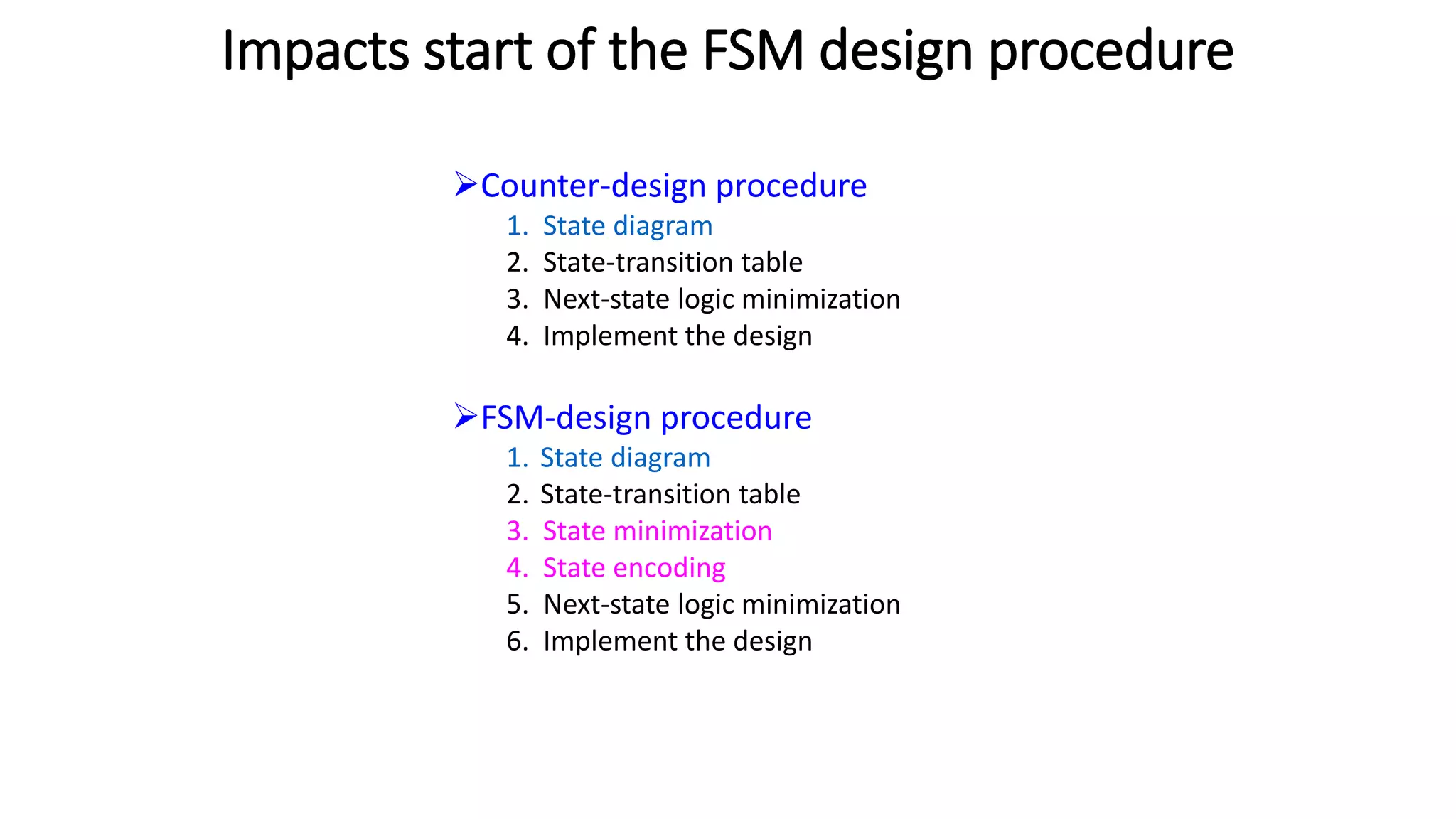

This document discusses various types of counters including asynchronous (ripple) counters and synchronous counters. It describes the basic operation and characteristics of ripple counters, synchronous counters, ring counters, Johnson counters, and modulus counters. It also covers the differences between synchronous and asynchronous sequential circuits. Finally, it provides information on finite state machines, including the differences between Moore and Mealy machines.

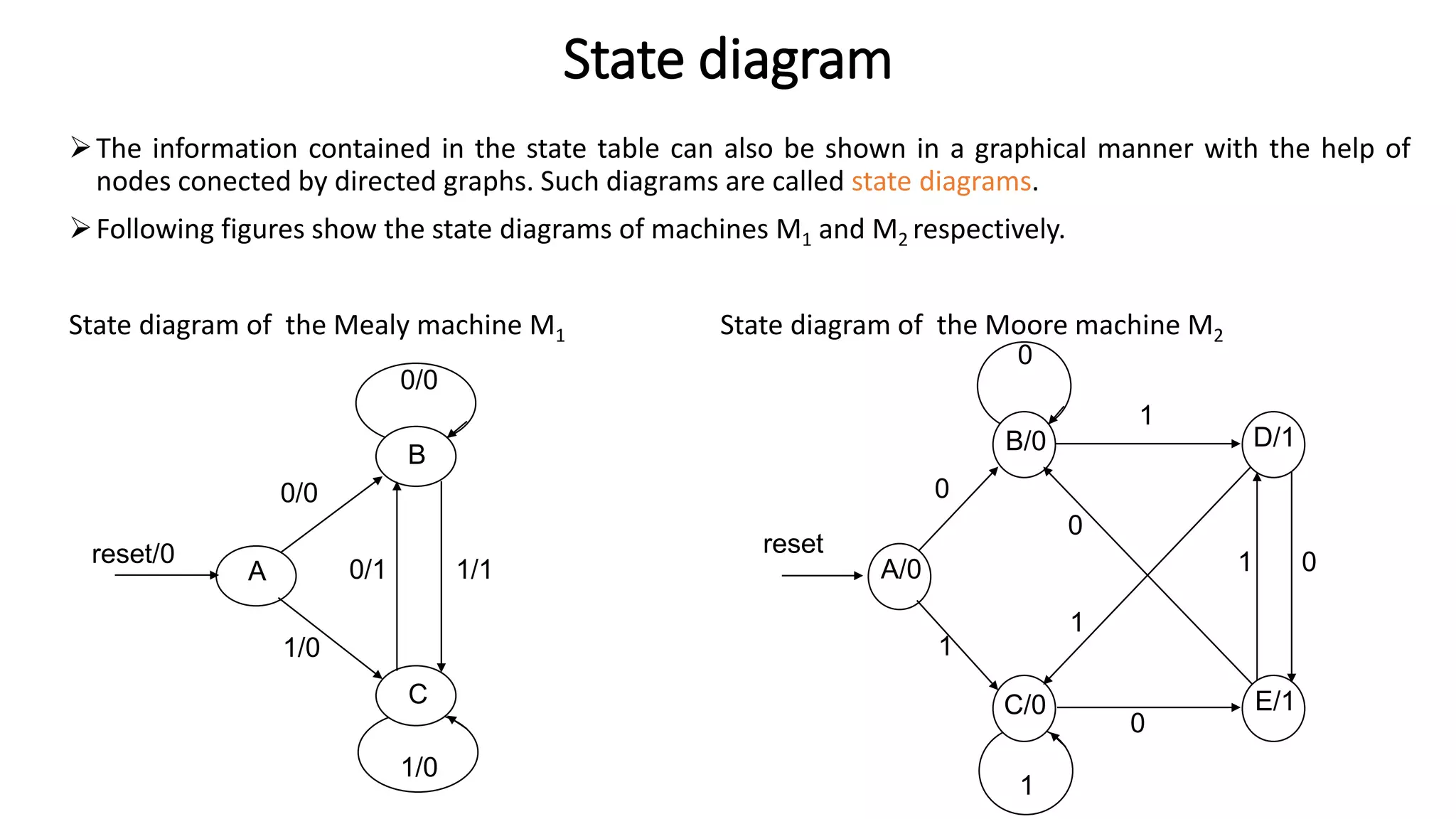

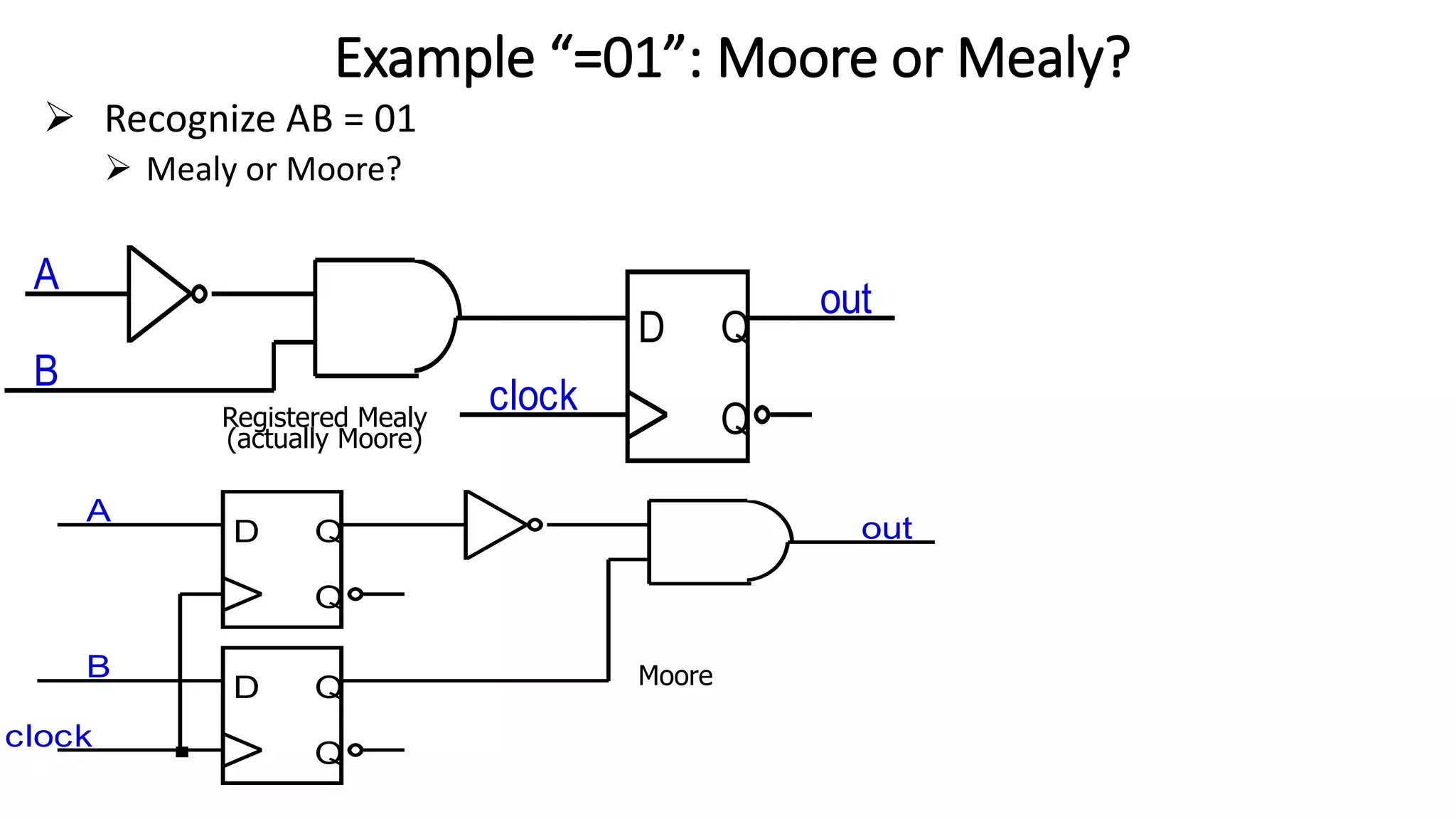

![State Diagrams

➢ Moore machine

• Each state is labeled by a pair:

state-name/output or state-name [output]

➢ Mealy machine

• Each transition arc is labeled by a pair:

input-condition/output](https://image.slidesharecdn.com/adeunit-4-191215045916/75/Ade-unit-4-Counters-28-2048.jpg)