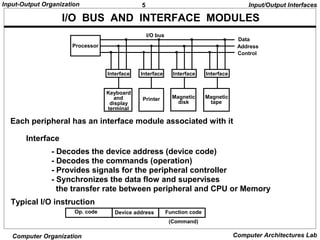

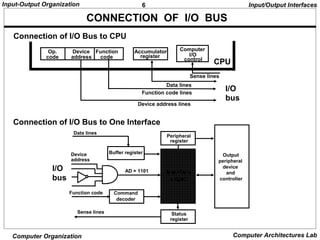

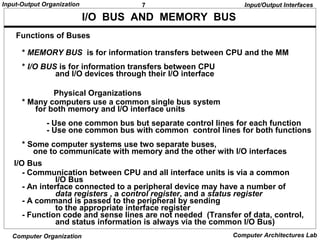

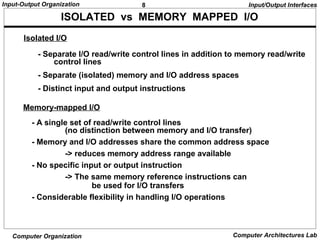

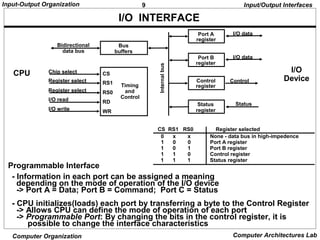

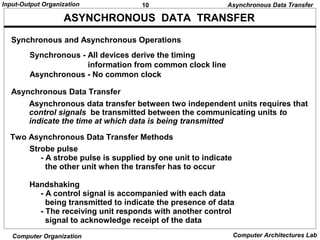

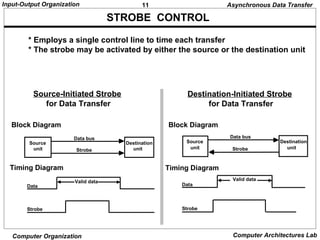

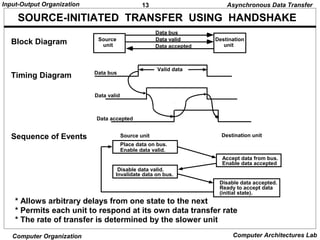

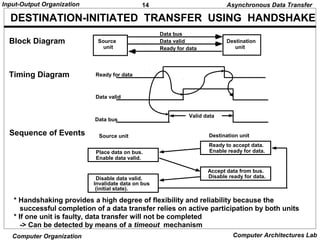

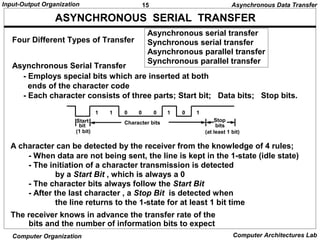

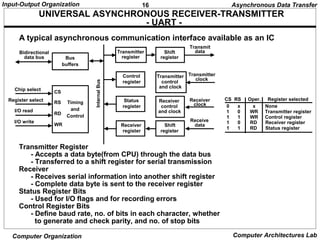

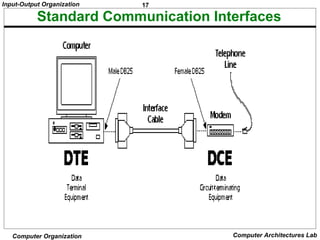

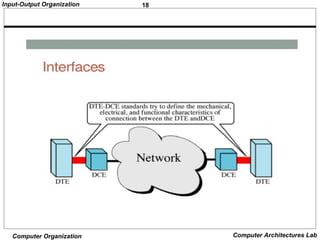

This document discusses input/output organization in computer systems. It describes peripheral devices for input and output, input/output interfaces that allow communication between peripherals and the CPU/memory, and various methods for transferring data asynchronously between independent devices or systems, including strobe control, handshaking, and serial transmission. Asynchronous data transfer is necessary because peripherals often operate at different speeds than the CPU and memory.