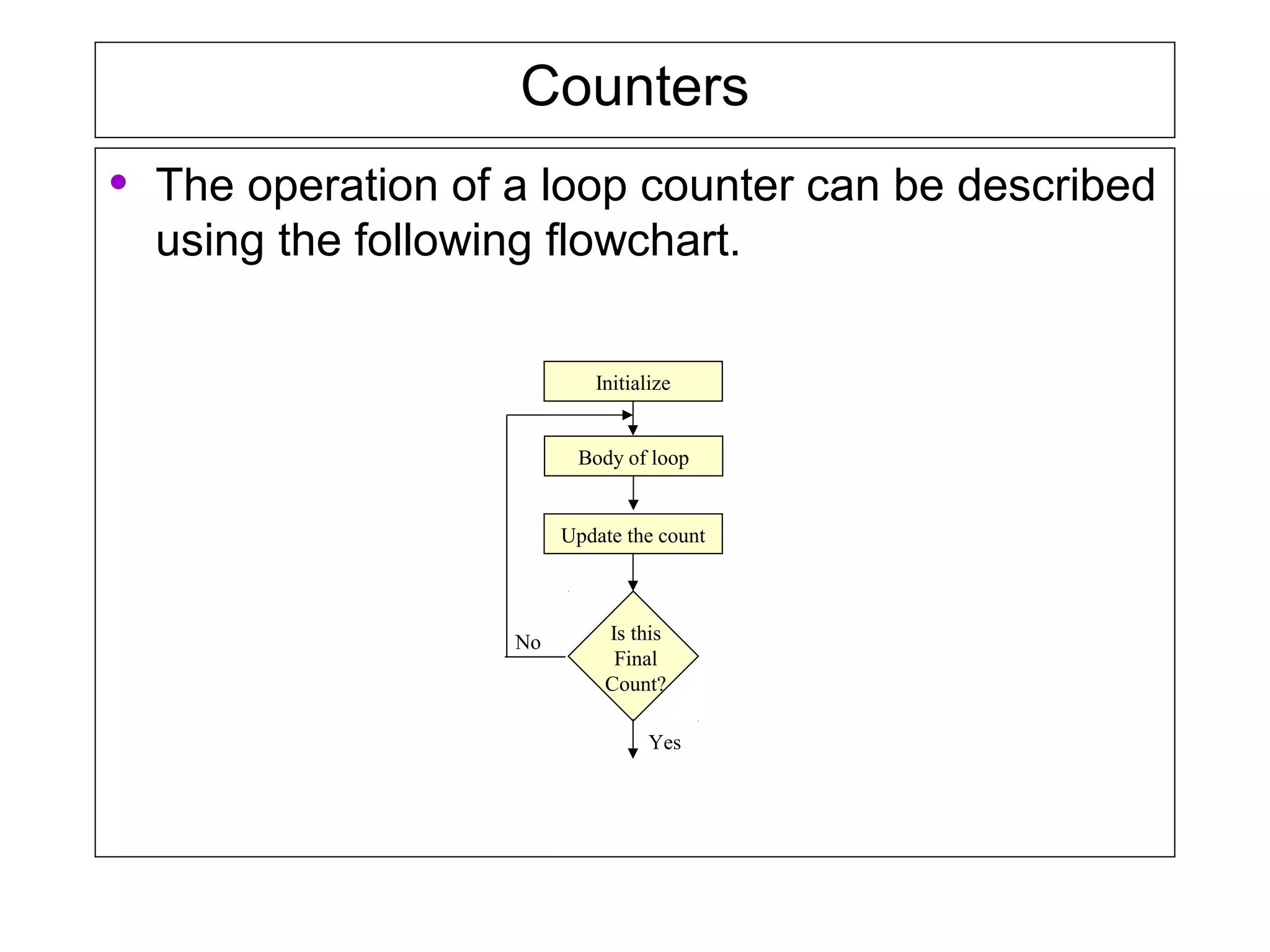

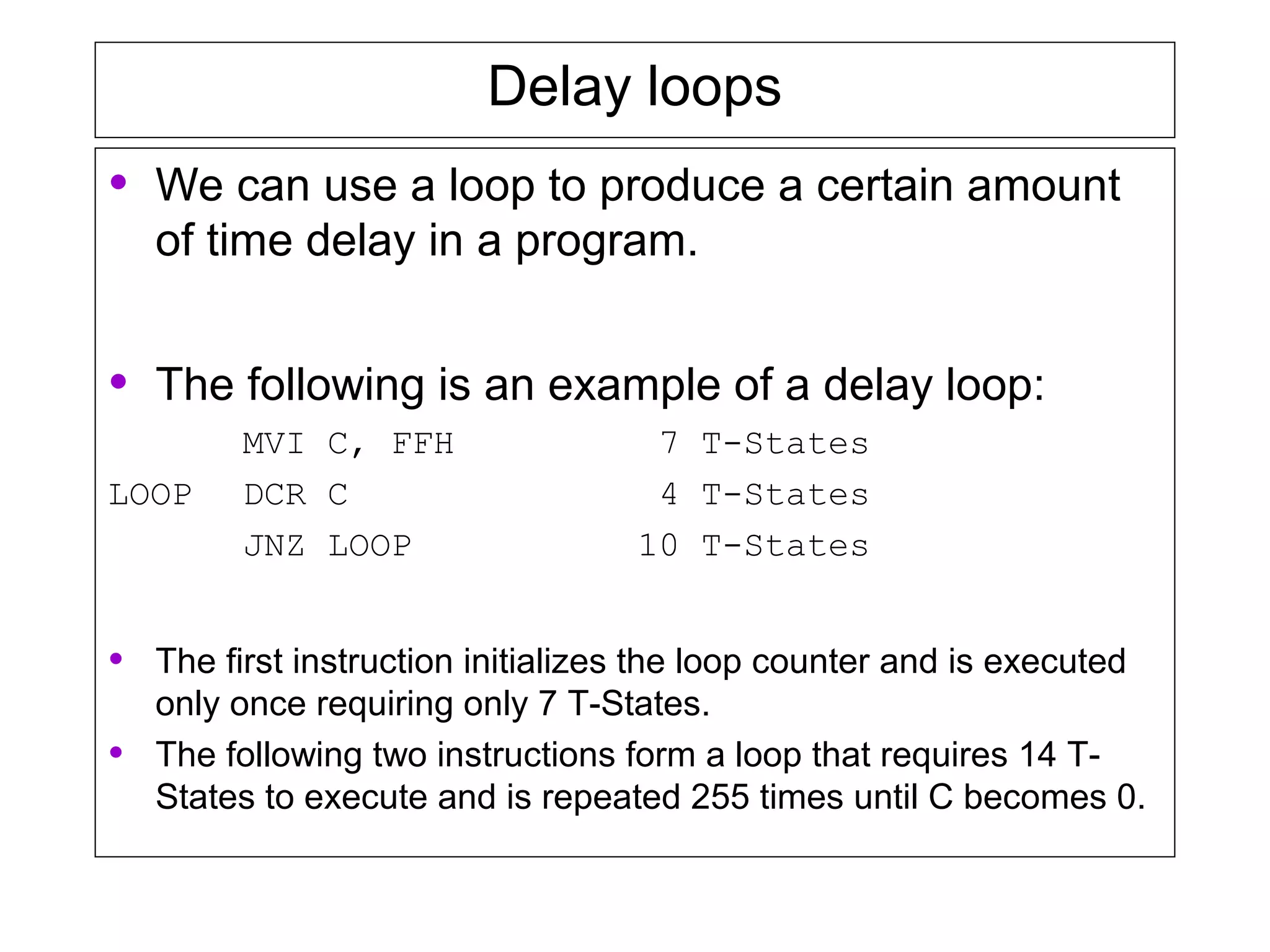

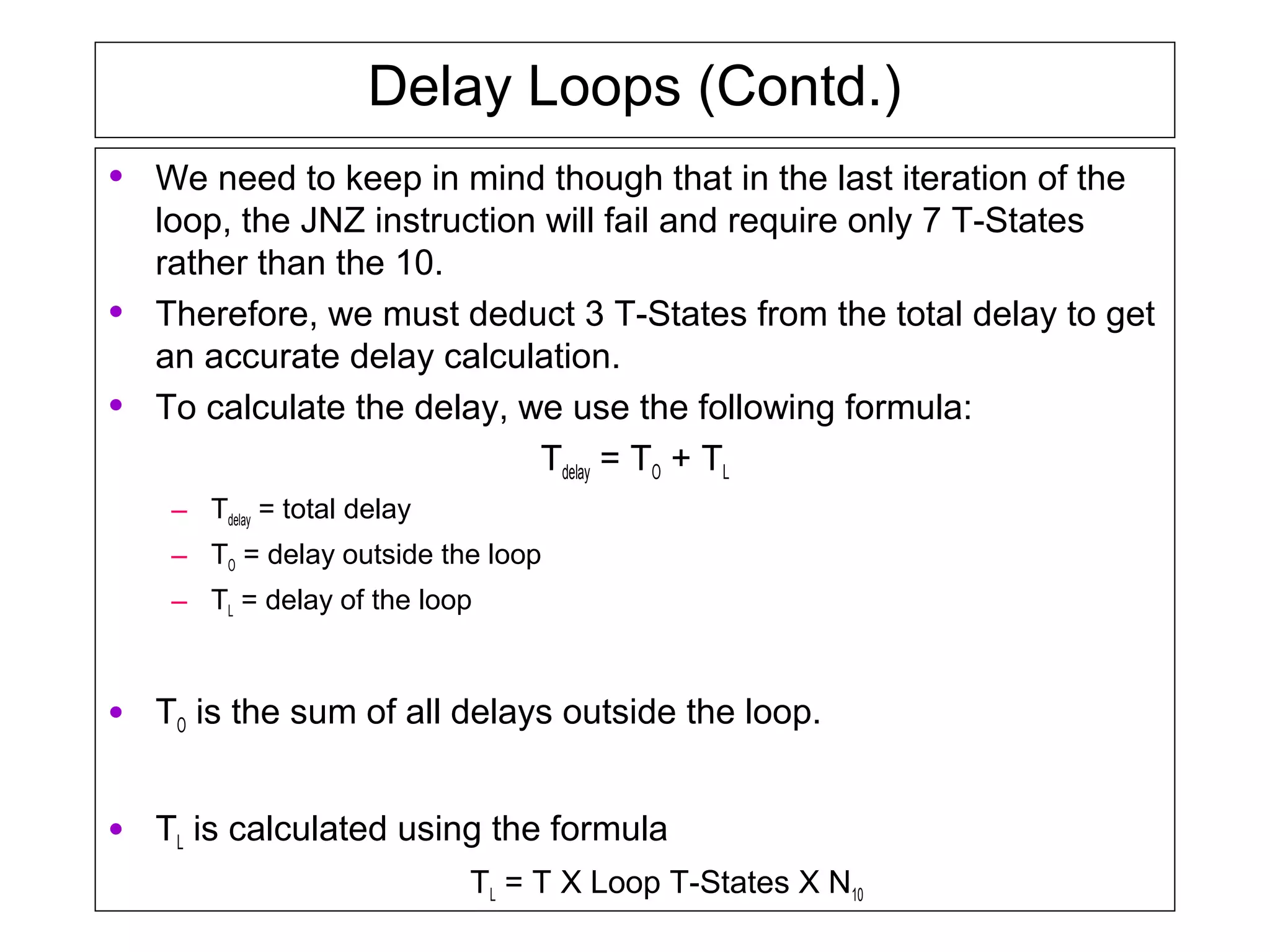

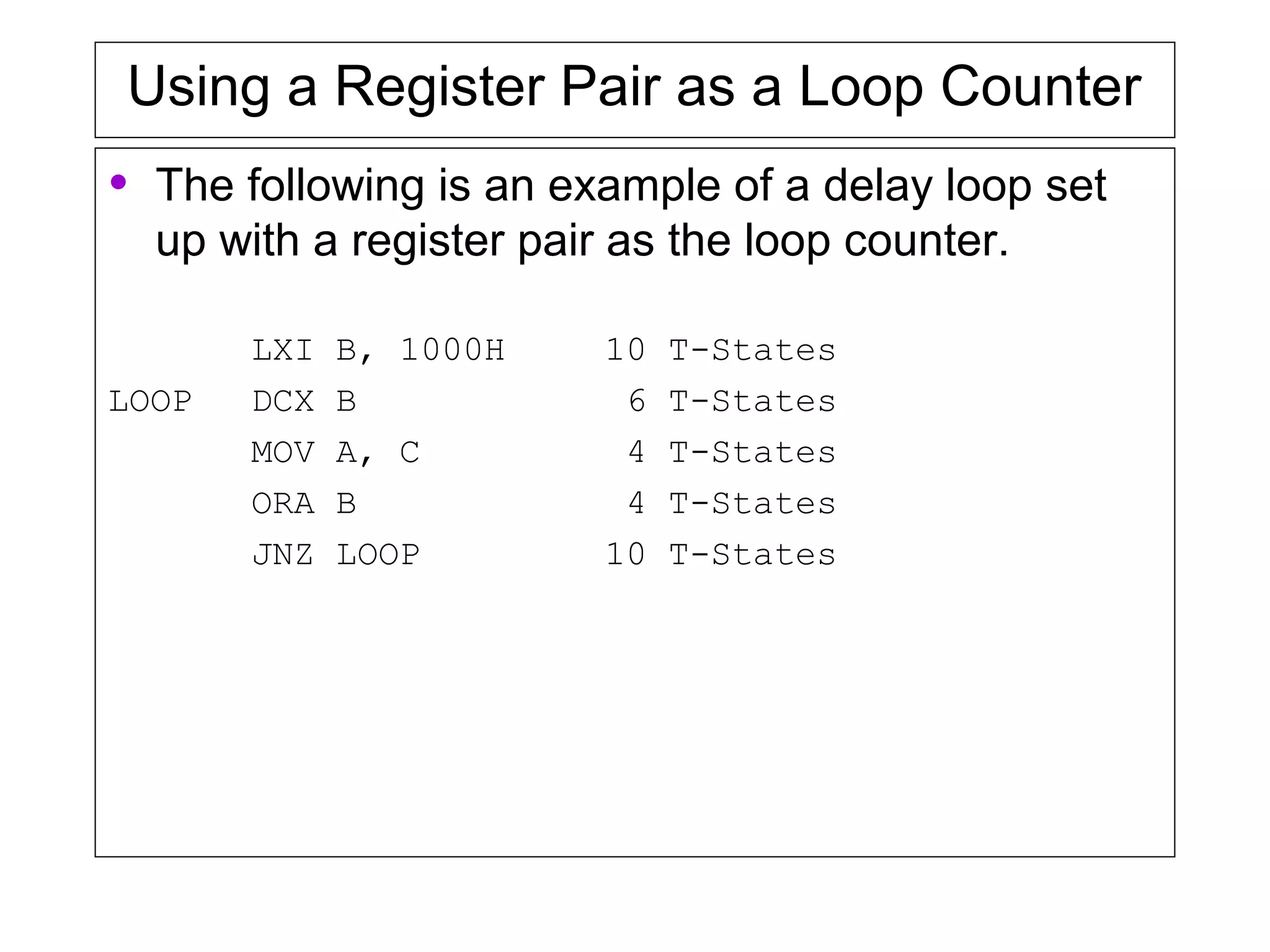

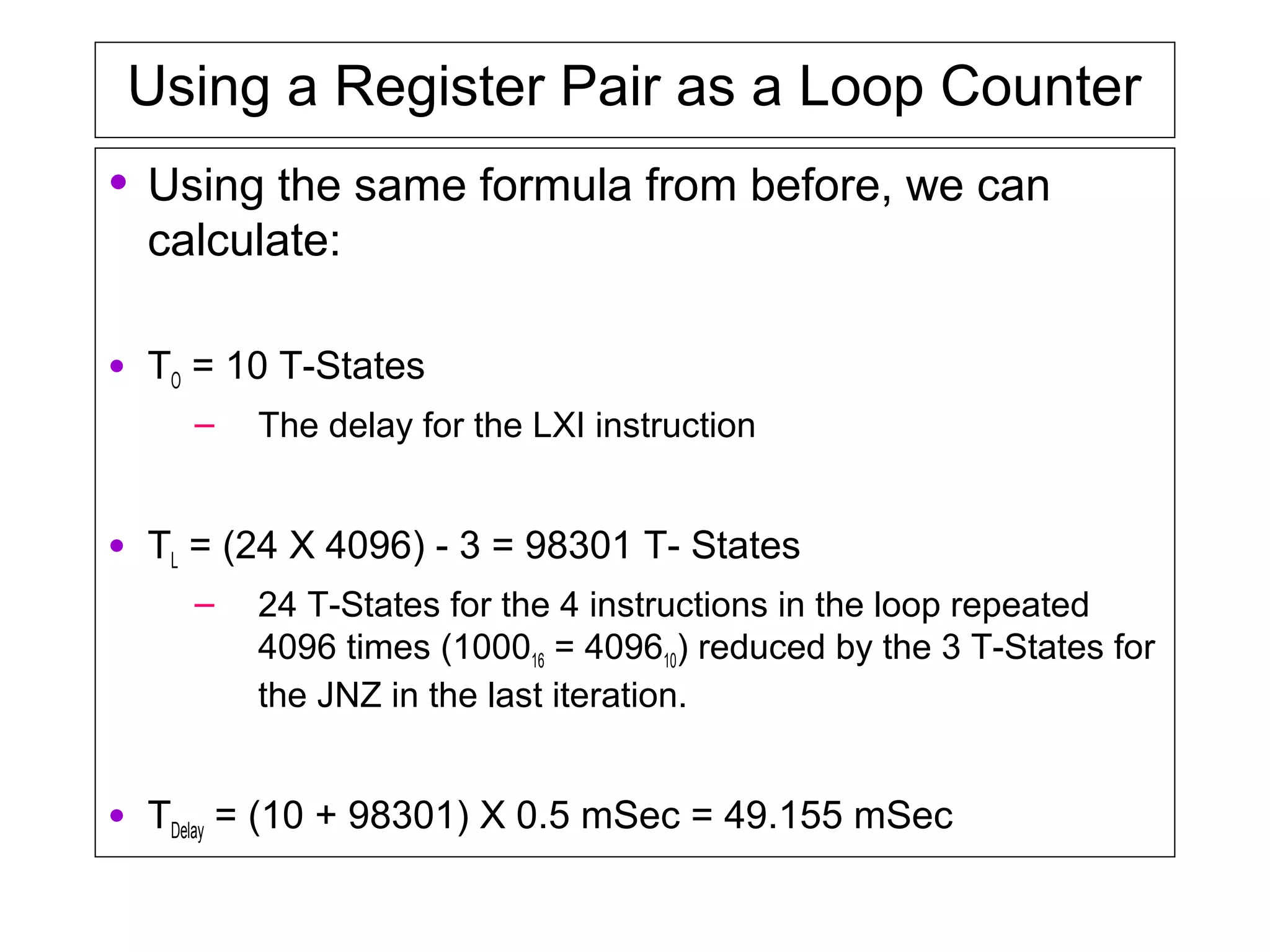

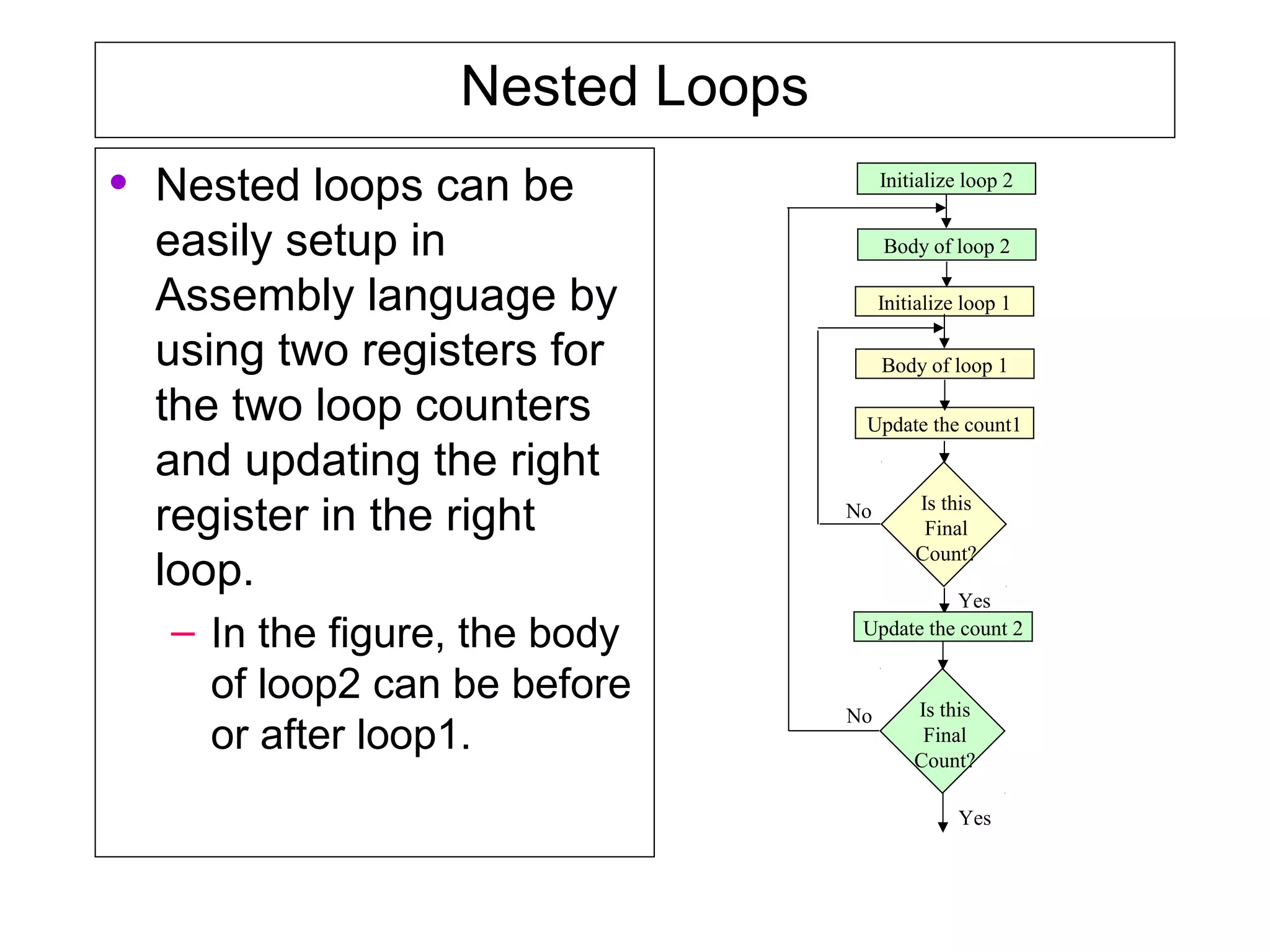

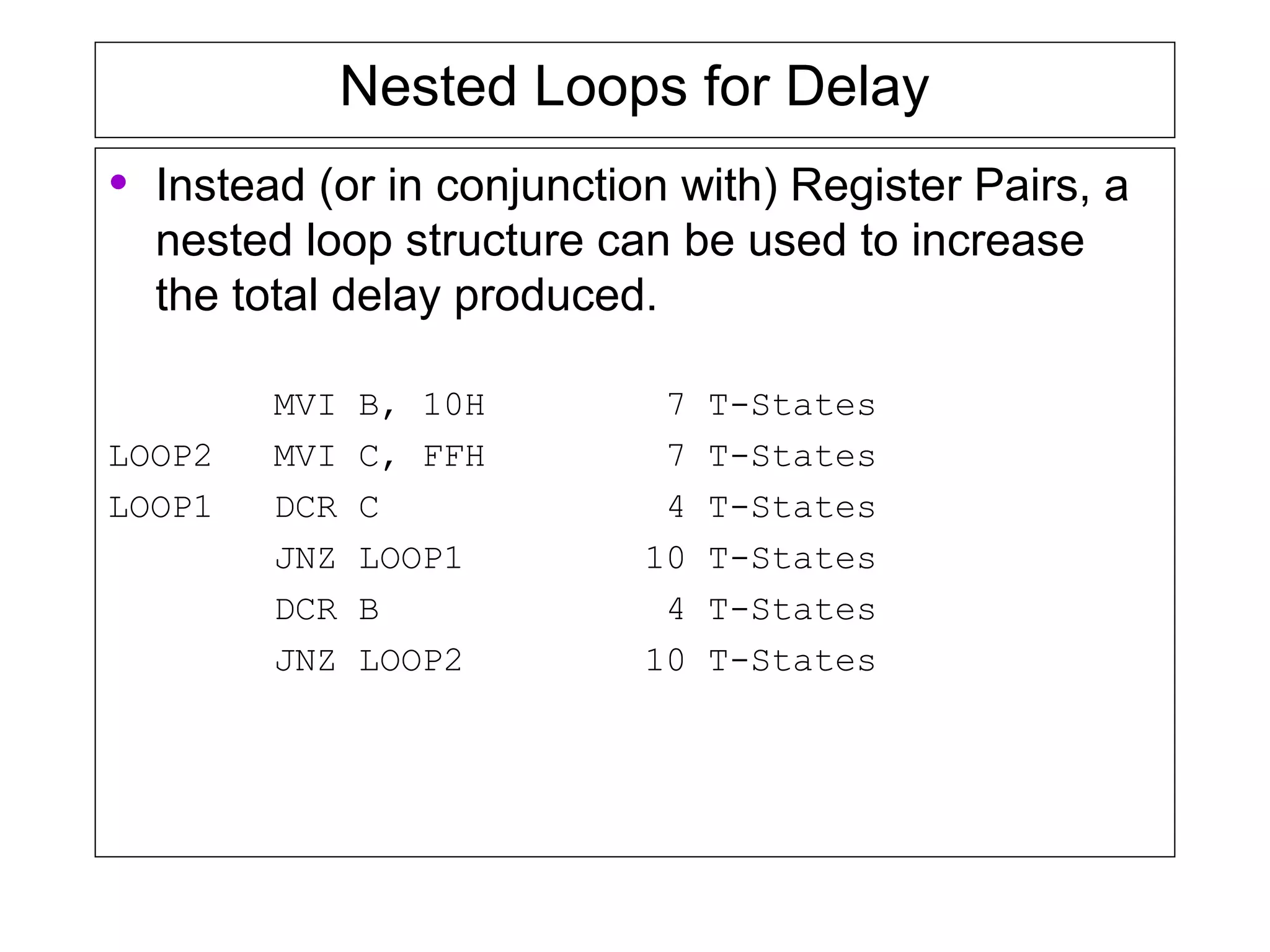

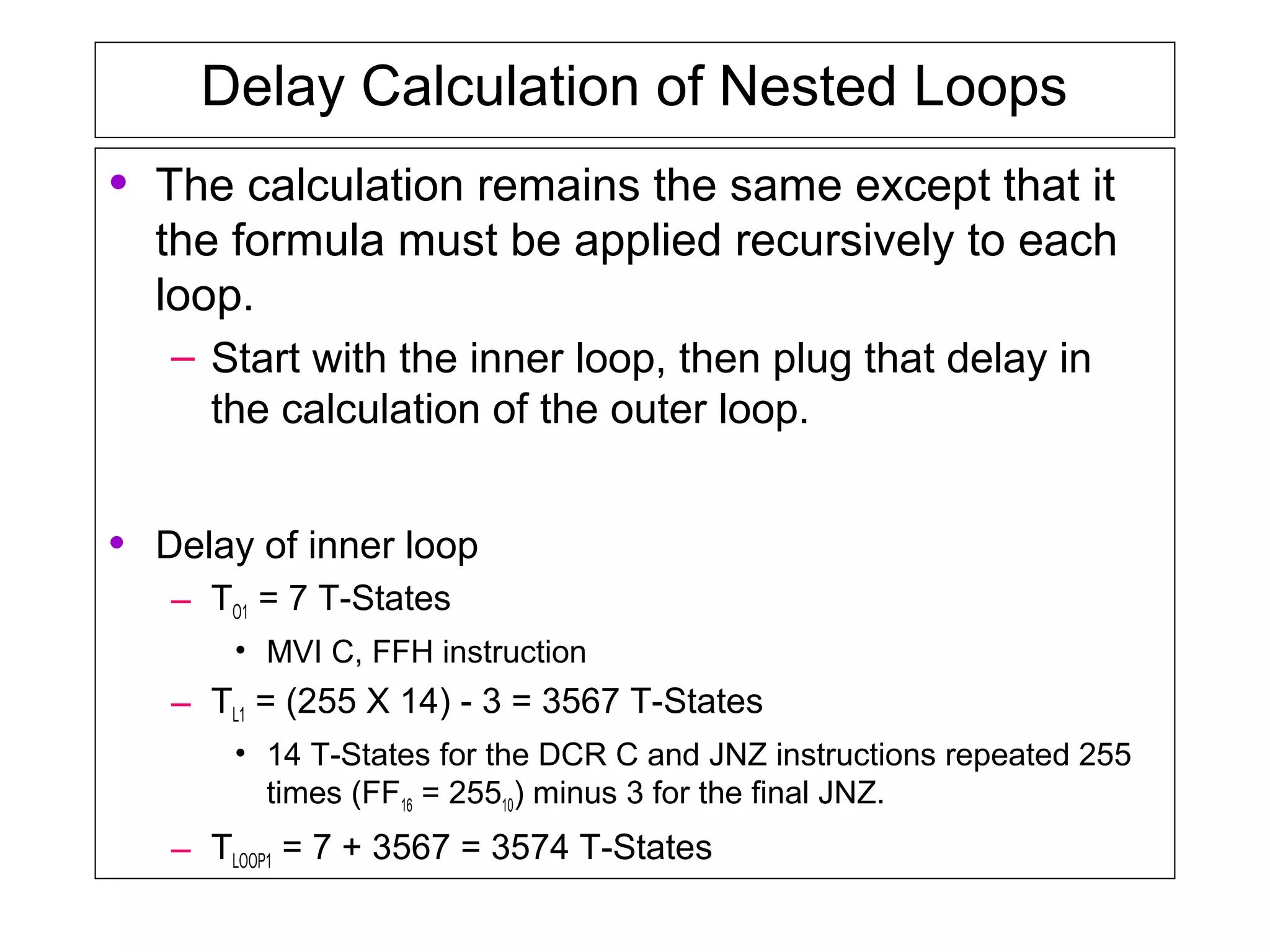

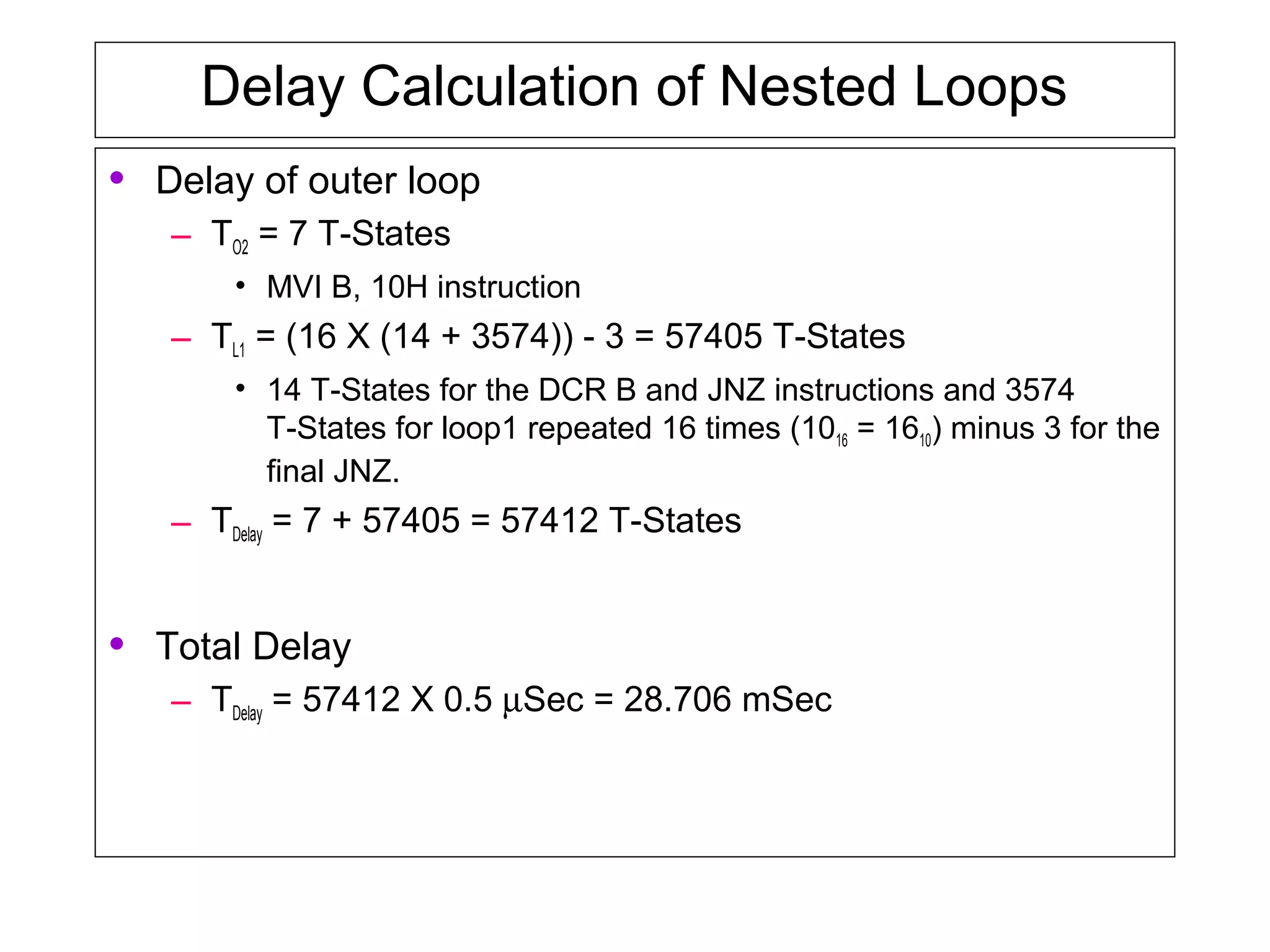

Counters and time delays can be implemented in software or hardware using loop constructs. Counters keep track of events like iterations in a for loop, while delays set up accurate timing between events. Delays can be implemented using loops that iterate a set number of times based on instruction timing. Nested loops and register pairs can increase delay times for longer periods.