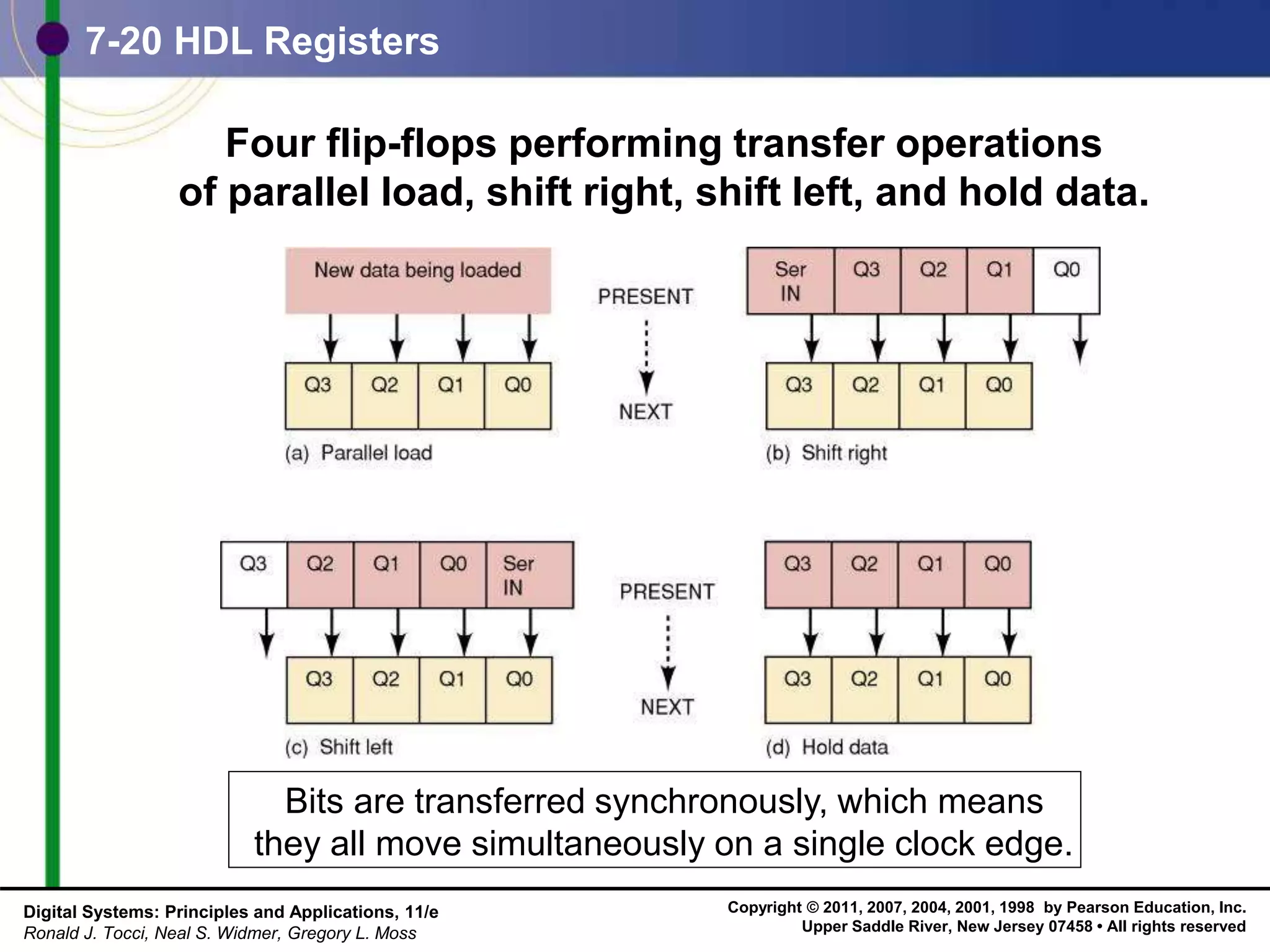

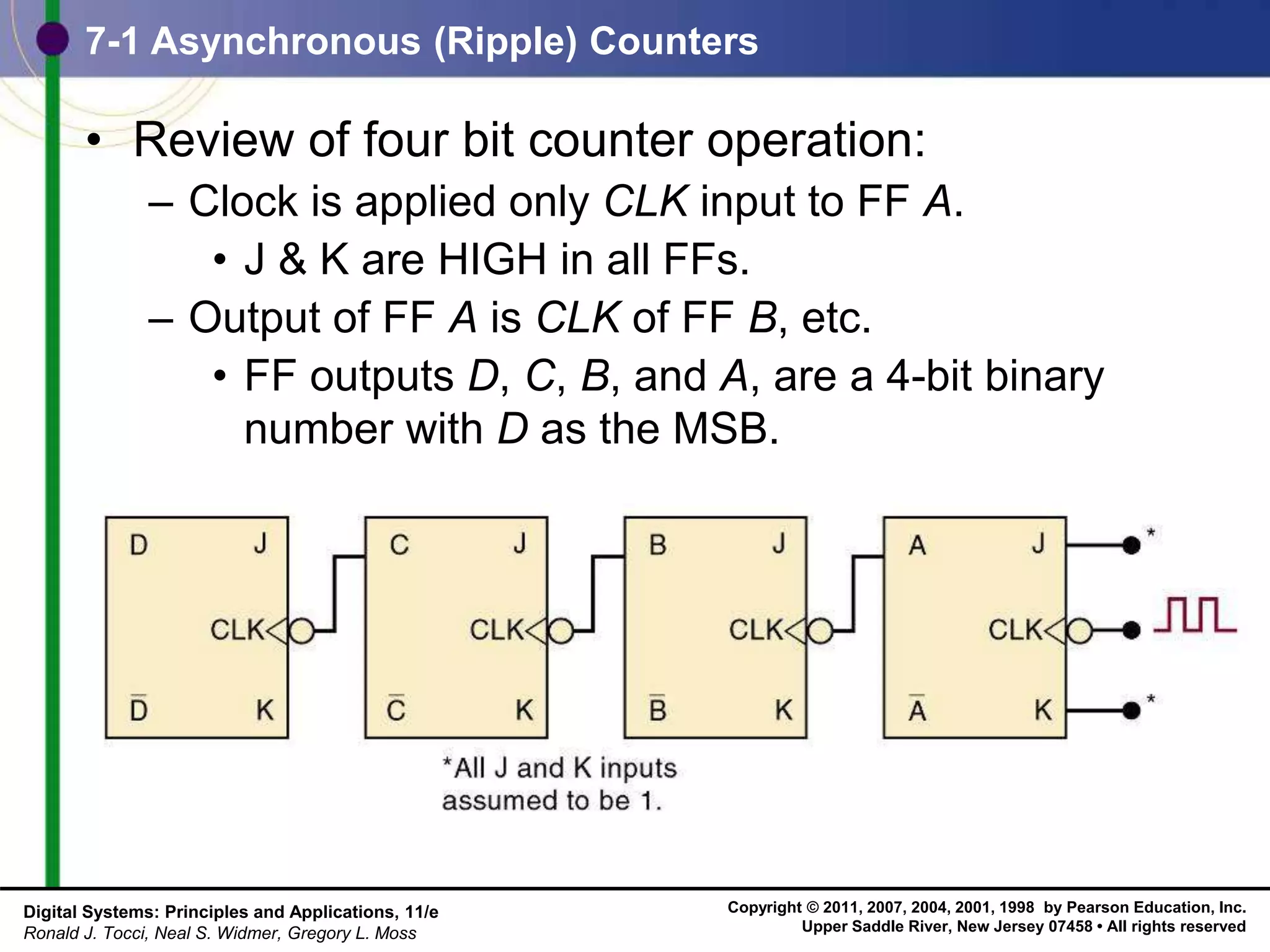

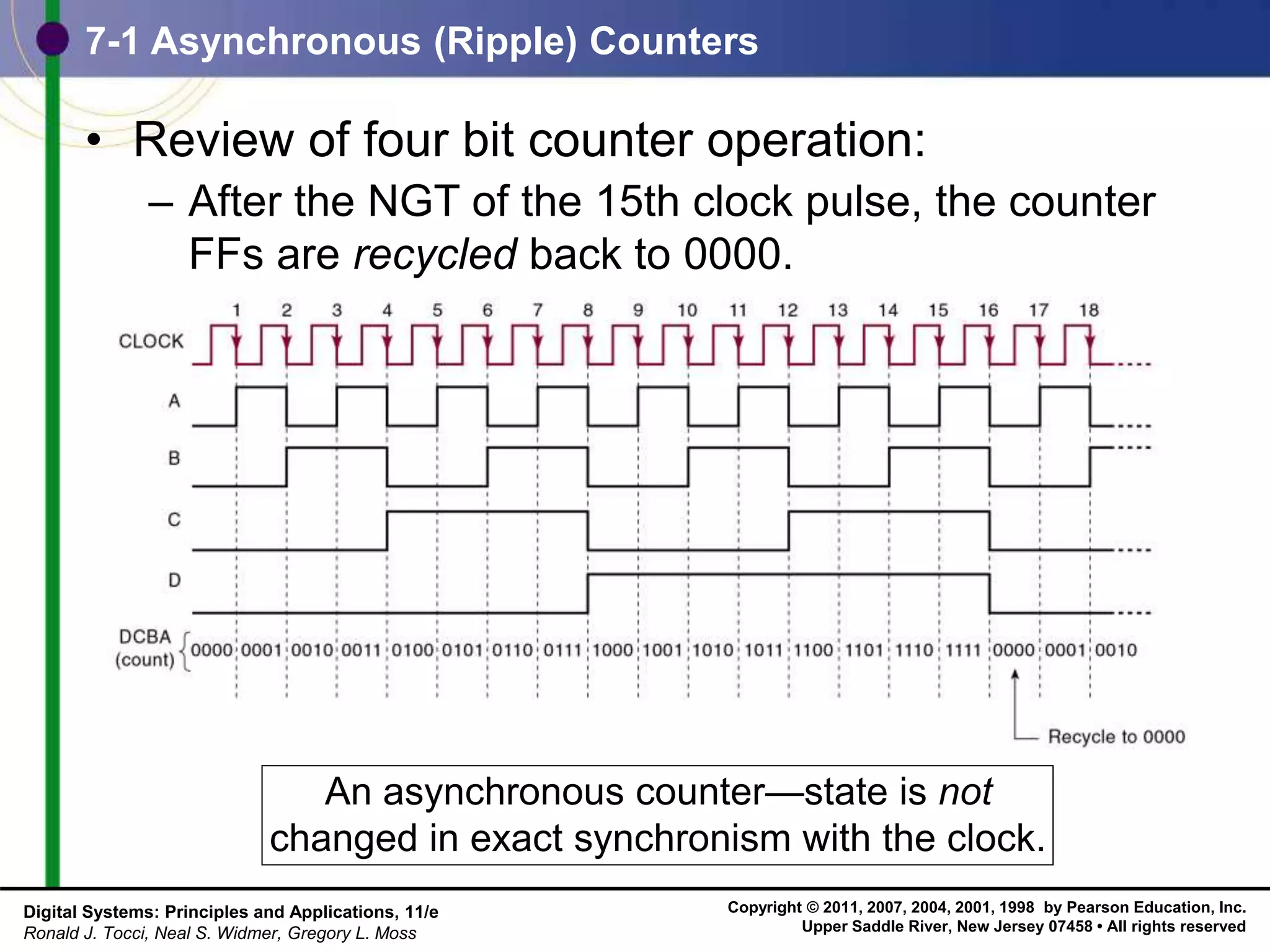

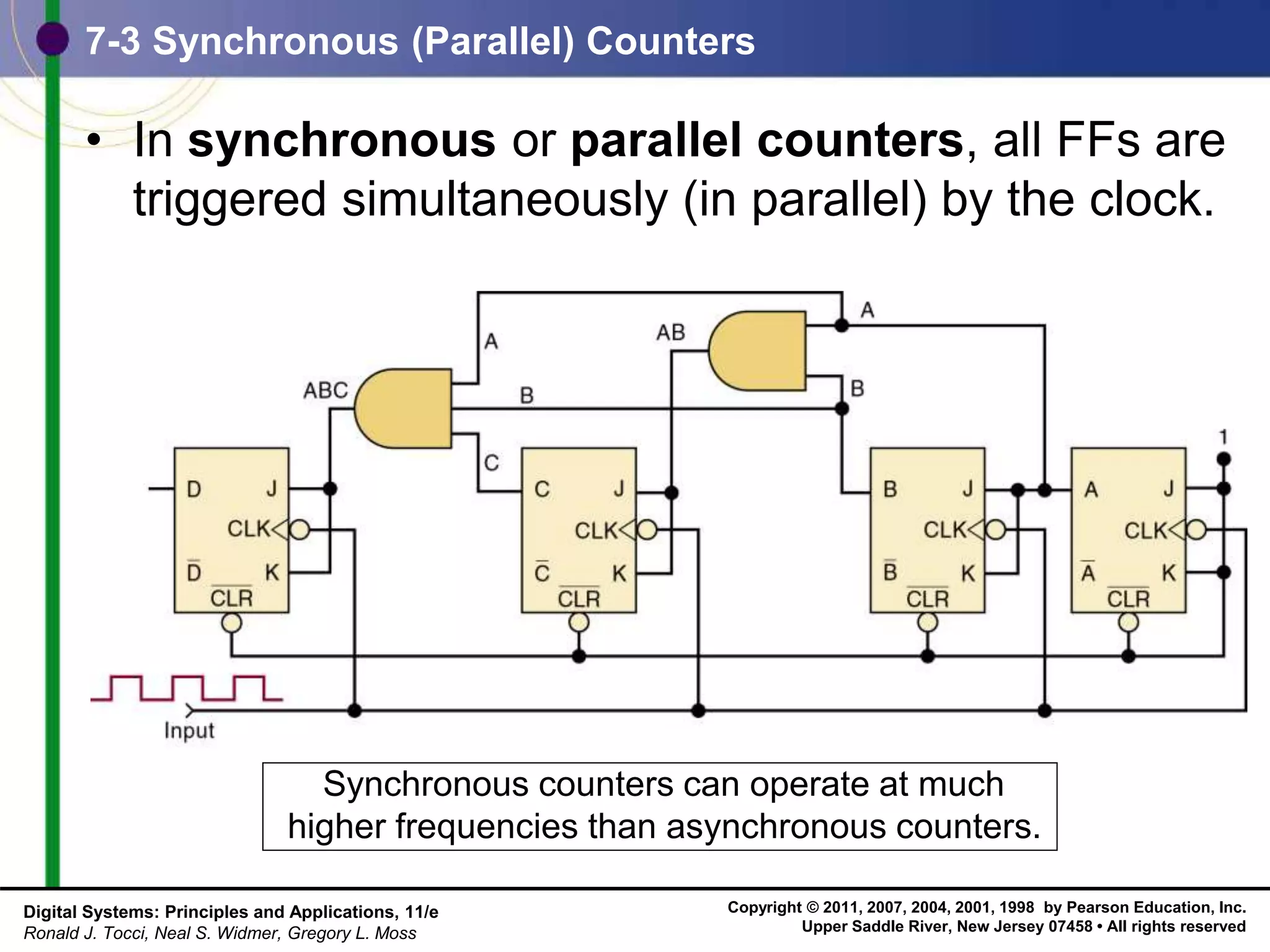

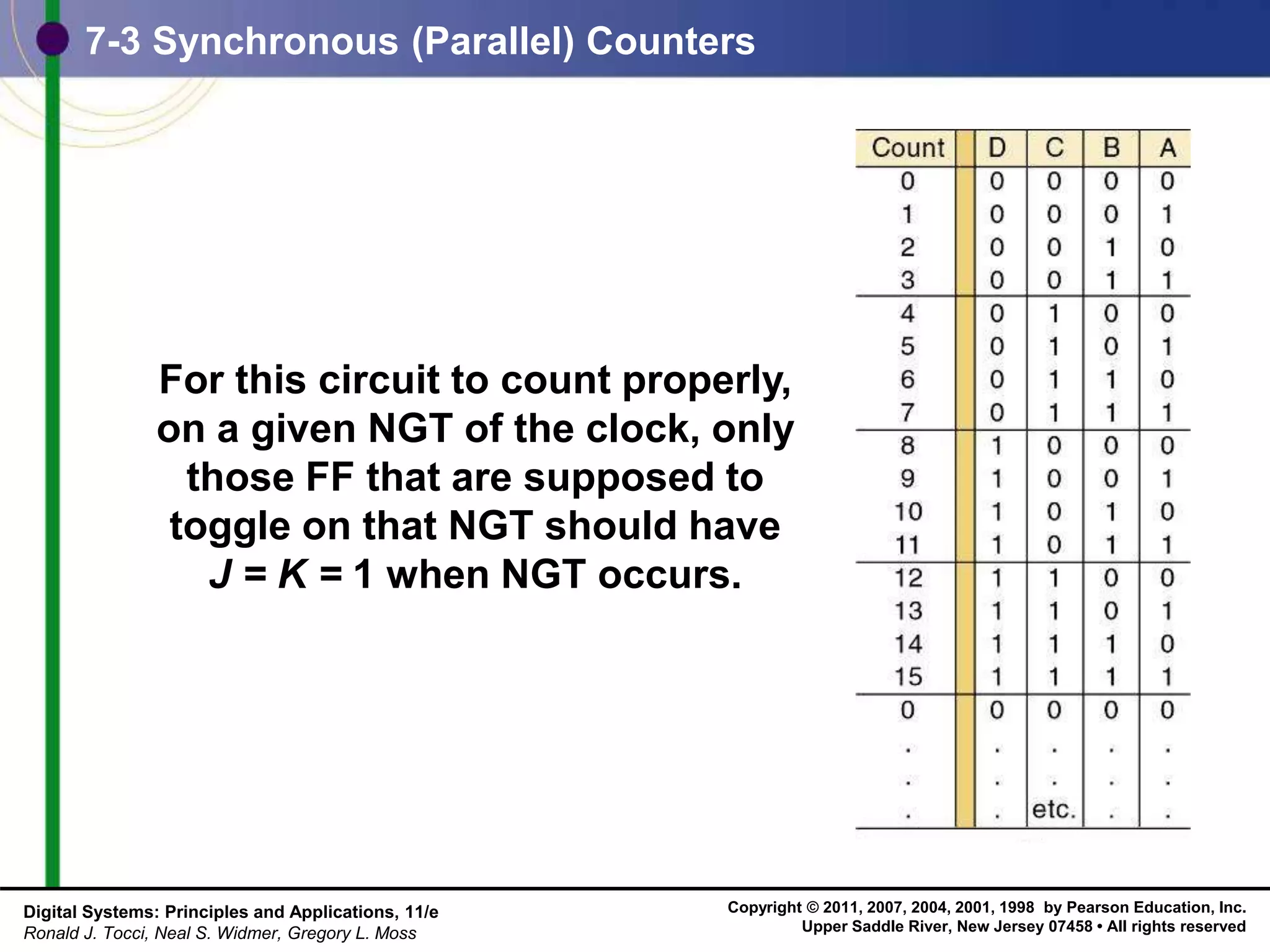

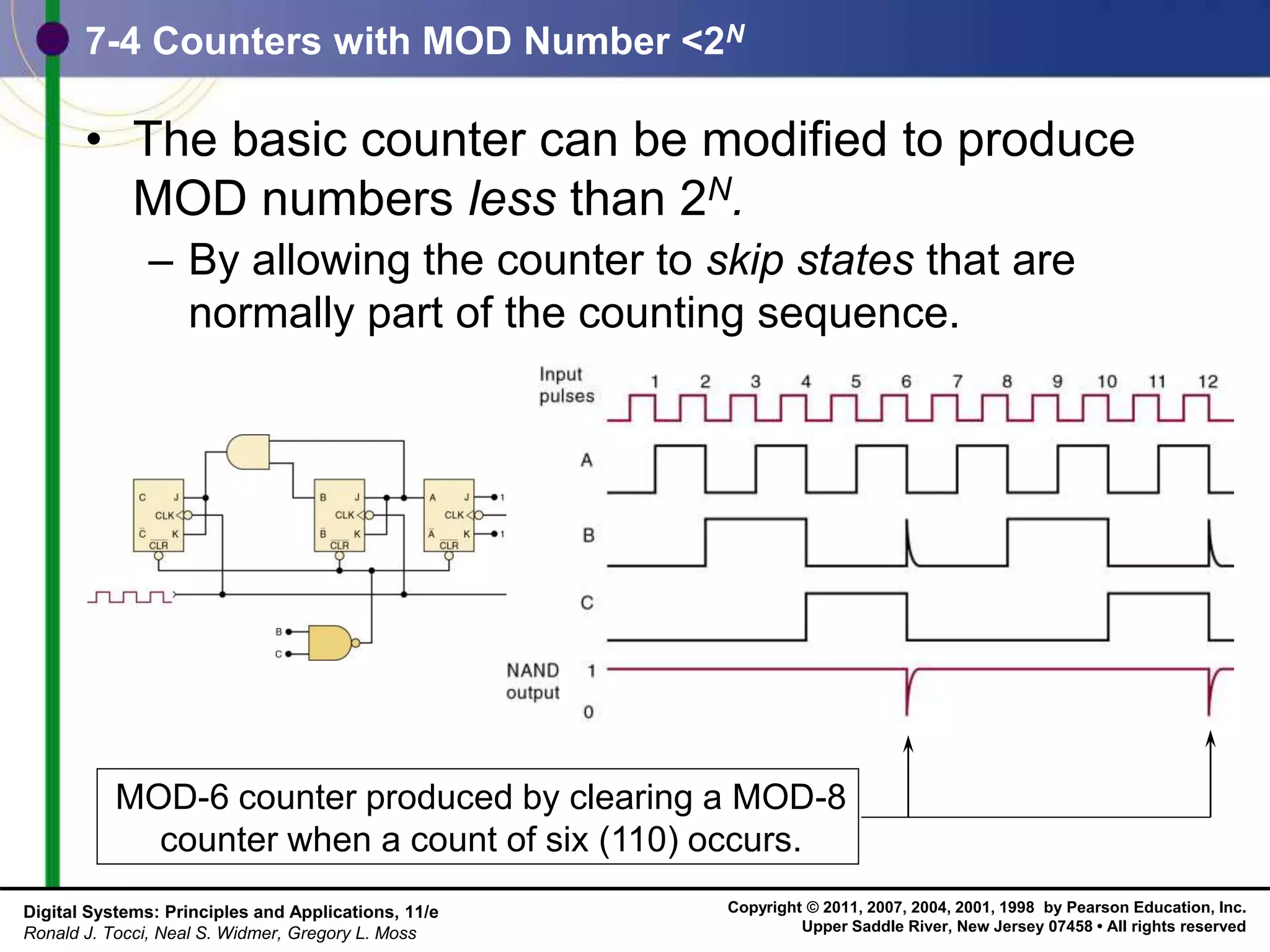

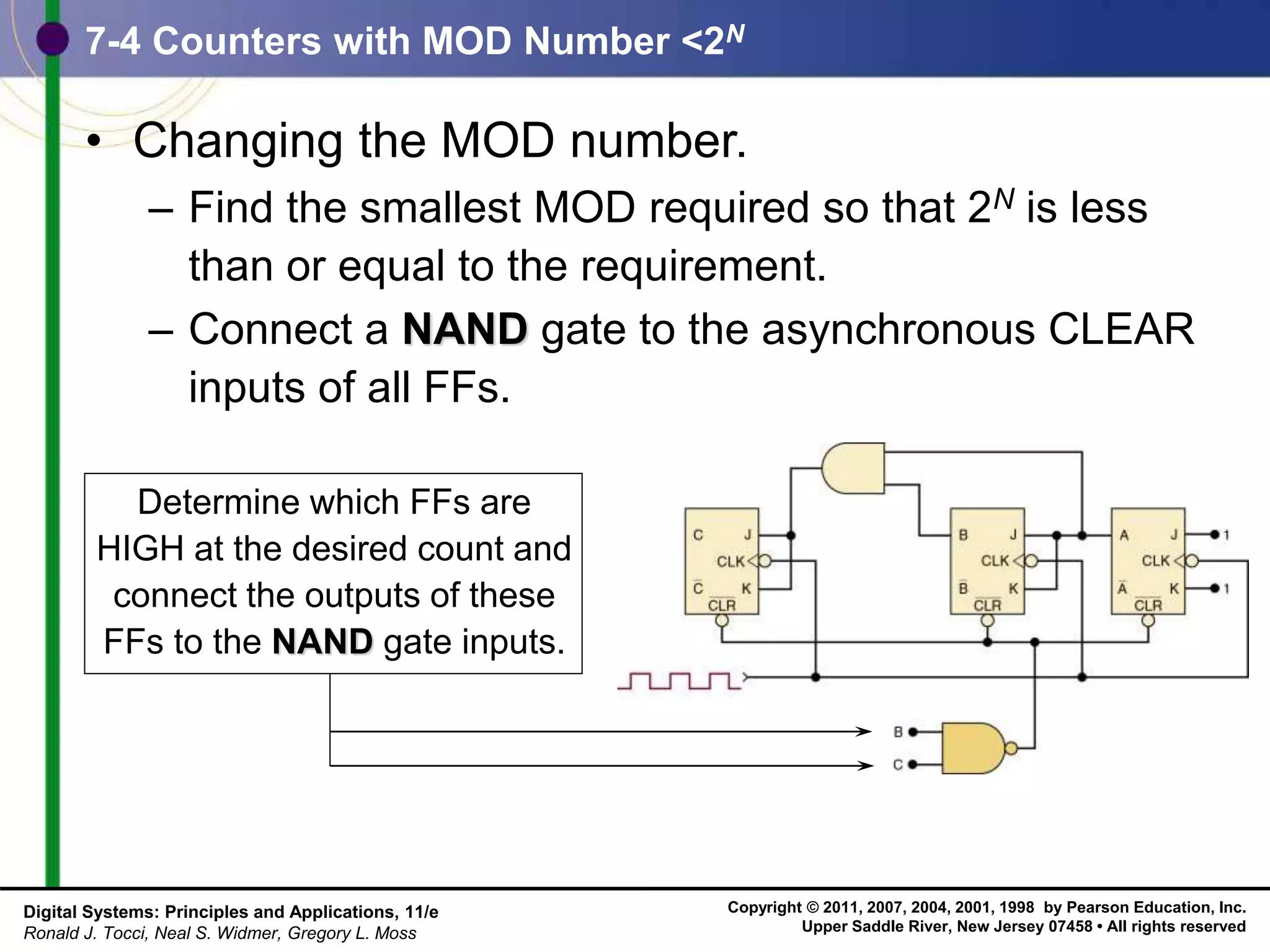

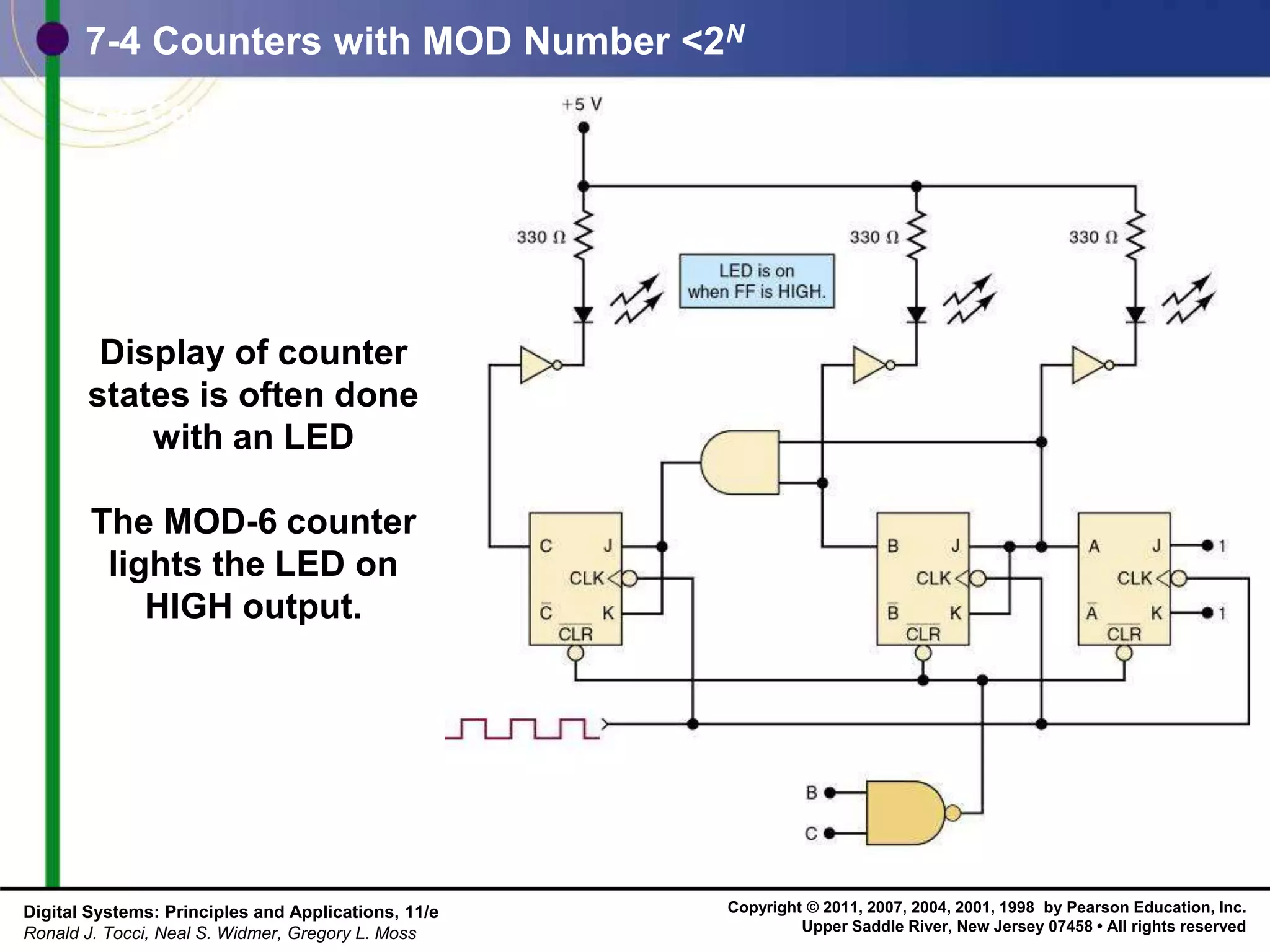

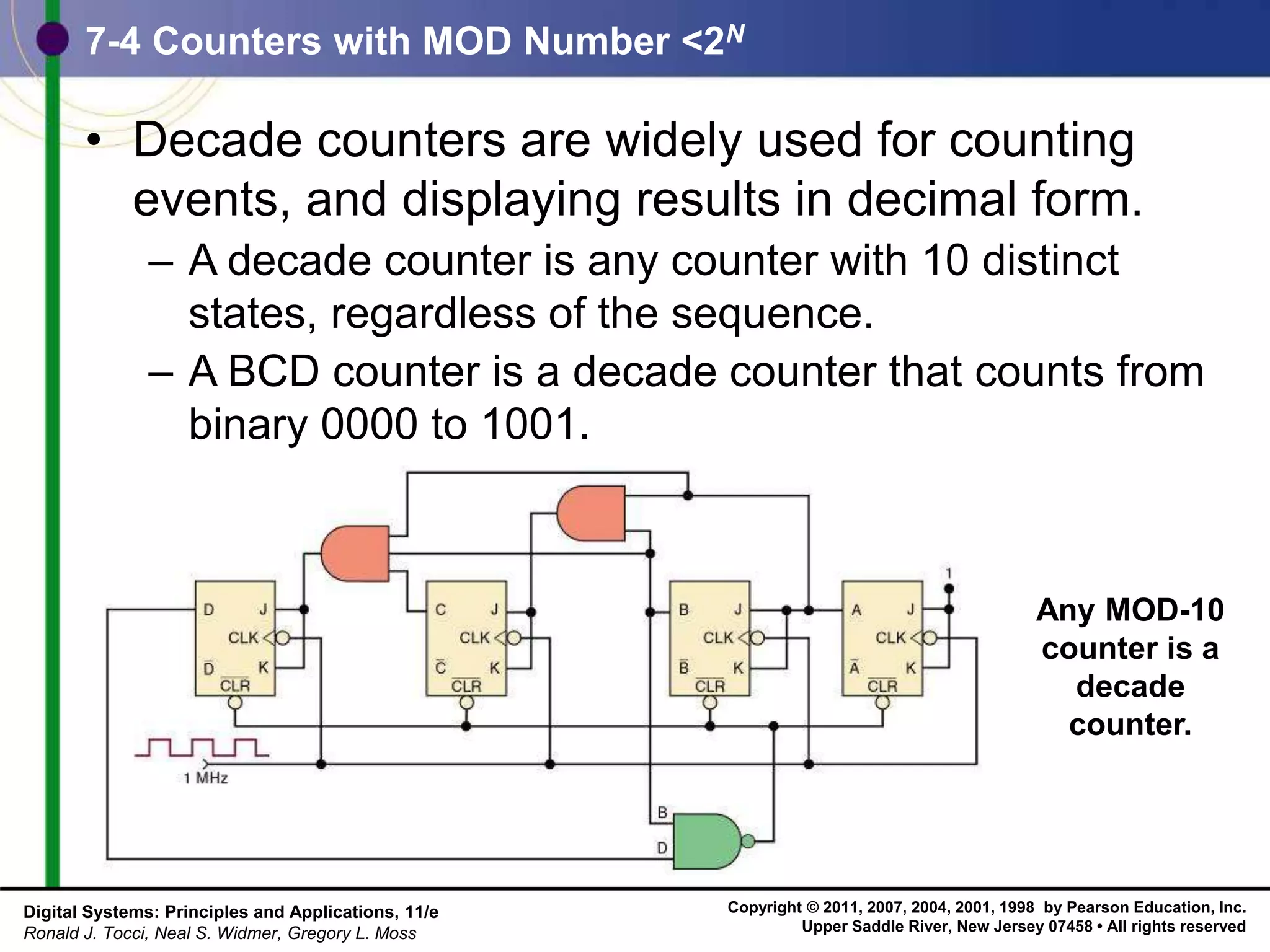

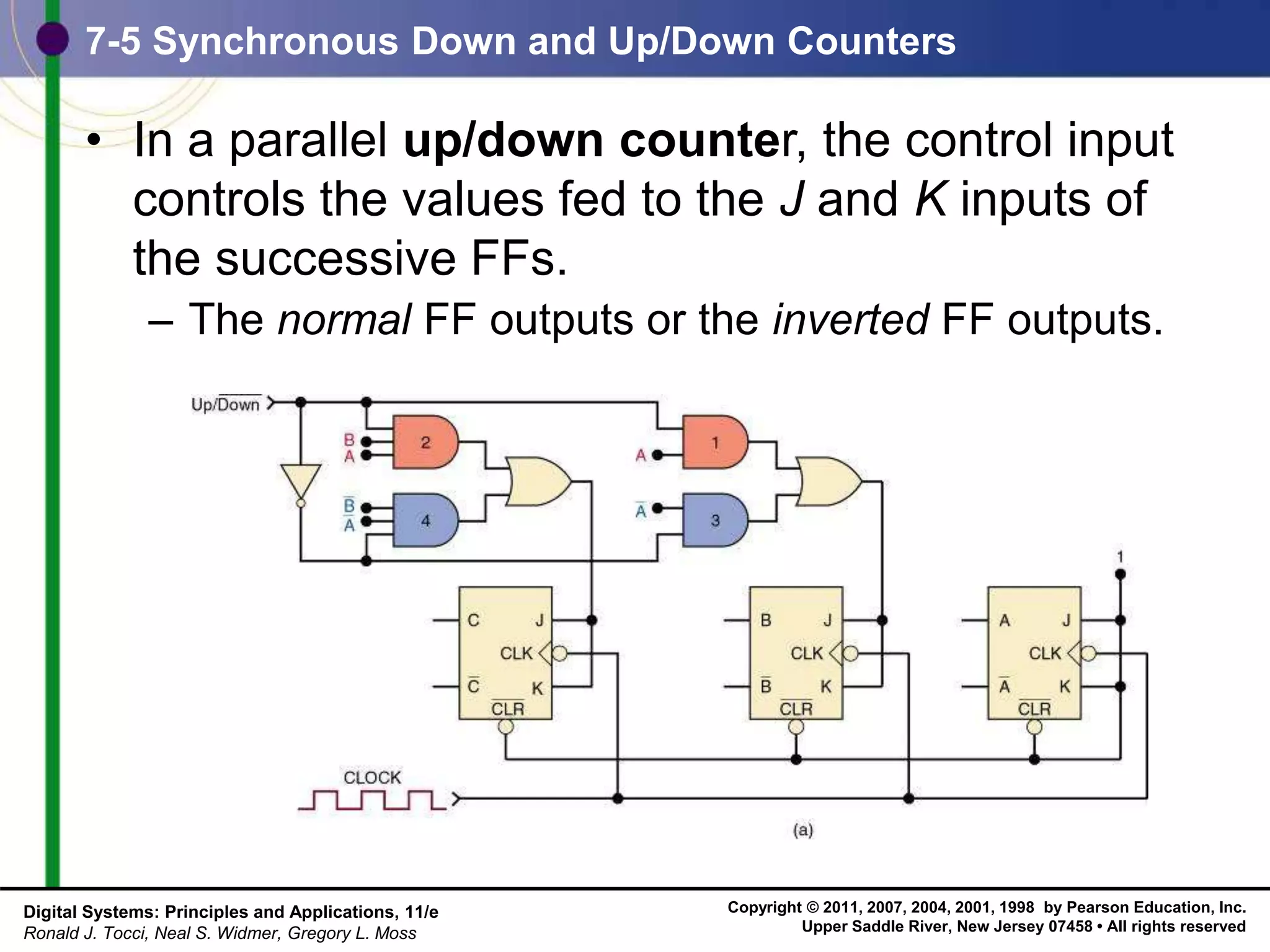

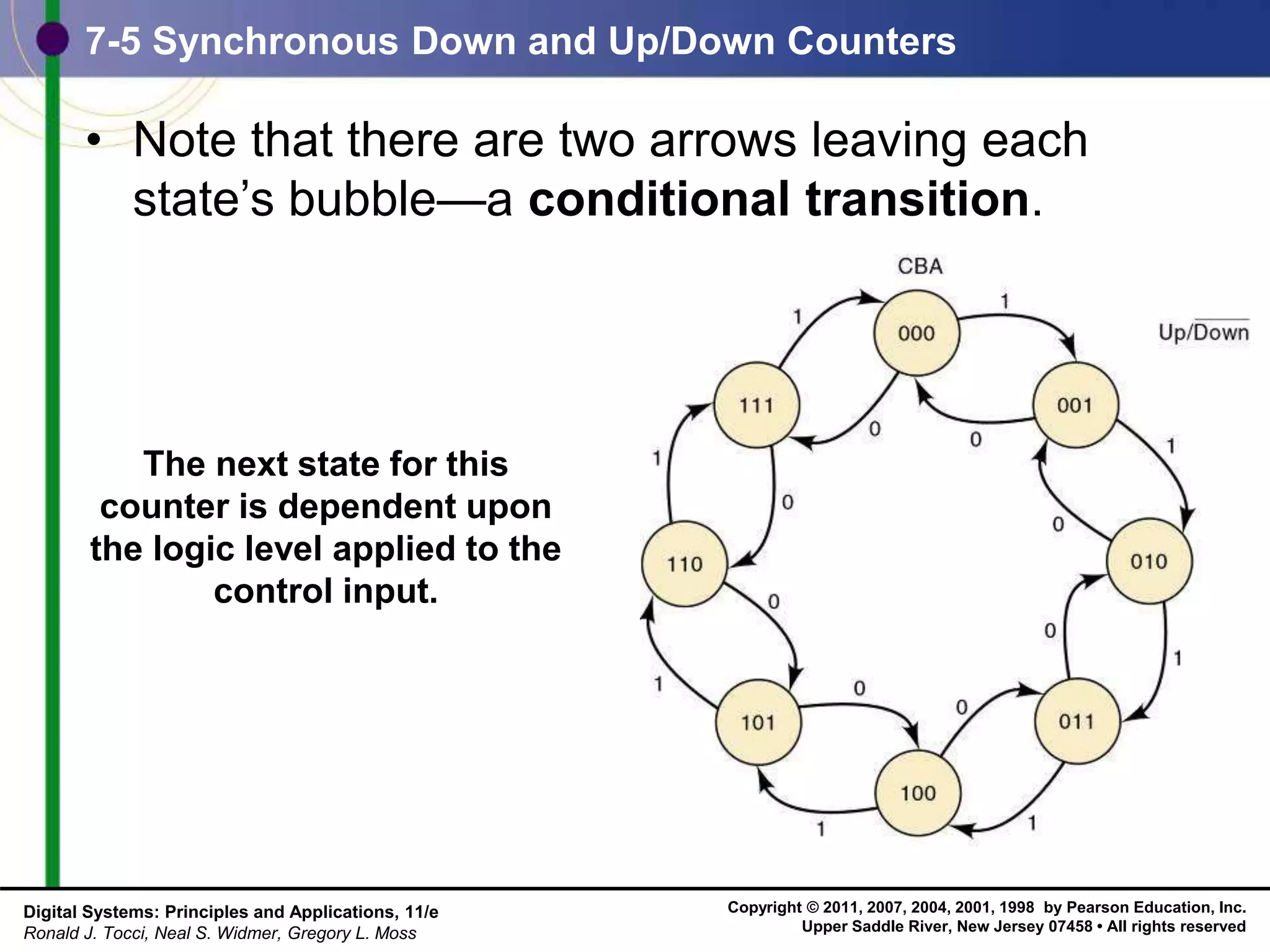

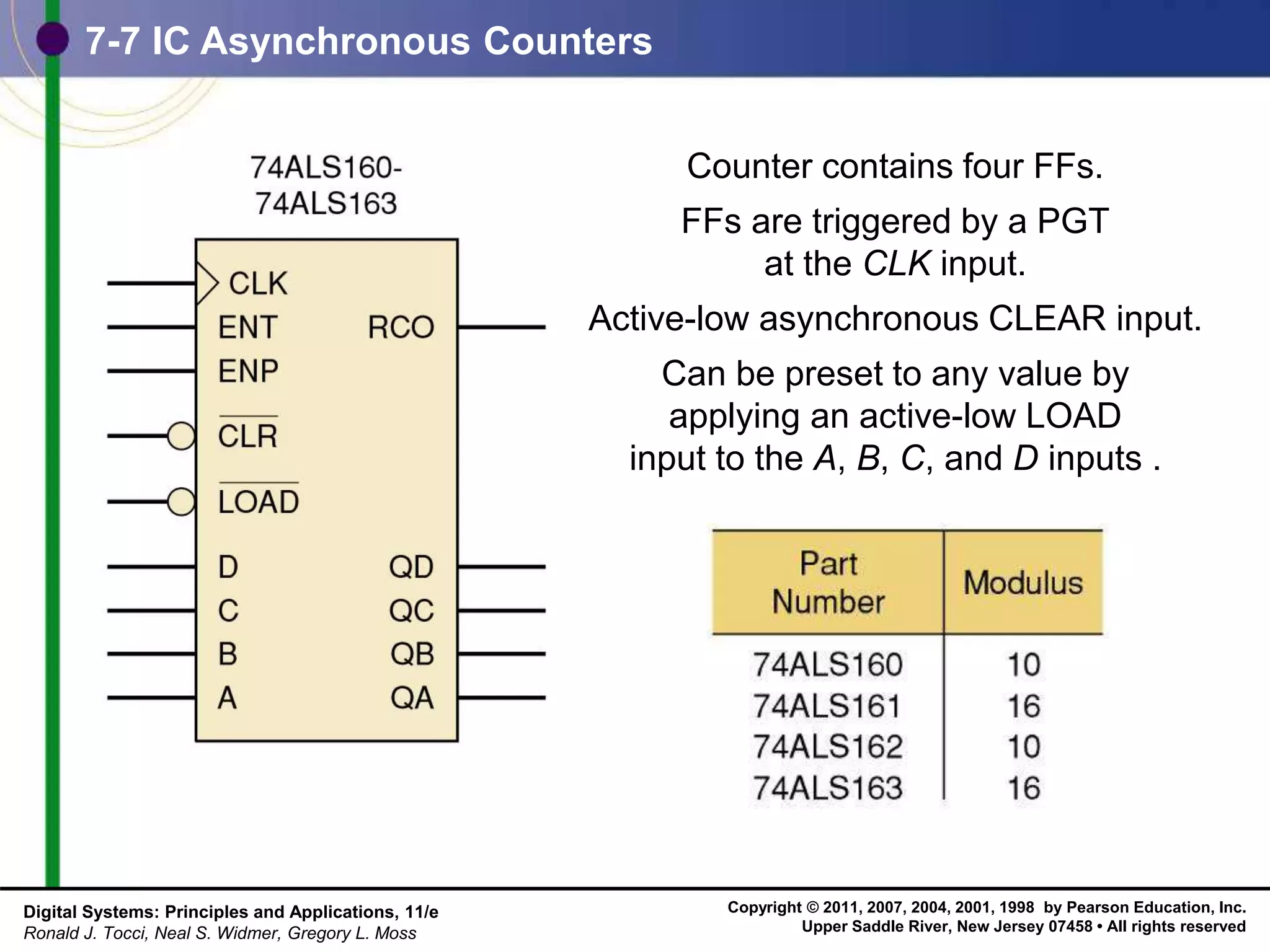

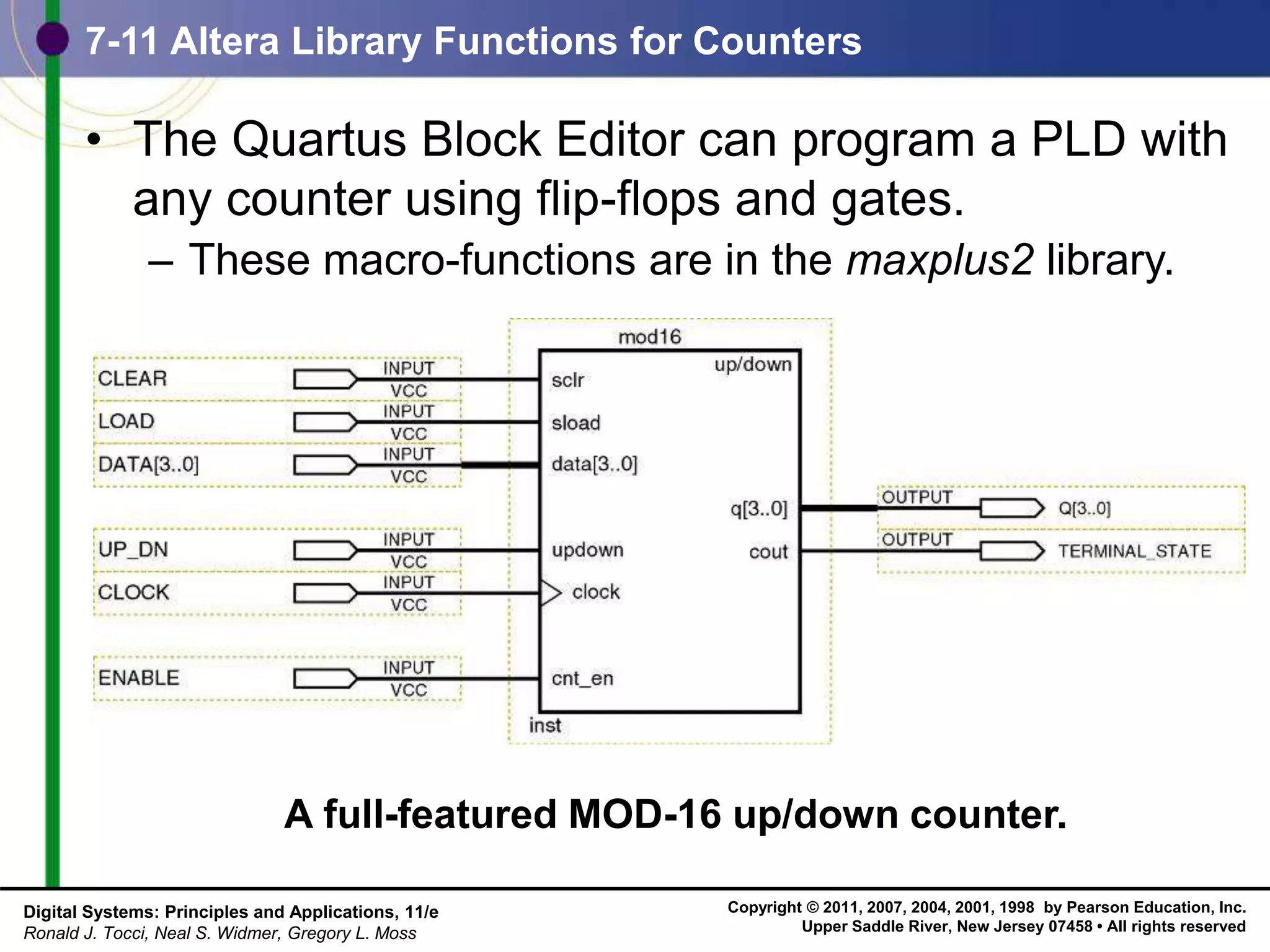

This document discusses digital counters and registers. It covers the operation of synchronous and asynchronous counters, analyzing different counter types, and implementing counters using HDL. It describes shift registers and using counters and registers to troubleshoot sequential logic systems. The document provides objectives for Chapter 7 and details asynchronous ripple counters, propagation delays, synchronous parallel counters, modifying counter MOD numbers, and IC-based asynchronous counters.

![Copyright © 2011, 2007, 2004, 2001, 1998 by Pearson Education, Inc.

Upper Saddle River, New Jersey 07458 • All rights reserved

Digital Systems: Principles and Applications, 11/e

Ronald J. Tocci, Neal S. Widmer, Gregory L. Moss

7-12 HDL Counters

• State descriptions in AHDL

The current state of the counter is evaluated (count[ ].q)

on line 11, and if it is less than the highest desired count

value, it uses the description count[ ].d count.q + 1 (line 12).](https://image.slidesharecdn.com/7countersregisters-230430222949-59df66d7/75/7Counters_registers-ppt-48-2048.jpg)