This document summarizes a research paper that presents a codec scheme to optimize power in VLSI interconnects using bus encoding. The scheme detects different types of crosstalk couplings between wires and encodes the data to reduce switching activity. It was implemented using Cadence tools in 0.18um technology. Simulation results found a maximum power of 6.44uW for an input combination, showing a 38.89% power reduction over previous work. The scheme models the full custom design approach instead of semi-custom.

![Int. Journal of Electrical & Electronics Engg. Vol. 2, Spl. Issue 1 (2015) e-ISSN: 1694-2310 | p-ISSN: 1694-2426

NITTTR, Chandigarh EDIT -2015 96

Codec Scheme for Power Optimization in

VLSI Interconnects

1

Dhriti Duggal,2

Rajnish Sharma

1,2

Chitkara University, Himachal Pradesh, India

1

dhriti.duggal@chitkarauniversity.edu.in, 2

rajnish.sharma@chitkarauniversity.edu.in

Abstract— This paper presents a codec scheme for optimizing

power in VLSI Interconnects. It is based on the traditional

bus encoding method which is considered to be one of the

most effective ways of power and delay reduction. The work

done aims at optimizing power by designing the scheme using

Full-Custom design approach. The model has been designed

and implemented using Cadence Virtuoso Analog Design

Suite in 0.18µm CMOS technology. Power has been computed

for different possible combinations of input data. Delay has

been reckoned for the maximum power consuming input

combination. Layout editor has been used to generate the

physical description of the circuit. The 4 bit input data

combination consuming maximum dynamic power of 6.44µW

and propagation delay of 722.7ps is “1000” with previously

transmitted 4 bit data being “0111”. A significant power

reduction of 38.89% has been observed by designing the

scheme using Full-Custom approach as compared to the

conventional Semi-Custom approach of design.

Keywords— Interconnects, Couplings, Power Dissipation,

Layout Implementation.

I. INTRODUCTION

For System on Chip (SOC) and Network on Chip (NOC)

designs in Deep Submicron era, interconnects play an

important role in the overall performance of the chip. They

are used to distribute clock and other signals and to provide

power/ground to and among the various circuits/systems

functions on the chip [1, 2]. Interconnects consume around

44% of the total chip area and hence it becomes very

important to estimate and minimize the power consumed

by them. Coupling Capacitance located between the wire

and its adjacent wires is important to analyze because it

slows down the signal. It can become the major component

of delay if the switching and coupling activities between

the group wires are not minimized. Further it may also lead

to Crosstalk and Signal Integrity related issues, which in

the worst of the cases may lead to the complete circuit

malfunction if not modeled properly [3-6]. There are

various methods to reduce the crosstalk, power

consumption and propagation delay but bus encoding

method is one of the most efficient methods [3]. It reduces

power consumption and crosstalk by bringing reduction in

the switching activity that is by reducing the number of

power consuming voltage transitions experienced by the

output capacitance/clock cycle.

Power consumption sources in digital CMOS circuits are

broadly classified into three main categories: static, short-

circuit and dynamic power dissipation [7]. Dynamic power

dissipation is one of the most dominant sources of power

dissipation in CMOS circuits which cannot be ignored.

Thus, to optimize power in any design successfully,

dynamic power has to be estimated and minimized

separately. The dissipated power is expressed as:

Pdiss = α* VDD

2

* fCLK* CL (1)

Where, CL is the load capacitance, VDD is supply voltage,

fCLK is the clock frequency and α is the average activity

factor or the switching factor whose value lies between 0

and 1. This paper focuses on bus encoding method for

reducing power dissipation of VLSI Interconnects by

reducing the switching activity.

The rest of the paper is organized as follows: Section II

discusses the types of couplings in interconnects. Section

III describes the implemented codec scheme. Results have

been discussed in Section IV and Section V concludes the

paper.

II. COUPLINGS IN INTERCONNECTS

The coupling between groups of three wires is classified

into five types depending upon the nature of transitions of

signals in the wires that are Type-0, Type-1, Type-2, Type-

3 and Type-4 as shown in Table 1 [3-6].

Table I. 3 bit bus couplings

TYPE-0 TYPE-1 TYPE-2 TYPE-3 TYPE-4

˗ ˗ ˗ ˗ ˗↑ ˗ ↑ ˗ ˗ ↑↓ ↑↓↑

↑↑↑ ˗↑↑ ↑↑ ˗ ˗ ↓↑ ↓↑↓

↓↓↓ ↑˗ ˗ ↑ ˗ ↓ ↑↓ ˗

↑↑˗ ↑↑↓ ↓↑ ˗

˗ ˗↓ ↑↓↓

˗↓↓ ˗ ↓ ˗

˗ ˗↓ ↓ ˗ ↓

↓↓ ˗ ↓ ˗ ↑

↓↓↑

↓↑↑

↑: transition from 0 to 1; ↓: transition from 1 to 0; ˗: no transition

Type-0 coupling occurs when all the 3 bit wires undergo

the same transition [1-2].Type-1 coupling occurs when

there is transition in one or maximum two wires (including

the centre one) while the third wire remains quite [1-

2].Type-2 coupling occurs when the centre wire is in the

opposite state transition with one of its adjacent wires

while the other wire undergoes the same state transition as

the centre wire [1-2]. Type-3 coupling occurs when the

centre wire undergoes the opposite state transition with one

of the two wires while the other wires are quite[1-2].Type-

4 coupling occurs when all the three wire transitions in the

opposite state with respect to each other[1-2].

III. IMPLEMENTED CODEC SCHEME

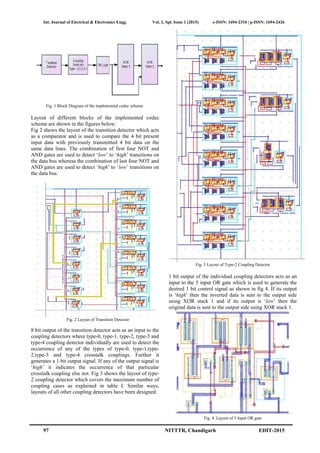

Fig 1 shows the block diagram of the implemented codec

scheme. Transition Detector compares the present 4 bit

input data with the previously transmitted 4 bit data.

Output of the transition detector acts as an input to the

coupling detectors which help in detecting crosstalk

couplings. XOR Stacks are used at both the encoder and

decoder side to transmit and receive data.](https://image.slidesharecdn.com/id111-150526193407-lva1-app6892/85/Codec-Scheme-for-Power-Optimization-in-VLSI-Interconnects-1-320.jpg)

![Int. Journal of Electrical & Electronics Engg. Vol. 2, Spl. Issue 1 (2015) e-ISSN: 1694-2310 | p-ISSN: 1694-2426

NITTTR, Chandigarh EDIT -2015 98

Fig 5 shows XOR Stack 1 which is used to transmit the

data to the decoder end according to the implemented logic

and the status of the control signal. A similar type of XOR

stack is used at the output end to decode the received

information depending upon the implemented logic and the

status of the control signal

Fig. 5 Layout of XOR Stack 1

IV. RESULTS AND DISCUSSION

The design has been implemented using Cadence Virtuoso

Analog Design Suite in 0.18µm technology. Virtuoso

layout editor has been used to generate the physical

description of the circuit. Table II highlights the total pre

and post layout power consumption of the implemented

codec scheme individually for all 16 possible combinations

of present and previous data. Power and delay results for

the maximum power consuming present and previous data

are shown in table III.

Table II. Total power results

Present

data

Previous

Data

Pre-layout

total power

consumption

(mW)

Post-layout total

power consumption

(mW)

0000 1111 2.705 3.190

0001 0000 1.521 1.590

0010 0001 1.851 2.072

0011 0010 1.521 1.590

0100 0011 2.542 2.929

0101 0100 1.521 1.590

0110 0101 1.849 2.082

0111 0110 1.519 1.592

1000 0111 2.937 3.508

1001 1000 1.521 1.592

1010 1001 1.849 2.082

1011 1010 1.521 1.592

1100 1011 2.540 2.917

1101 1100 1.521 1.582

1110 1101 1.848 2.074

1111 1110 1.521 1.586

Table III. Power and delay results for the worst combination

when present and previous data is “1000” and “0111”

Pre layout Post layout

Total power (mW) 2.937 3.508

Dynamic power (µW) 5.40 6.44

Total delay (ps) 402.4 722.7

Table IV shows the comparison of present work with

previously done work in terms of power consumption and

propagation delay.

TABLE IV. Comparison of present work with previous work

Parameter [1] Present Work

Power (µW) 10.54 6.44

Propagation Delay

(ps)

296 722.7

There is a significant improvement of 38.89% in power

consumption in the work done as compared to the previous

work. A codec scheme has been presented which focuses

mainly on reducing the switching and coupling activity so

as to reduce the power consumption. Modeling the

complete scheme using Full-Custom design approach has

been the focus point instead of using the traditional Semi-

Custom approach of design. Full-Custom design

methodology gives the liberty to the designer to specify the

layout of each and every transistor and the interconnections

between them. Whereas, in case of Semi-Custom designing

pre defined and pre characterized libraries are used, not

giving the privilege of complete customization to the

designer. Though there has been improvement in power

but increase in delay has been observed in the present work

as previous work focused the research on couplings

associated with either RC or RLC modeled interconnects.

In the present work, stress has been laid upon both of them

equally. The scheme has been designed for all types of

crosstalk couplings rather than focusing on only inductive

or resistive couplings in particular leading to a trade-off

between power and delay.

V. CONCLUSION

Codec Scheme implementation for optimizing power in

VLSI Interconnects has been presented. The pre and post

layout results have been compared. Also the comparison of

the present design has been done with the previously done

work in terms of power and propagation delay and a

significant improvement in dynamic power consumption

has been observed.

REFERENCES

[1]Deepika Agarwal, G. Nagendra Babu, B.K. Kaushik, S.K. Manhas,

“Reduction of Crosstalk in RC Modeled Interconnects with Low

Power Encoder” Emerging Trends in Networks and Computer

Communications (ETNCC),IEEE International Conference, pp. 115-

120, 2011.

[2]G. Nagendra Babu, Deepika Agarwal, B.K. Kaushik, S.K. Manhas,

Brijesh Kumar “Crosstalk avoidance in RLC modelled interconnects

using low encoder,” Recent advances in Intelligent Computational

Systems (RAICS),pp 921-924, 2011.](https://image.slidesharecdn.com/id111-150526193407-lva1-app6892/85/Codec-Scheme-for-Power-Optimization-in-VLSI-Interconnects-3-320.jpg)

![Int. Journal of Electrical & Electronics Engg. Vol. 2, Spl. Issue 1 (2015) e-ISSN: 1694-2310 | p-ISSN: 1694-2426

99 NITTTR, Chandigarh EDIT-2015

[3]Chih-Peng Fan and Chia-Hao Fang, “Efficient RC Low-power bus

encoding methods for Crosstalk reduction,” Integration VLSI Journal,

Elsevier, vol. 44, no. 1, pp. 75-86, Jan. 2011.

[4]M.R Stan, and W.P. Burleson, “Bus-Invert Coding for Low-power

I/O,” IEEE Trans. On Very Large Scale Integration System, vol.3, no.

1, pp. 49-58, March 1995.

[5]S.K. Verma and B.K. Kaushik, “A Bus Encoding Method for Crosstalk

and Power Reduction in RC Coupled VLSI Interconnects”

International Journal of VLSI design & Communication Systems

(VLSICS) Vol.3, No.2, April 2012, pp.29-39.

[6]S.K. Verma and B.K. Kaushik ,“Crosstalk and Power Reduction Using

Bus Encoding in RC Coupled VLSI Interconnects” Third International

Conference on Emerging Trends in Engineering and Technology

(ICETET), IEEE computer society, November 2010, pp.735-740.

[7]Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic,

“Digital Integrated Circuits,” 2nd

Edition, PrenticeHall Publication,

2003.](https://image.slidesharecdn.com/id111-150526193407-lva1-app6892/85/Codec-Scheme-for-Power-Optimization-in-VLSI-Interconnects-4-320.jpg)