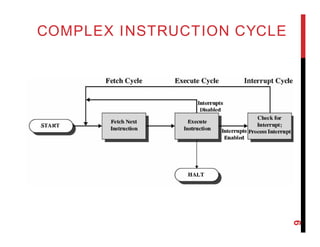

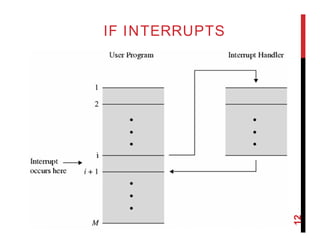

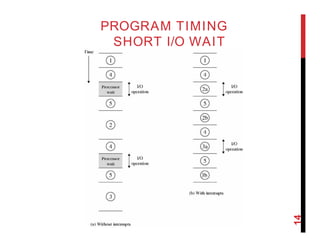

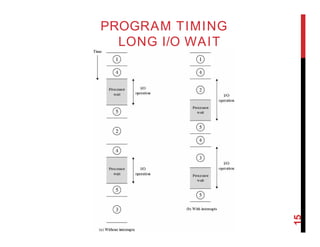

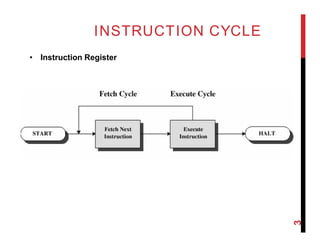

This document discusses various aspects of computer organization and assembly language. It covers the central processing unit including the register set, arithmetic logic unit, control unit, and data path. It also describes different instruction cycle models and bus organizations such as one-bus, two-bus, and three-bus. Interrupts and how they allow other modules to interrupt normal program processing are explained. The control unit and how it manages computer resources through control and timing signals is covered. Microprogrammed and hardwired control unit designs are compared.

![INSTRUCTION CYCLE EXAMPLES

• MOV AL,5

• ADD AL,[003]

8](https://image.slidesharecdn.com/coal-10instructioncycleandinterrupts-140729101225-phpapp01/85/Coal-10-instruction-cycle-and-interrupts-in-Assembly-Programming-8-320.jpg)