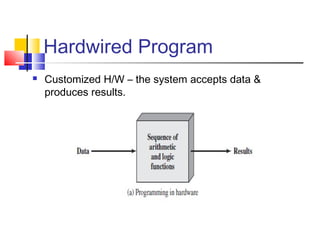

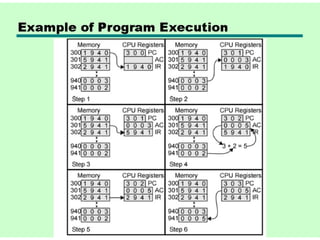

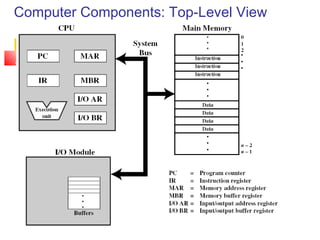

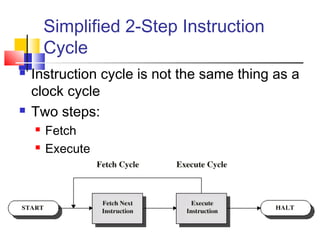

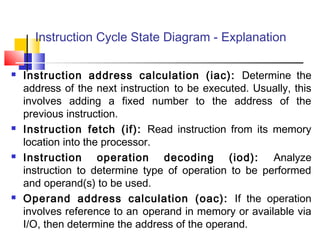

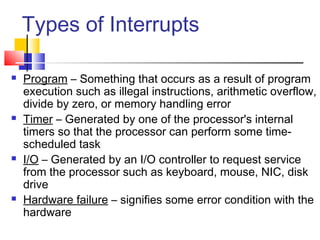

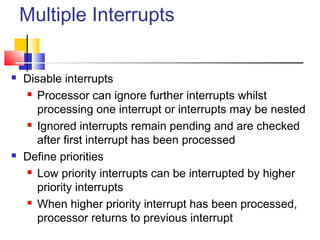

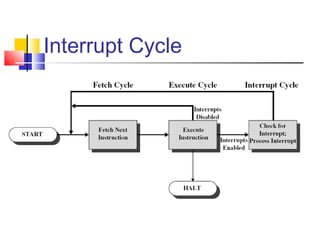

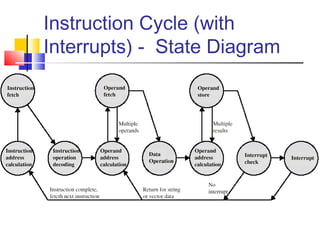

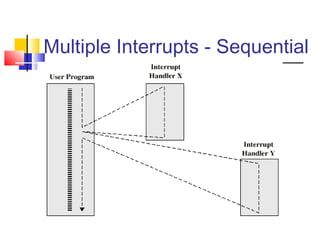

This document discusses the basic components and functions of a computer system with a single processor architecture. It covers the von Neumann architecture, hardwired programs, instruction interpretation, the fetch-execute cycle, interrupts and how they are handled, I/O functions, and different structures for interconnecting computer components.