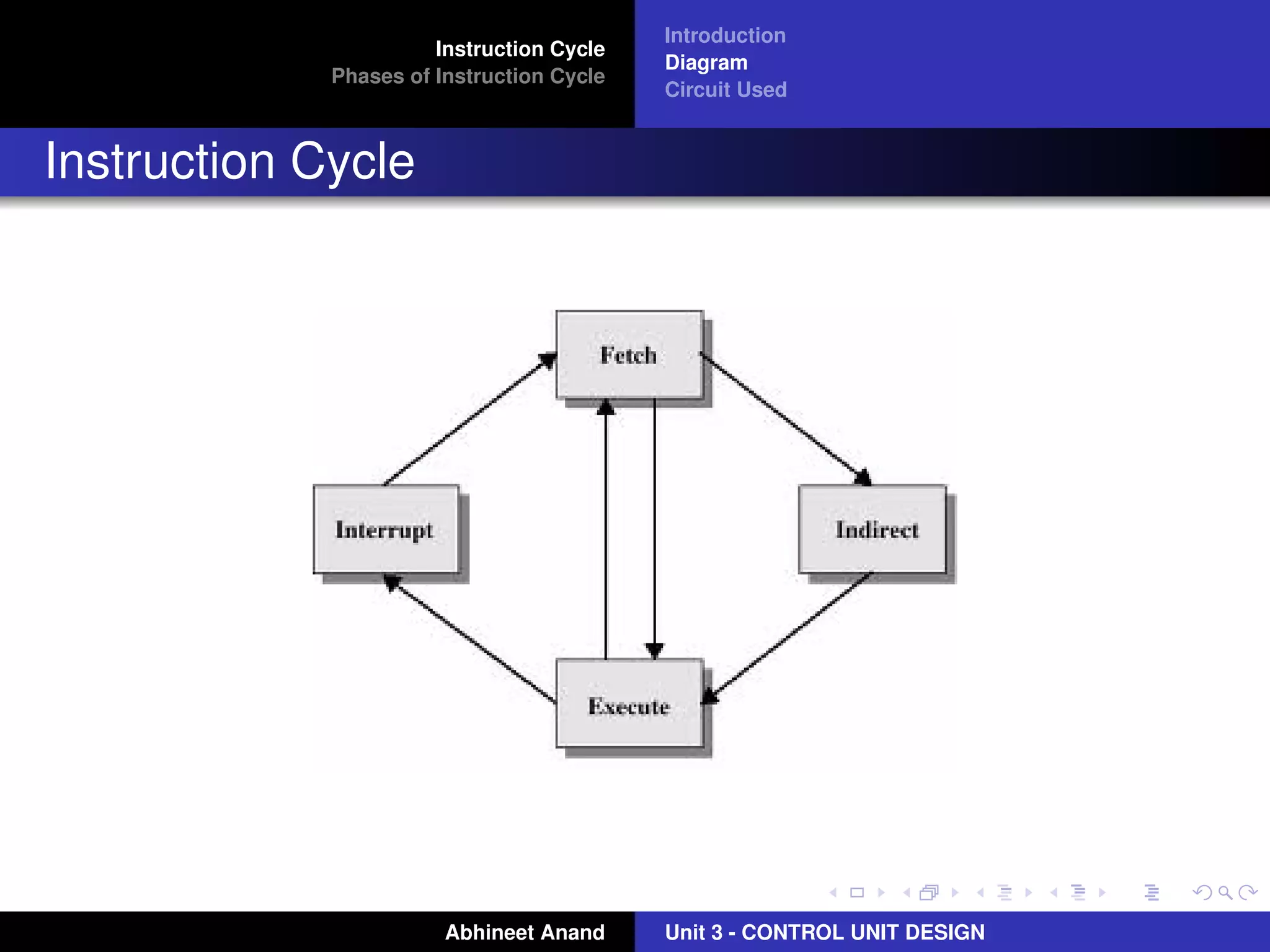

The document describes the phases of the instruction cycle in a CPU. It discusses the following phases: 1) Fetch - the next instruction is fetched from memory and stored in the instruction register using the program counter; 2) Decode - the instruction inside the register is decoded; 3) Execute - the control unit passes signals to function units like the ALU to perform the required actions like arithmetic or logic operations. It also describes common circuits used in a CPU like the program counter, memory address register, and instruction register.

![Instruction Cycle

Phases of Instruction Cycle

Fetching the instruction

Decode the instruction

In case of a memory instruction

Execute the instruction

The Fetch Execute cycle in Transfer Notation

Expressed in register transfer notation:

MAR <- PC

MDR<- Memory {MAR address}; PC <- [PC]+1 (Increment

the PC for next cycle at the same time)

IR<- MDR

Abhineet Anand

Unit 3 - CONTROL UNIT DESIGN](https://image.slidesharecdn.com/instructioncycle-140206030943-phpapp01/75/Instruction-cycle-11-2048.jpg)