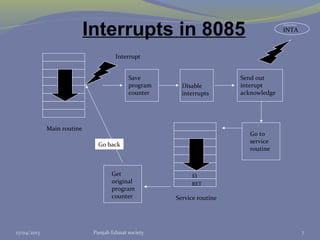

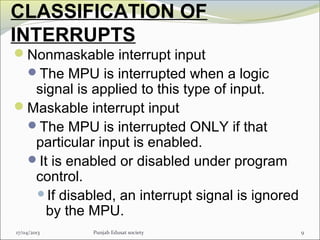

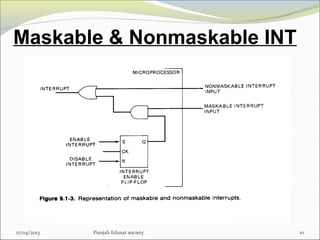

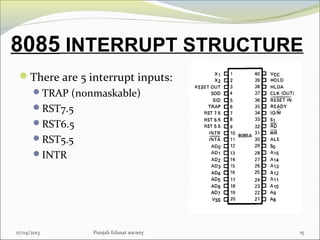

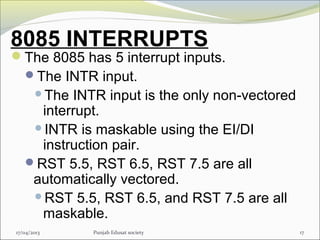

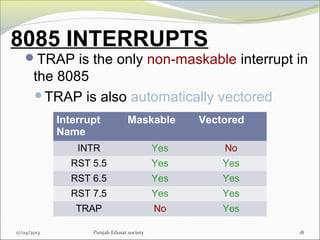

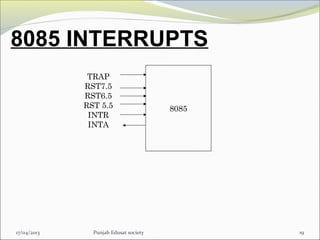

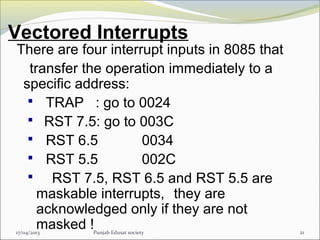

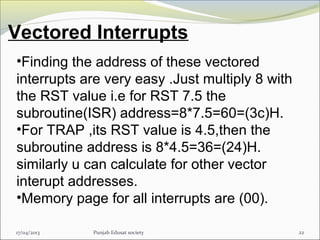

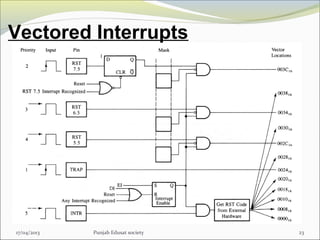

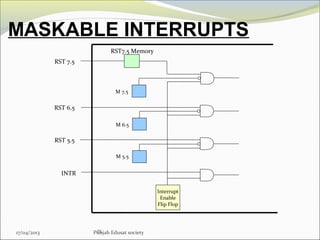

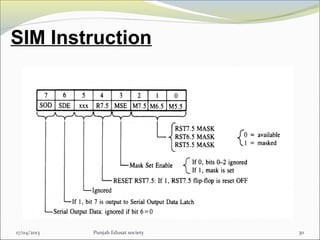

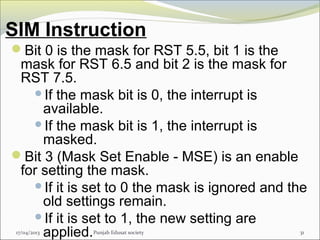

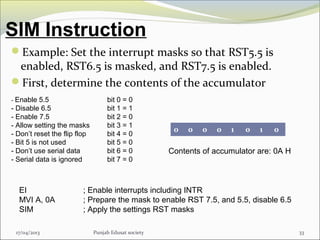

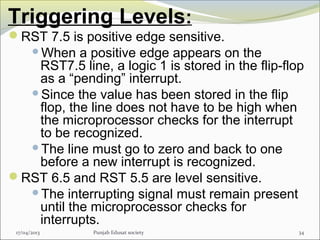

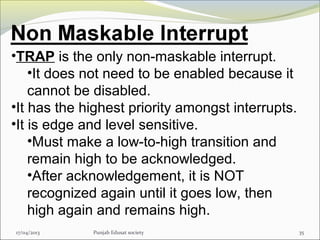

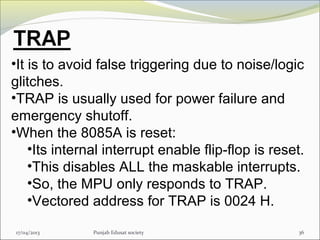

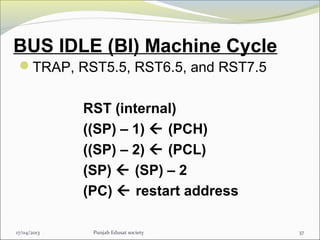

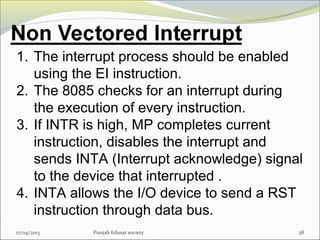

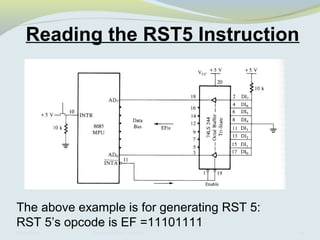

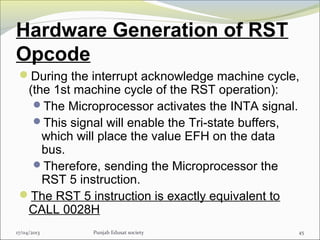

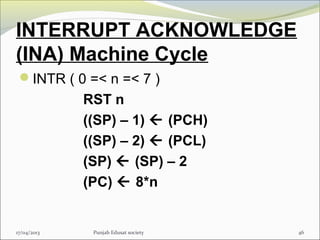

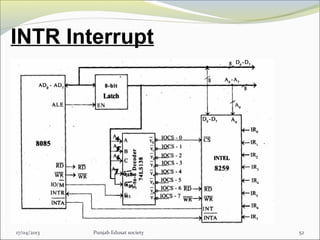

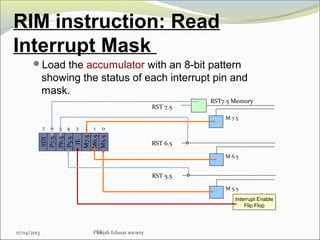

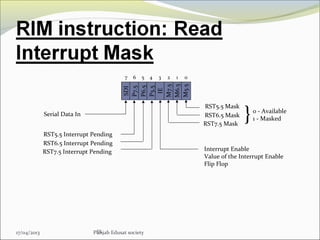

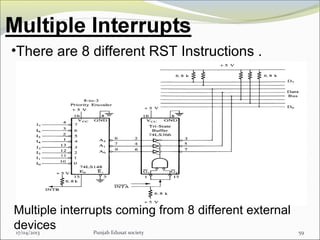

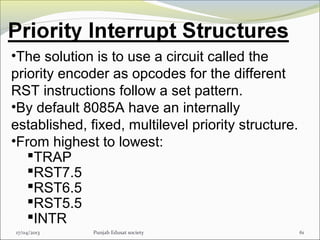

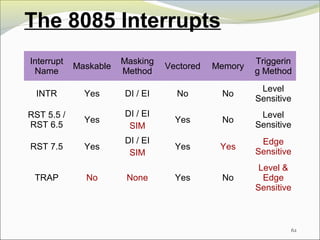

The document discusses interrupts in the 8085 microprocessor. It describes how interrupts work, including how the 8085 handles different types of interrupts like maskable, non-maskable, vectored and non-vectored interrupts. It provides details on the interrupt handling process, interrupt priorities, the interrupt mask and how individual interrupts can be enabled or disabled.