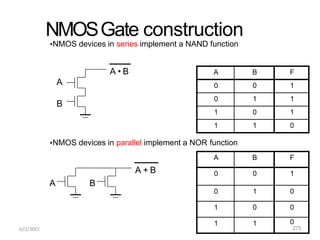

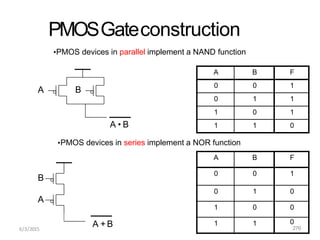

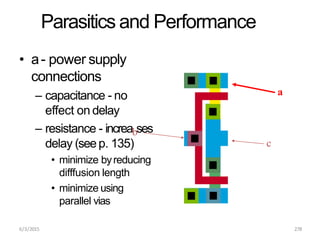

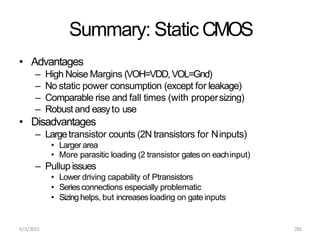

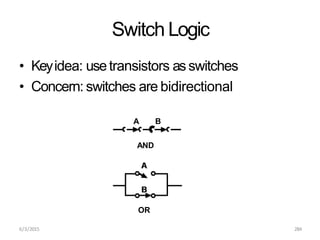

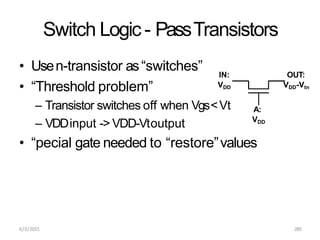

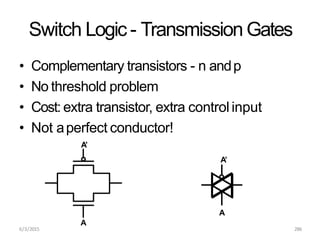

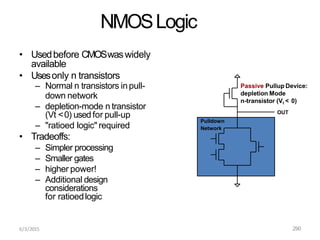

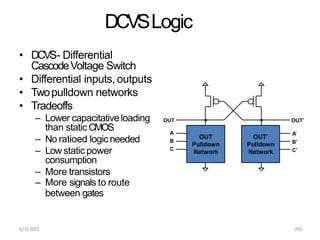

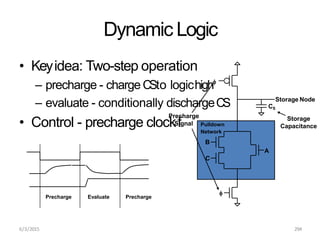

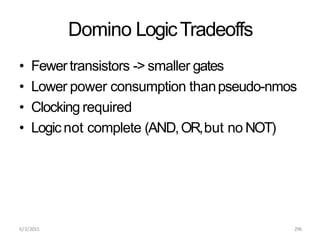

The document discusses various topics in digital logic design, focusing on CMOS, NMOS, and PMOS gate constructions and their corresponding implementations such as NAND and NOR functions. It also addresses the impact of parasitics on performance, challenges in driving large capacitive loads, and alternatives to static CMOS logic, including switch logic, dynamic logic, and pseudo-NMOS. Additionally, trade-offs between power consumption, noise margins, and transistor counts are analyzed throughout the document.