Combinational Logic Circuits (1).pptx

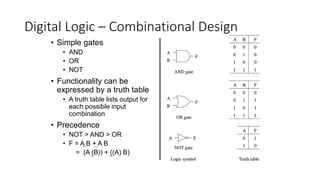

- 1. Digital Logic – Combinational Design • Simple gates • AND • OR • NOT • Functionality can be expressed by a truth table • A truth table lists output for each possible input combination • Precedence • NOT > AND > OR • F = A B + A B = (A (B)) + ((A) B)

- 2. Basic Concepts (cont.) • Additional useful gates • NAND • NOR • XOR • NAND = AND + NOT • NOR = OR + NOT • XOR implements exclusive- OR function • NAND and NOR gates require only 2 transistors • AND and OR need 3 transistors!

- 3. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Floyd, Digital Fundamentals, 10th ed The XOR gate produces a HIGH output only when the inputs are at opposite logic levels. The truth table is The XOR Gate 0 0 0 1 1 0 1 1 0 1 1 0 A B X A B X The XOR operation is written as X = AB + AB. Alternatively, it can be written with a circled plus sign between the variables as X = A + B. XOR and XNOR Gates

- 4. Digital Logic Design using MOS • An nMOS transistor can be modelled as a switch connected between the drain (D) and source (S) and the switch is controlled by gate (G). • nMOS as a Switch • When the Gate (G) is Logic High (H), • the nMOS is ON • the switch is closed • D is connected to S • When the Gate is Logic Low (L), • the nMOS is OFF • the switch is open • D is disconnected from S. • An nMOS can pass the logic low (Gnd) perfectly but cannot pass logic high perfectly. • pMOS as a Switch • When the Gate (G) is Logic Low (L), • the pMOS is ON • the switch is closed • D is connected to S. • When the gate is Logic HIGH (H), • the pMOS is OFF • the switch is open • D is disconnected from S. • A pMOS can pass logic high (VDD) perfectly but cannot pass logic low perfectly. nMOS as a Switch pMOS as a Switch pMOS (VGS) Logic 0: ON Logic 1: OFF nMOS (VGS) Logic 0: OFF Logic 1: ON

- 5. CMOS Design Methodology • Logic Design using CMOS Logic: For a given Boolean Expression, the basic CMOS design methodology involves three steps: • Step1: Take the complement of Boolean Expression • Step2: Design PDN by realizing • AND terms using series- connected nMOS • OR terms using parallel- connected nMOS • Step3: Design PUN just reverse (or dual) of the PDN • For Ex: NOT-AND (NAND) & NOT-OR (NOR) Logic

- 6. Design of CMOS Inverter (NOT) Gate • CMOS Inverter • A CMOS inverter is the simplest logic circuit that uses one nMOS and one pMOS transistor. The nMOS is used in PDN and the pMOS is used in the PUN. • When input is LOW, the nMOS is OFF and the pMOS is ON. Hence, the output is connected to VDD through pMOS. • When the input is HIGH, the nMOS is ON and the pMOS is OFF. Hence, the output is connected to the GND through nMOS. • Load Capacitor • A capacitor is connected at the output node to represent the load seen by the inverter. • The load capacitor is charged to VDD through pMOS when the input is low and is discharged to the GND through nMOS when the input is high.

- 7. Design of Two-Input NAND Gate • Two input NAND Gate design using CMOS Inverters, • Step 1: Take Complement of Y, • Step 2: Design the PDN. • In this case, there is only one AND term. • So, there will be two nMOS in series. • Step 3: Design the PUN. • In PUN, there will be two pMOS in parallel. Practice Example

- 8. Design of Two-Input NOR Gate Practice Example

- 9. Practice Examples • Question: Find the Output of the following CMOS Logic Gates. OUT= [(A.B)+C+D]’ VDD OUT= [(A.B)+C]’ F OUT= (A.B.C.D)’ Output C= (A.B)’ Output C= (A+B)’