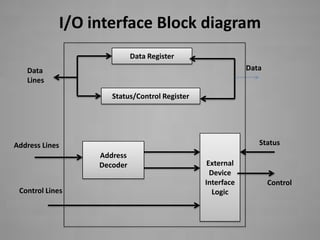

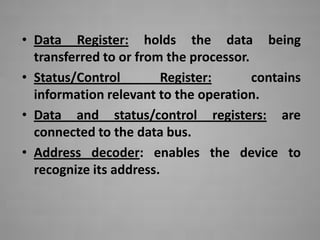

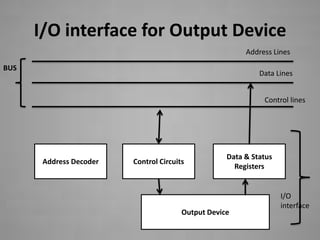

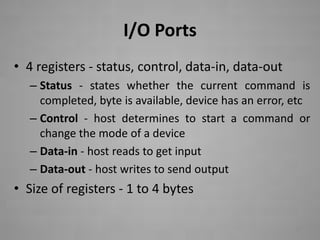

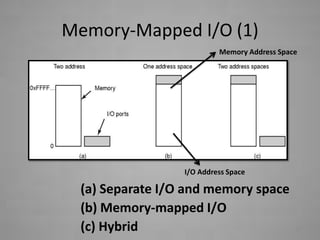

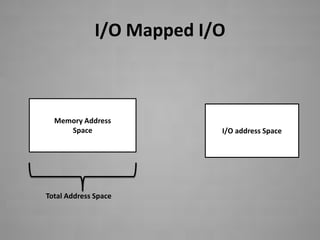

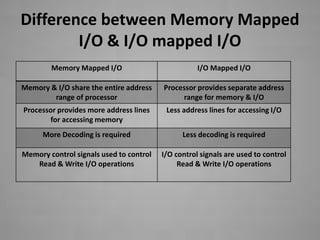

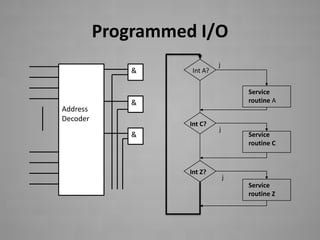

The document discusses input/output (I/O) interfaces. An I/O interface is required for communication between the CPU, I/O devices, and memory. It performs data buffering, control and timing, and error detection. There are two main techniques for I/O interfacing - memory mapped I/O and I/O mapped I/O. Programmed I/O is an approach where the CPU polls I/O devices by checking their status periodically to see when operations complete.