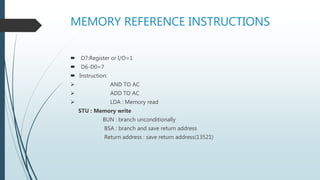

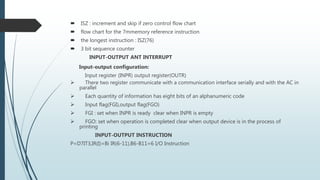

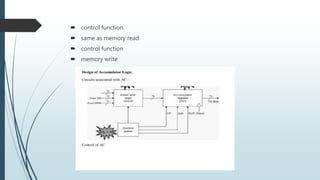

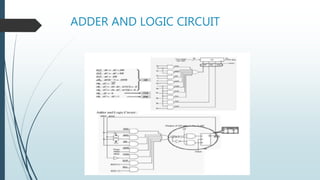

This document provides an overview of basic computer organization and design. It discusses memory reference instructions, input/output and interrupts, and the design of a basic computer. The computer consists of a memory unit, nine registers, flags, decoders, buses, and control logic. It describes the control functions for memory reading and writing, register selection, flag manipulation, and arithmetic operations using an adder and logic circuit. The document aims to provide a complete description of the basic components and design of a computer system.