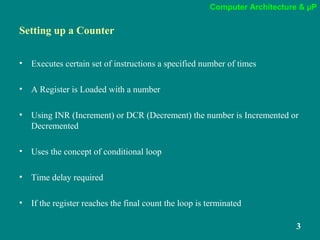

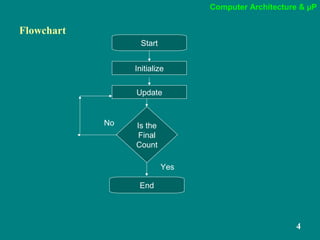

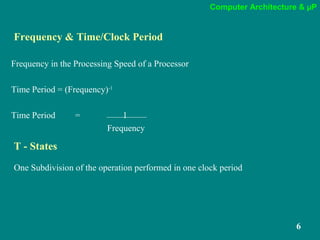

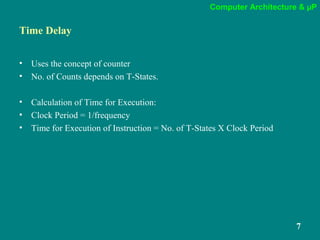

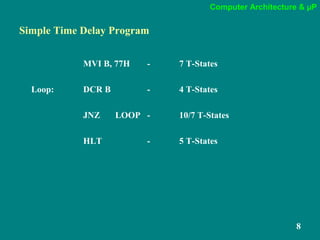

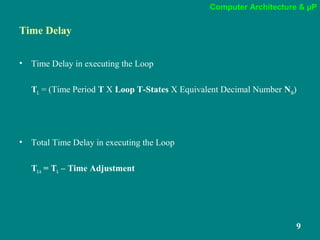

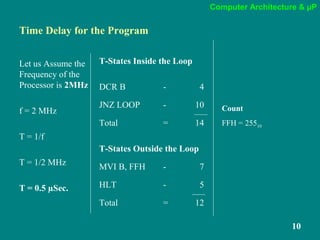

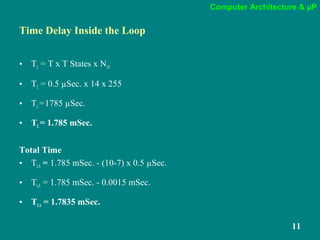

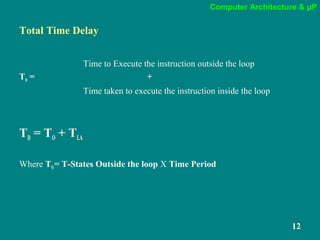

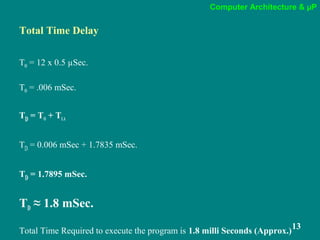

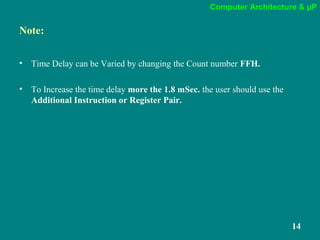

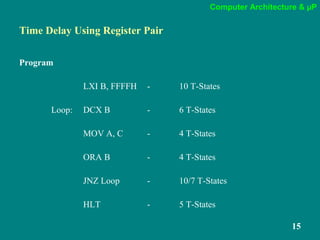

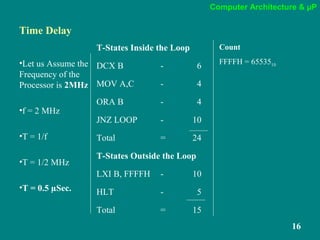

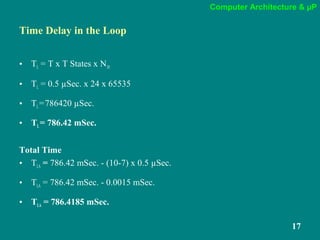

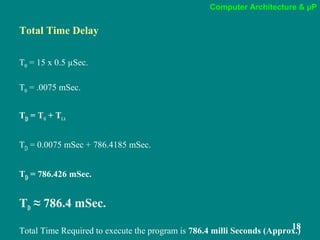

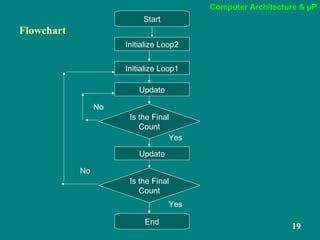

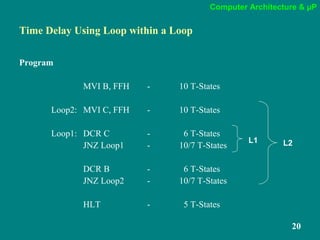

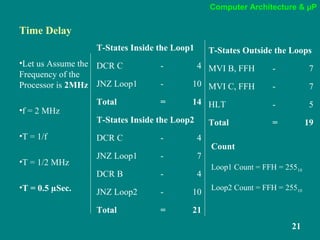

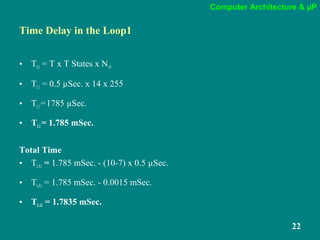

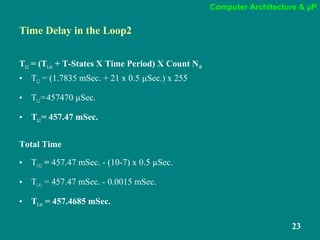

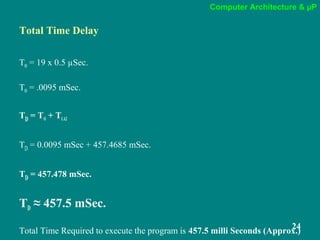

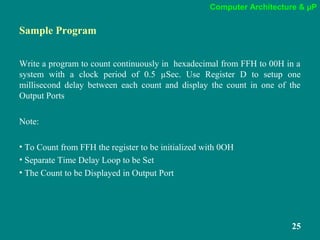

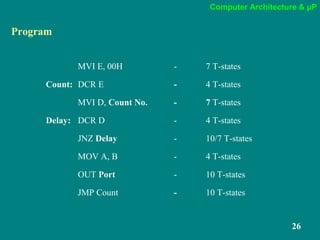

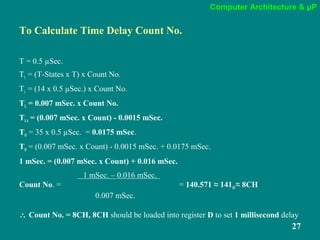

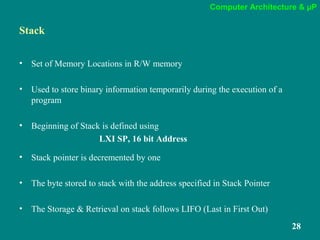

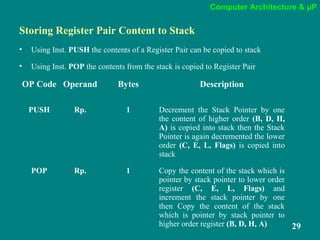

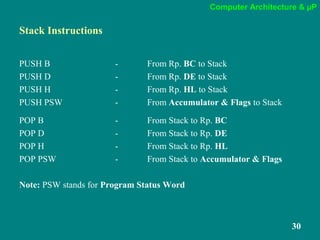

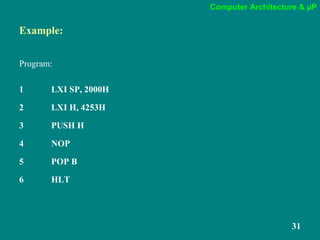

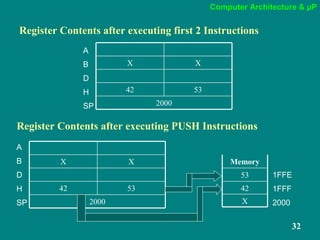

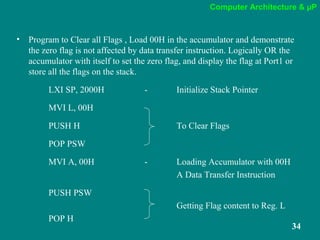

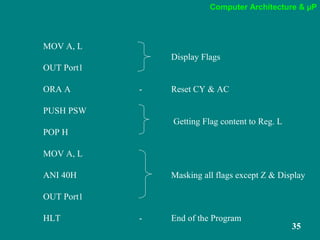

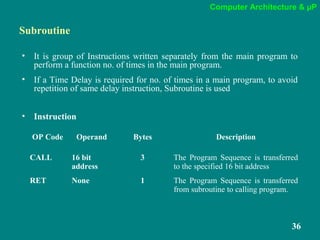

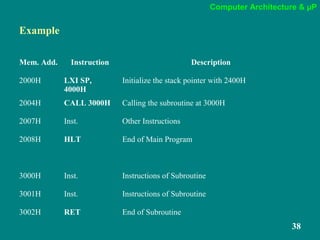

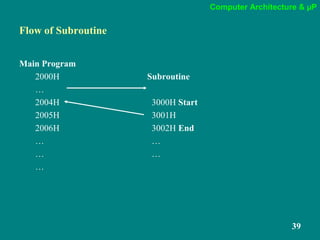

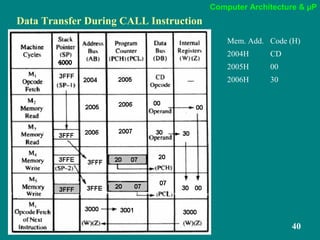

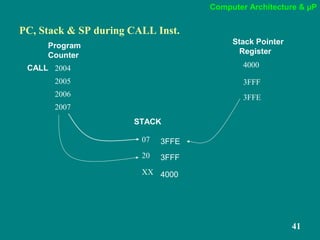

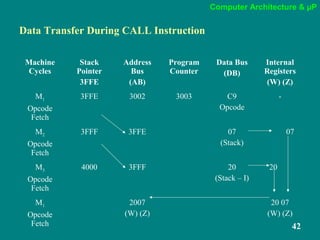

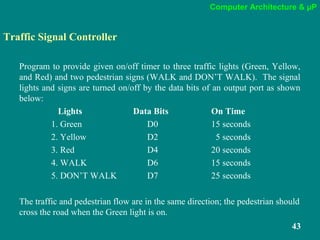

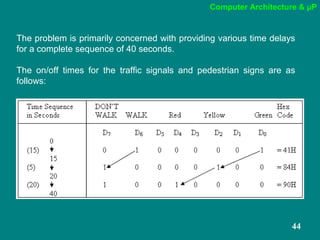

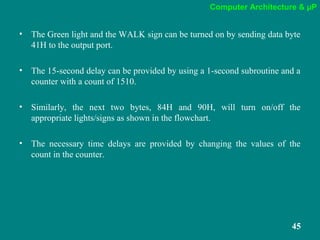

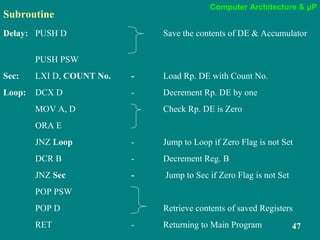

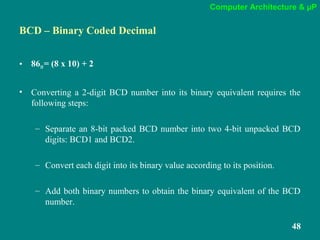

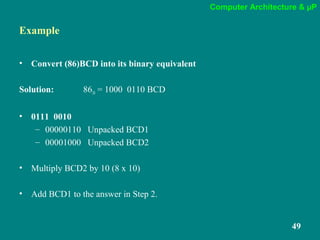

This document discusses computer architecture and microprocessors. It explains how to set up a counter using a register loaded with a number that is then incremented or decremented. It discusses time delay, which uses a counter concept where the number of clock cycles depends on T-states. A simple example program is provided and calculated to take 1.8 milliseconds to execute based on a 2MHz processor frequency. Additional examples are given to illustrate using register pairs or nested loops to create longer time delays. The document also covers stacks, stack instructions, and using subroutines to avoid repeatedly writing time delay code.