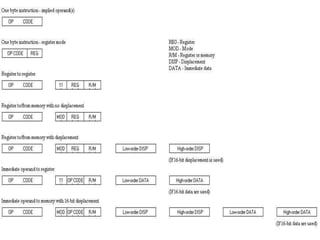

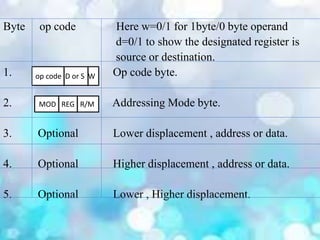

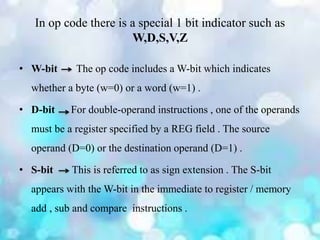

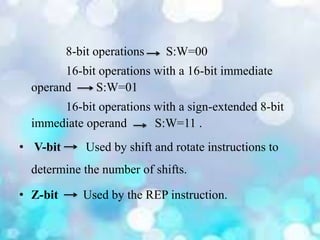

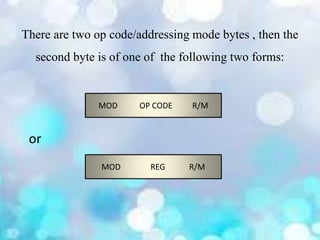

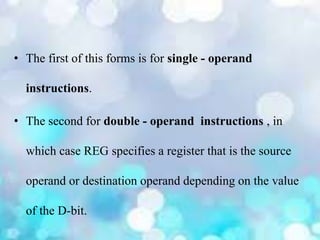

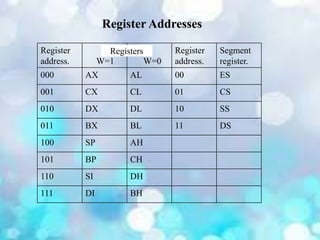

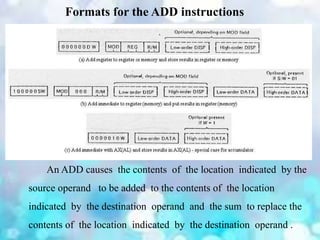

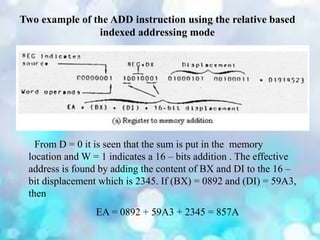

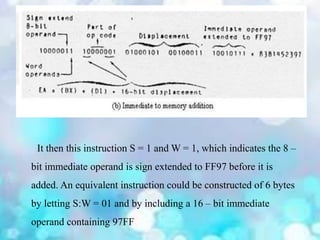

The document summarizes the instruction formats used by the 8086 microprocessor. It discusses the different parts of an instruction, including the opcode, addressing mode byte, registers, and displacement fields. It explains that instructions can be 1 to 7 bytes long depending on the addressing mode. Several examples of ADD instructions are provided to illustrate how the different fields specify the operands and destination.

![MICROCOMPUTER

ARCHTECTURE

INSTRUCTION

FORMATS

PRESENTED BY

M.LAVANYA

M.sc[CS&IT]

NSCAS.](https://image.slidesharecdn.com/instructionformats-170826051305/85/microcomputer-architecture-Instruction-formats-1-320.jpg)