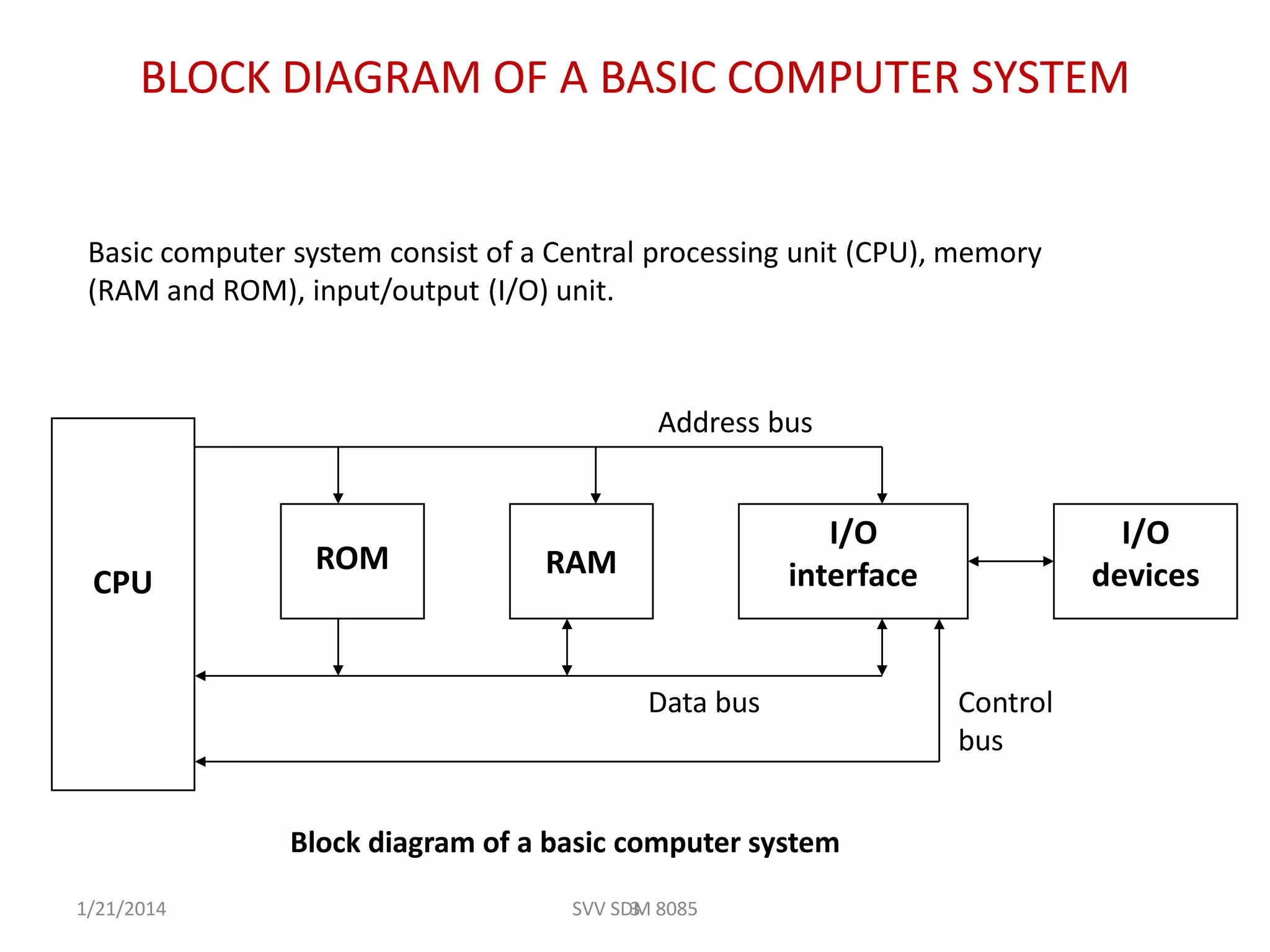

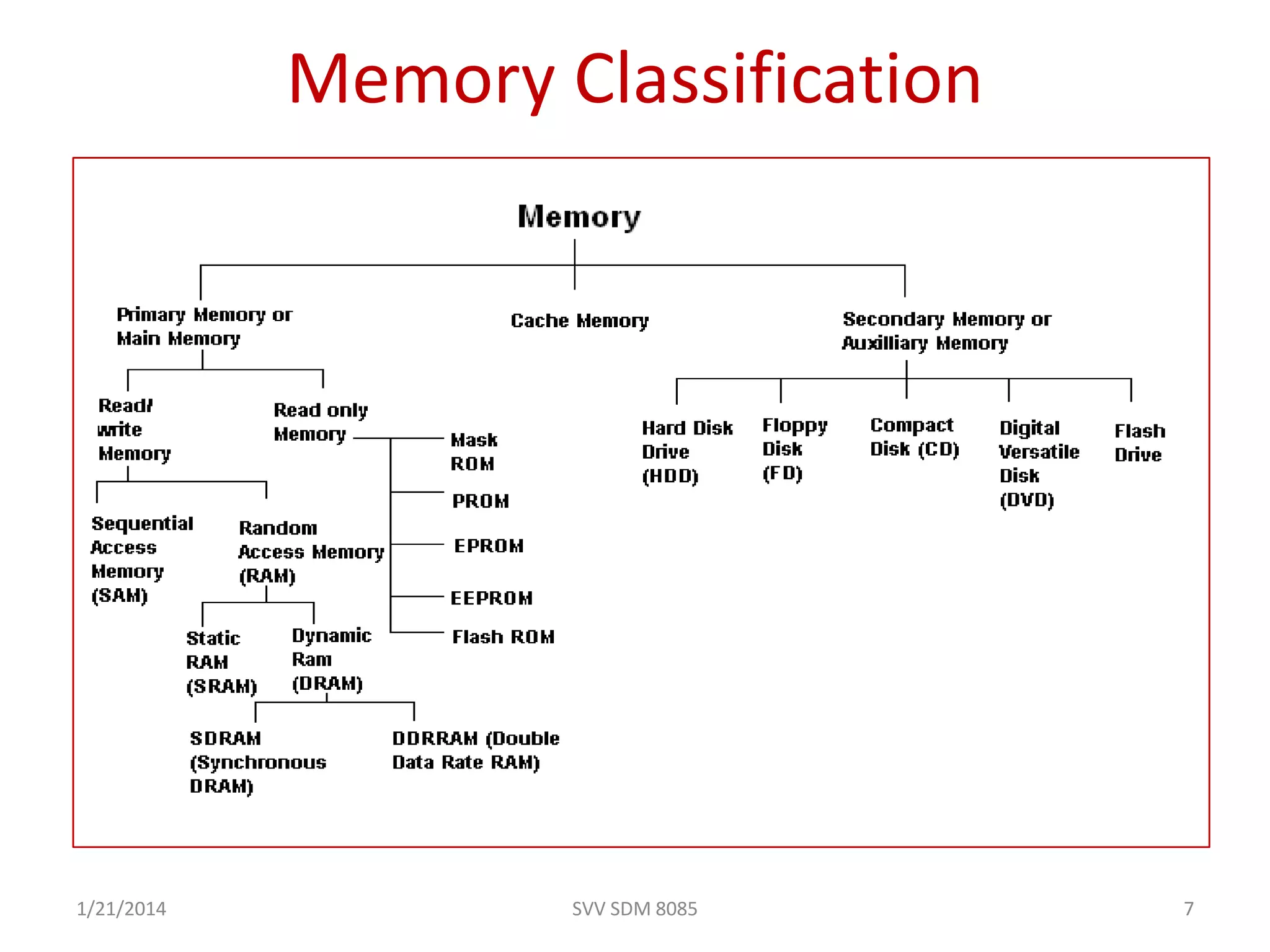

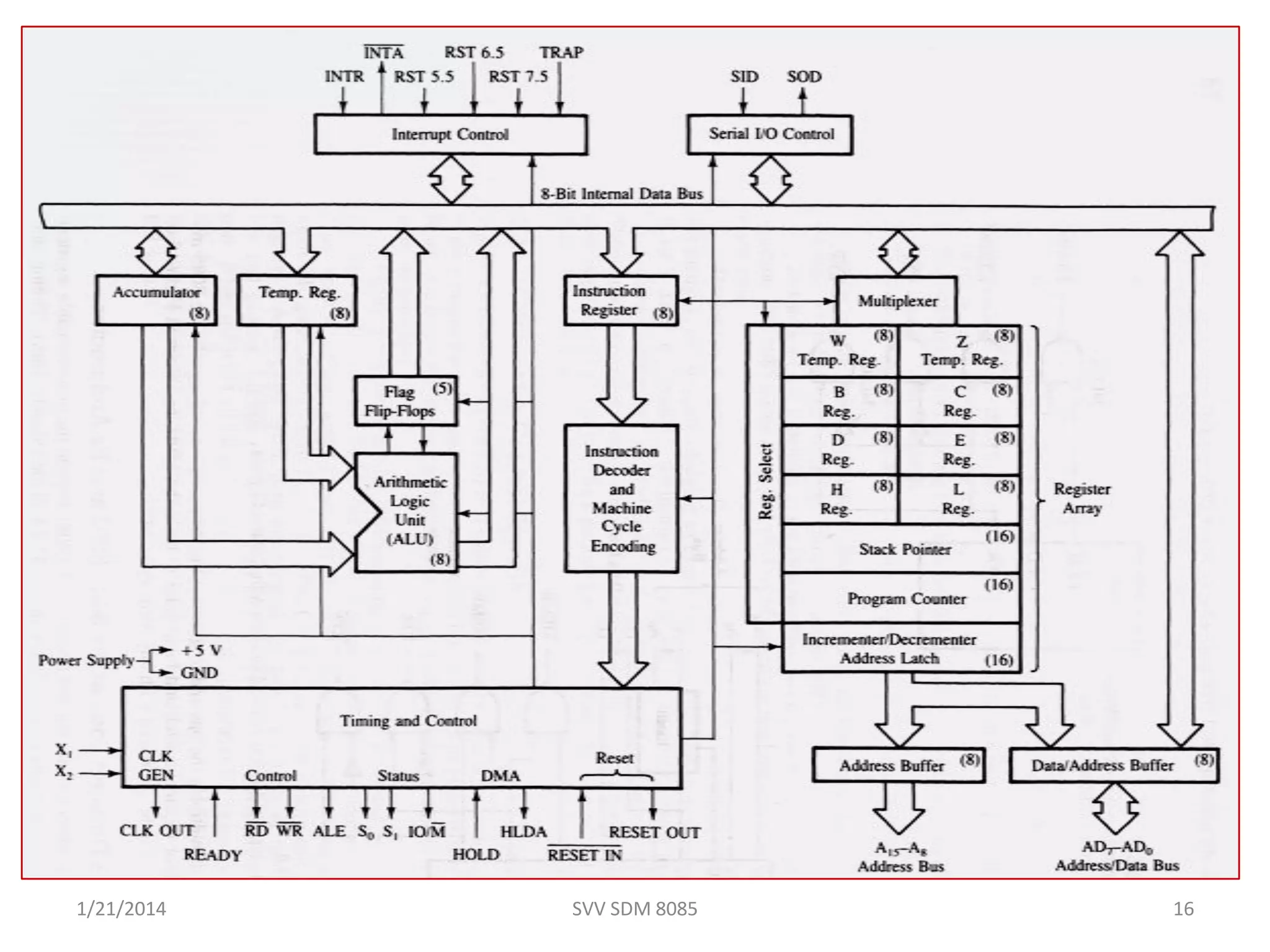

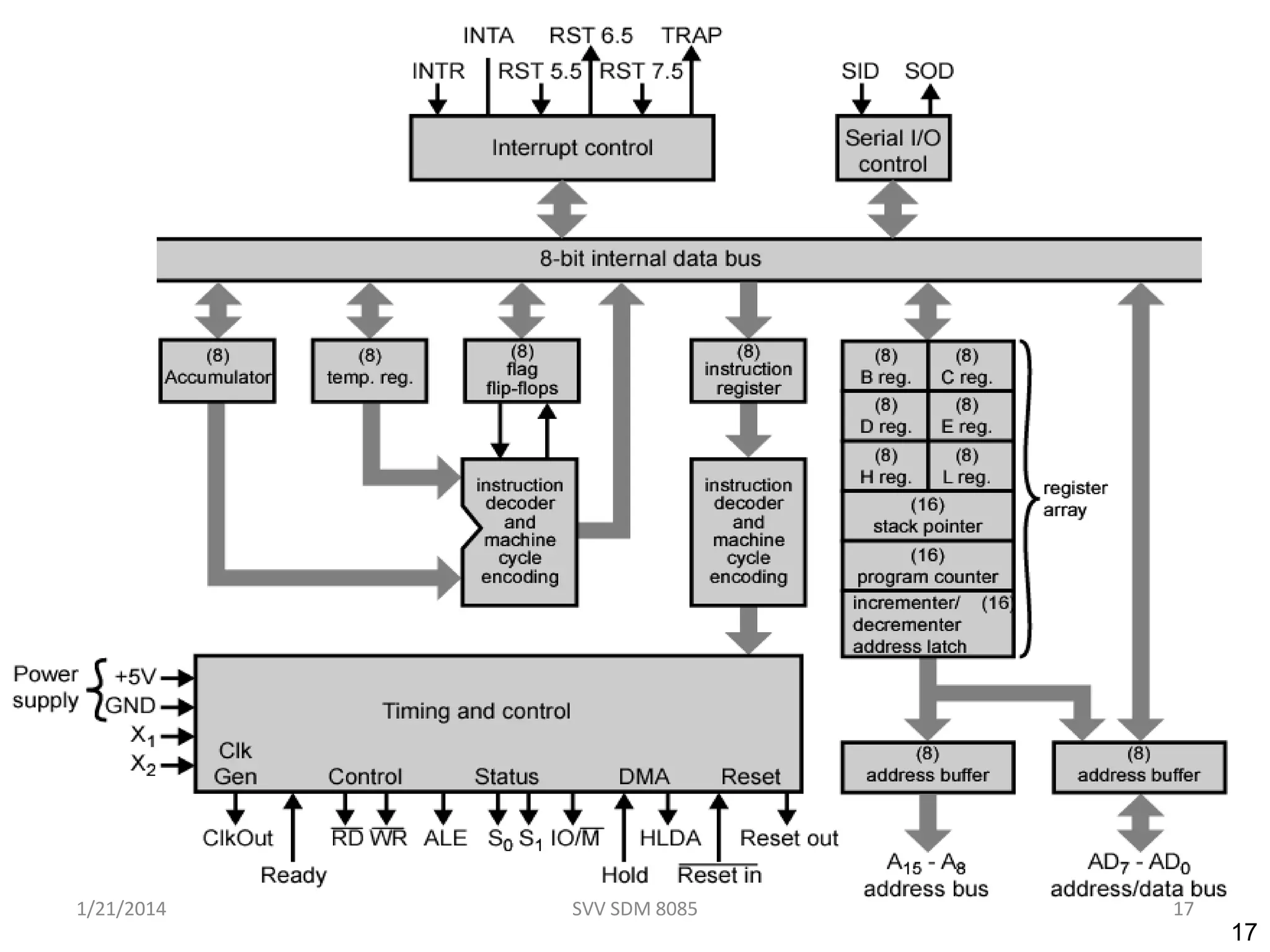

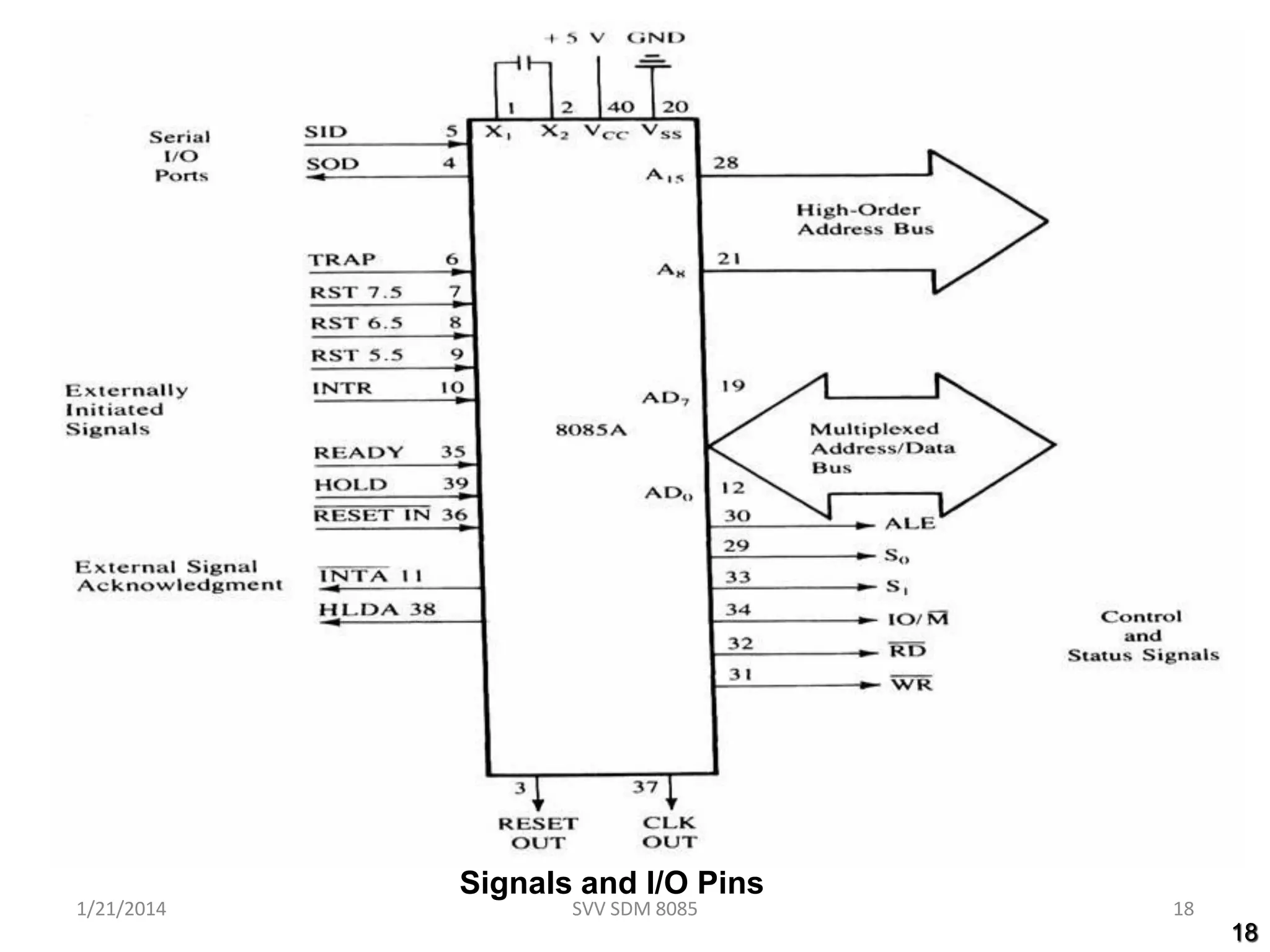

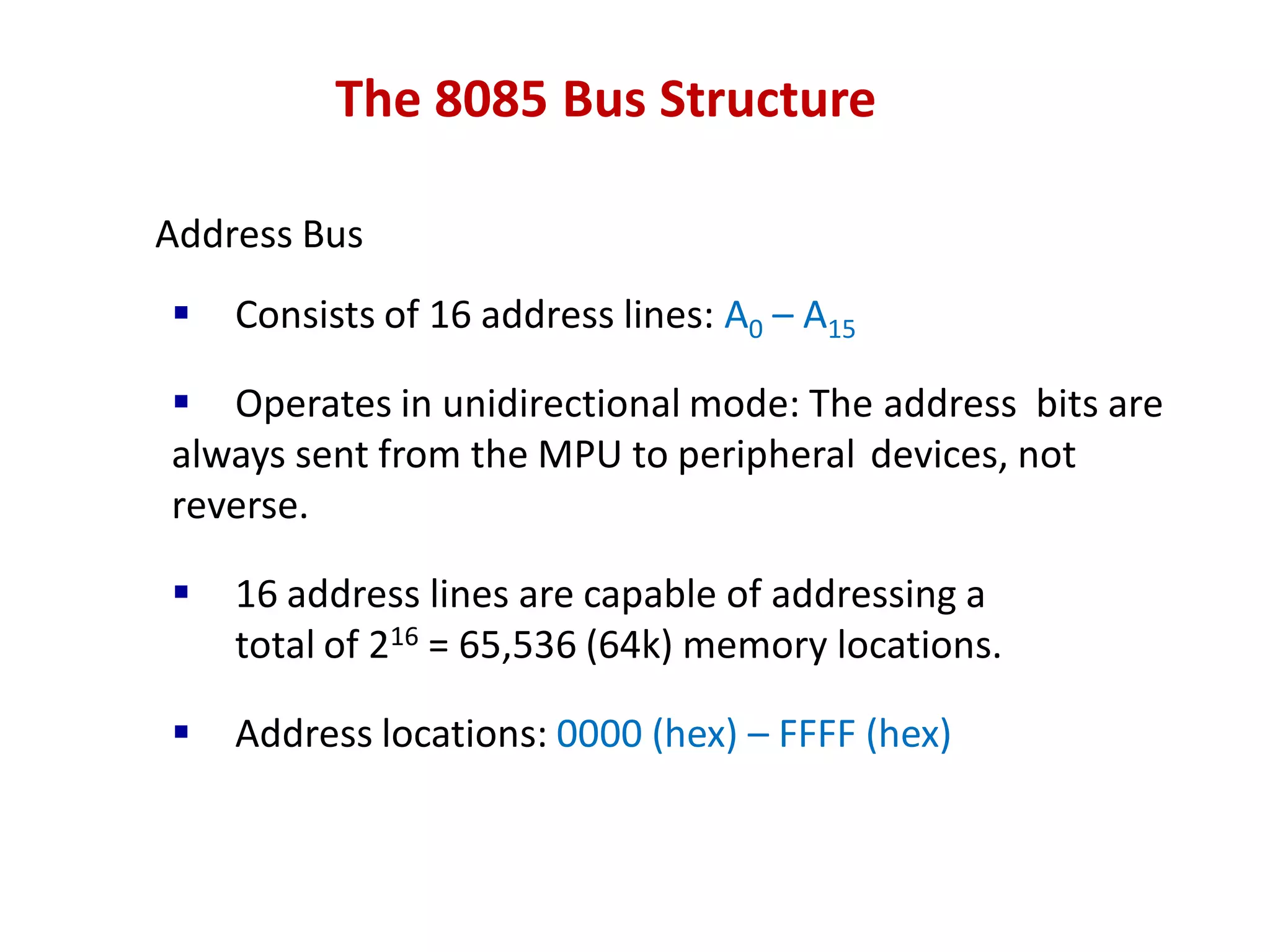

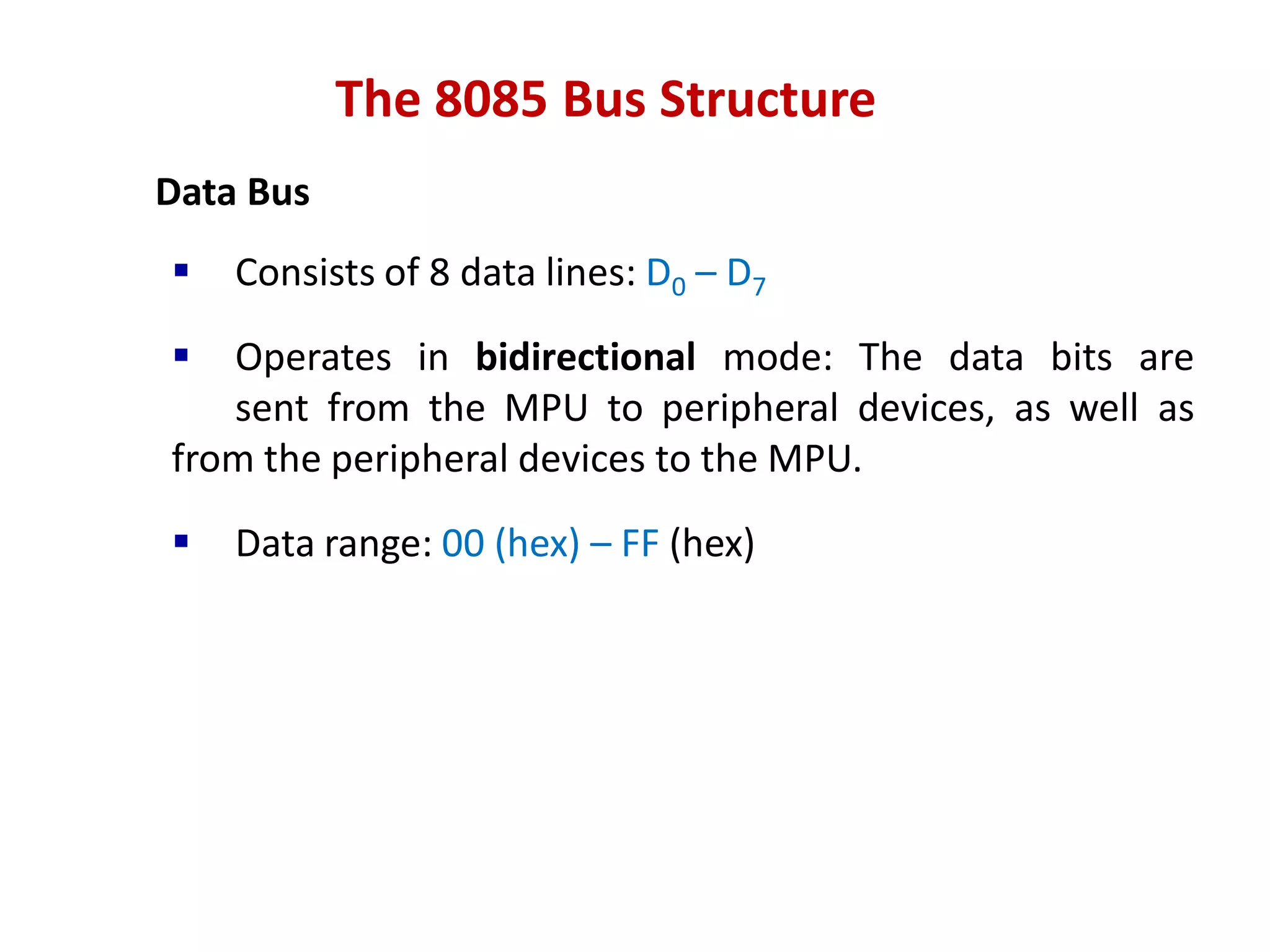

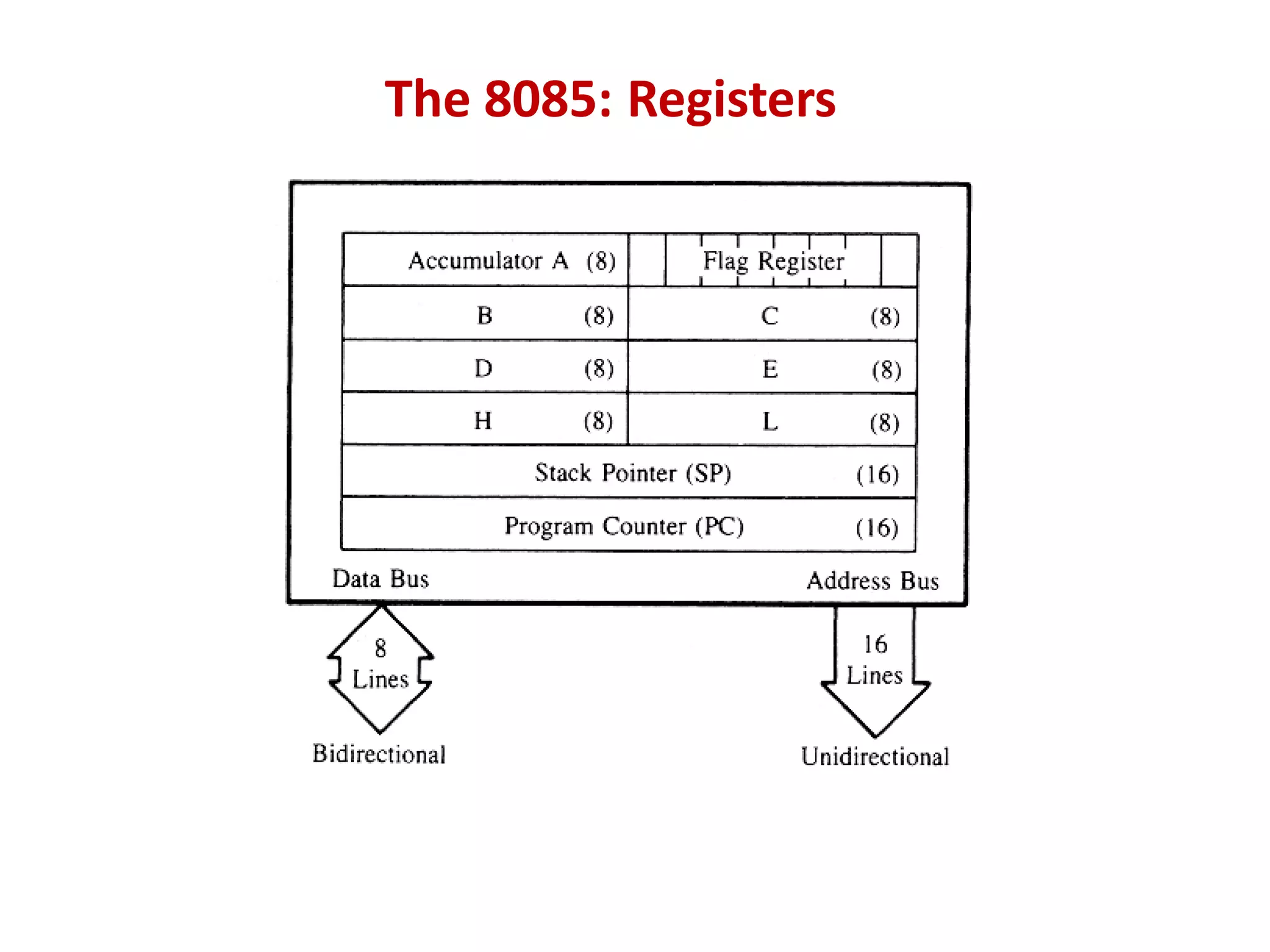

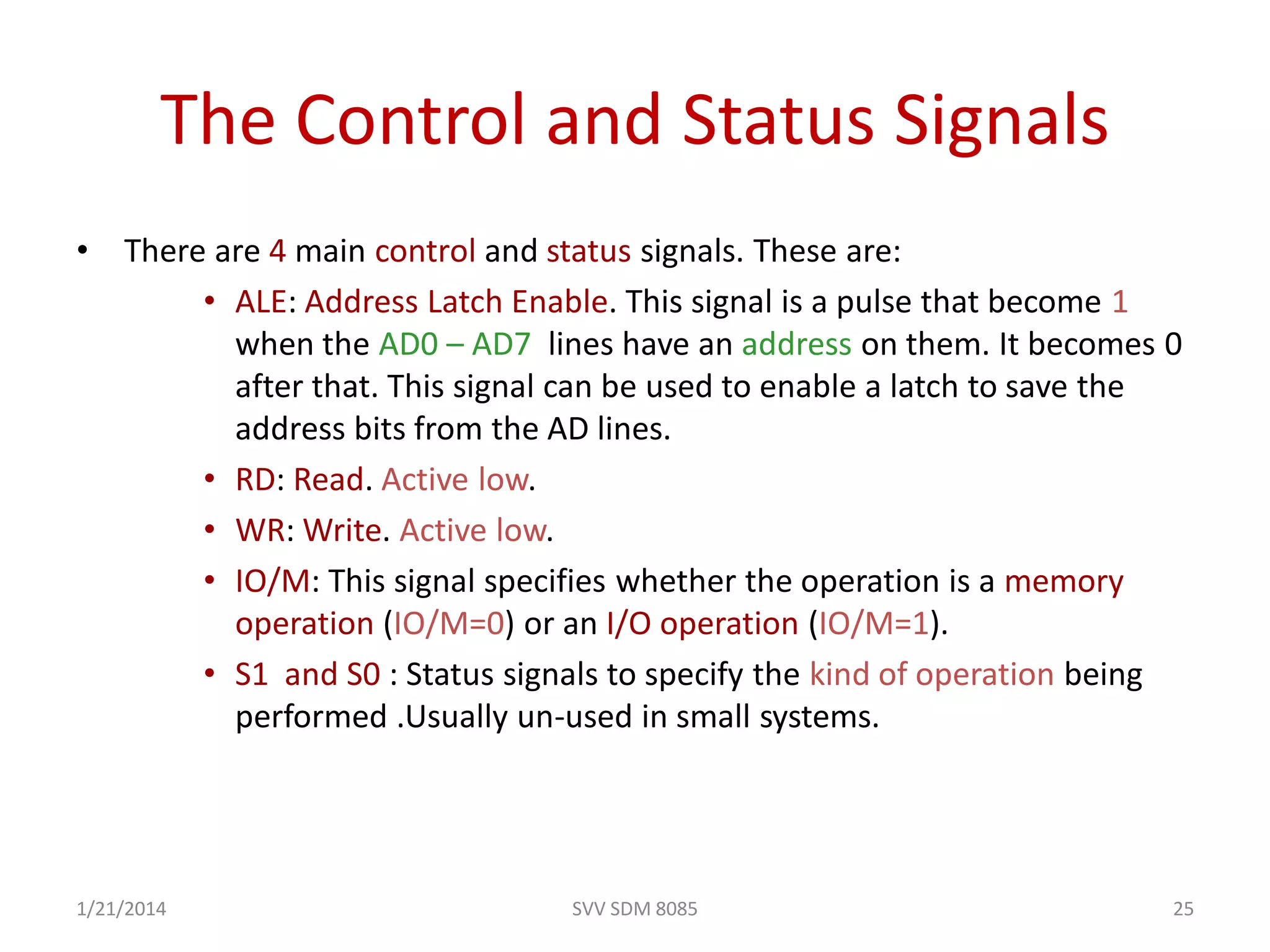

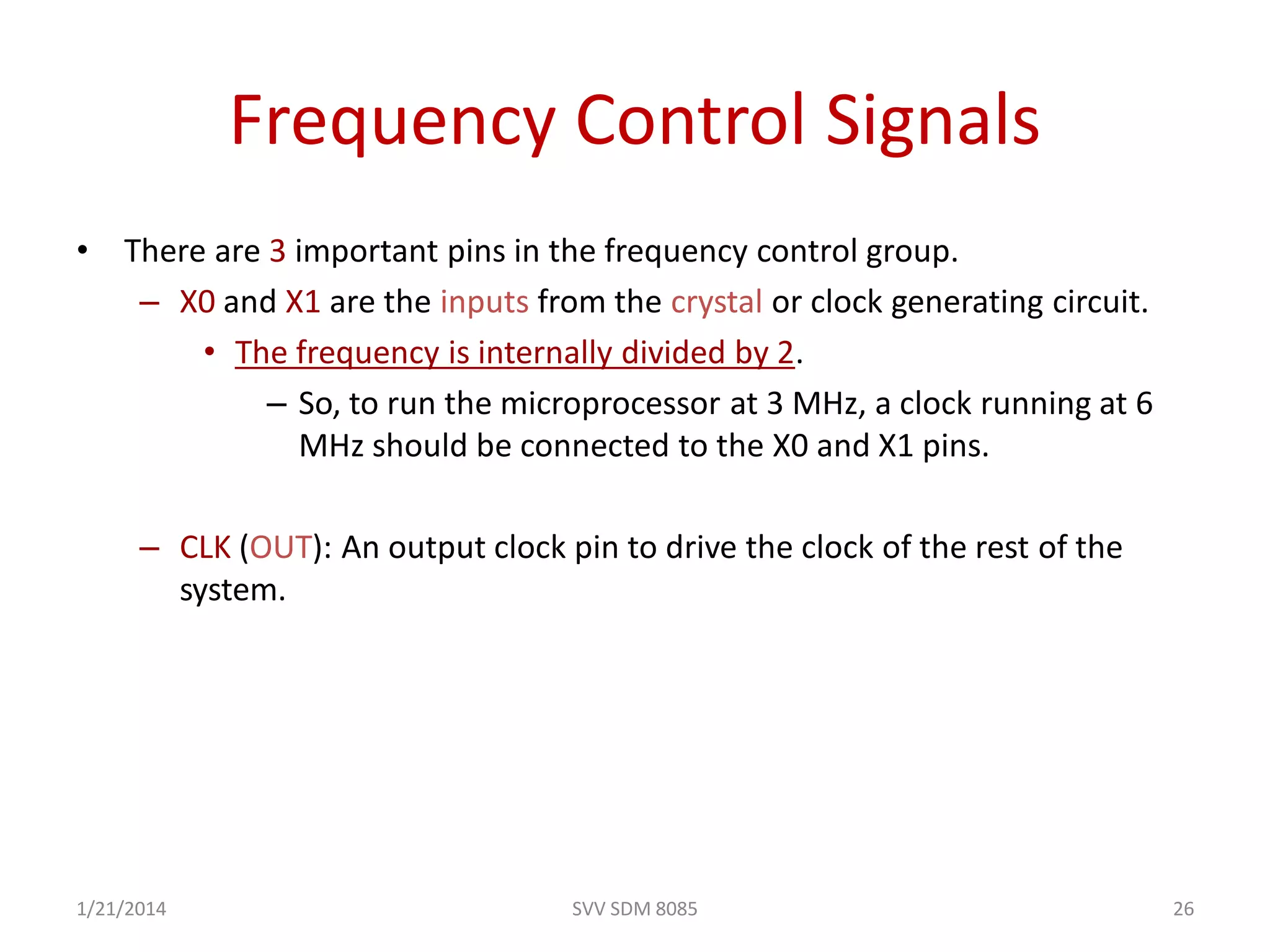

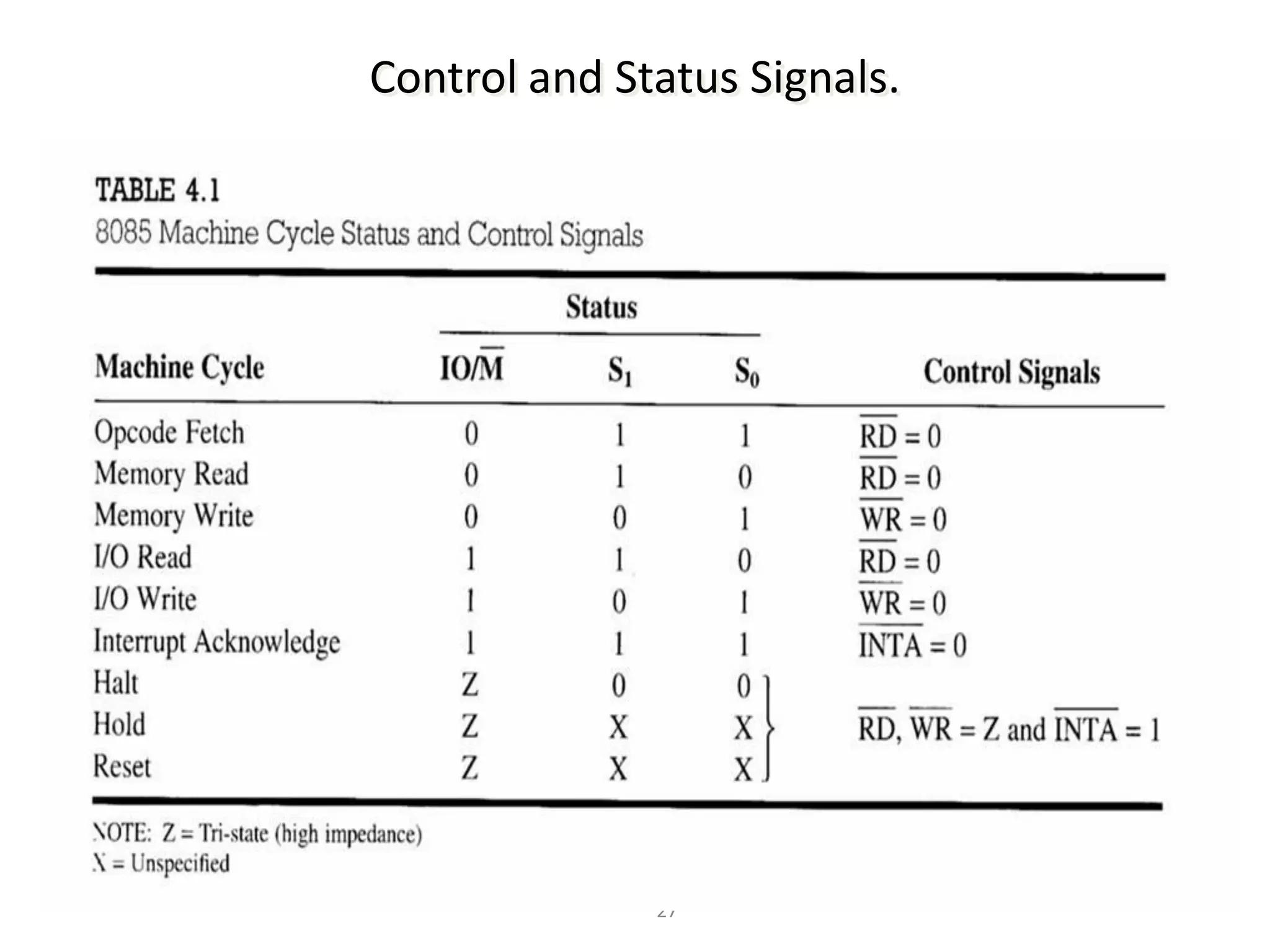

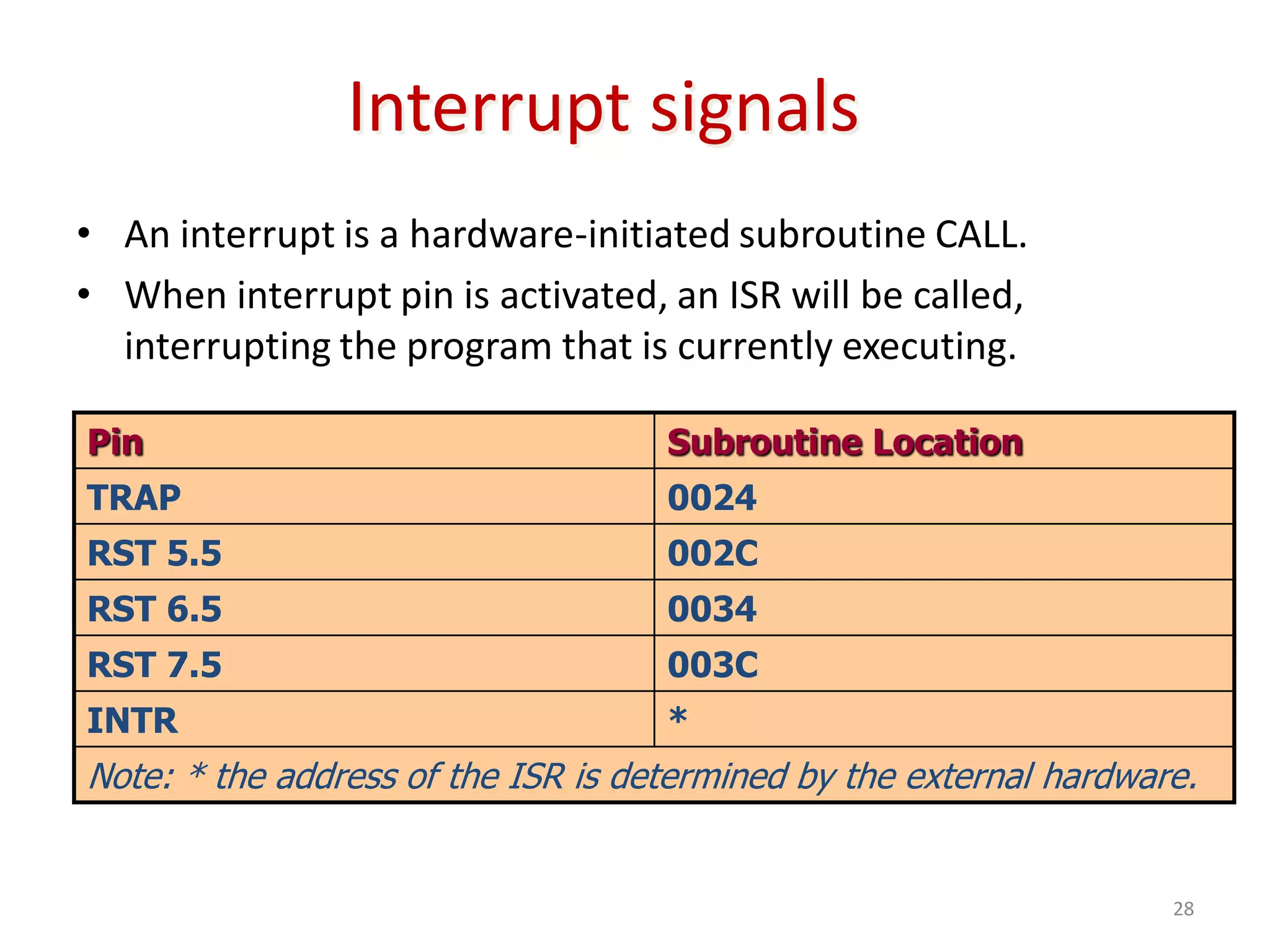

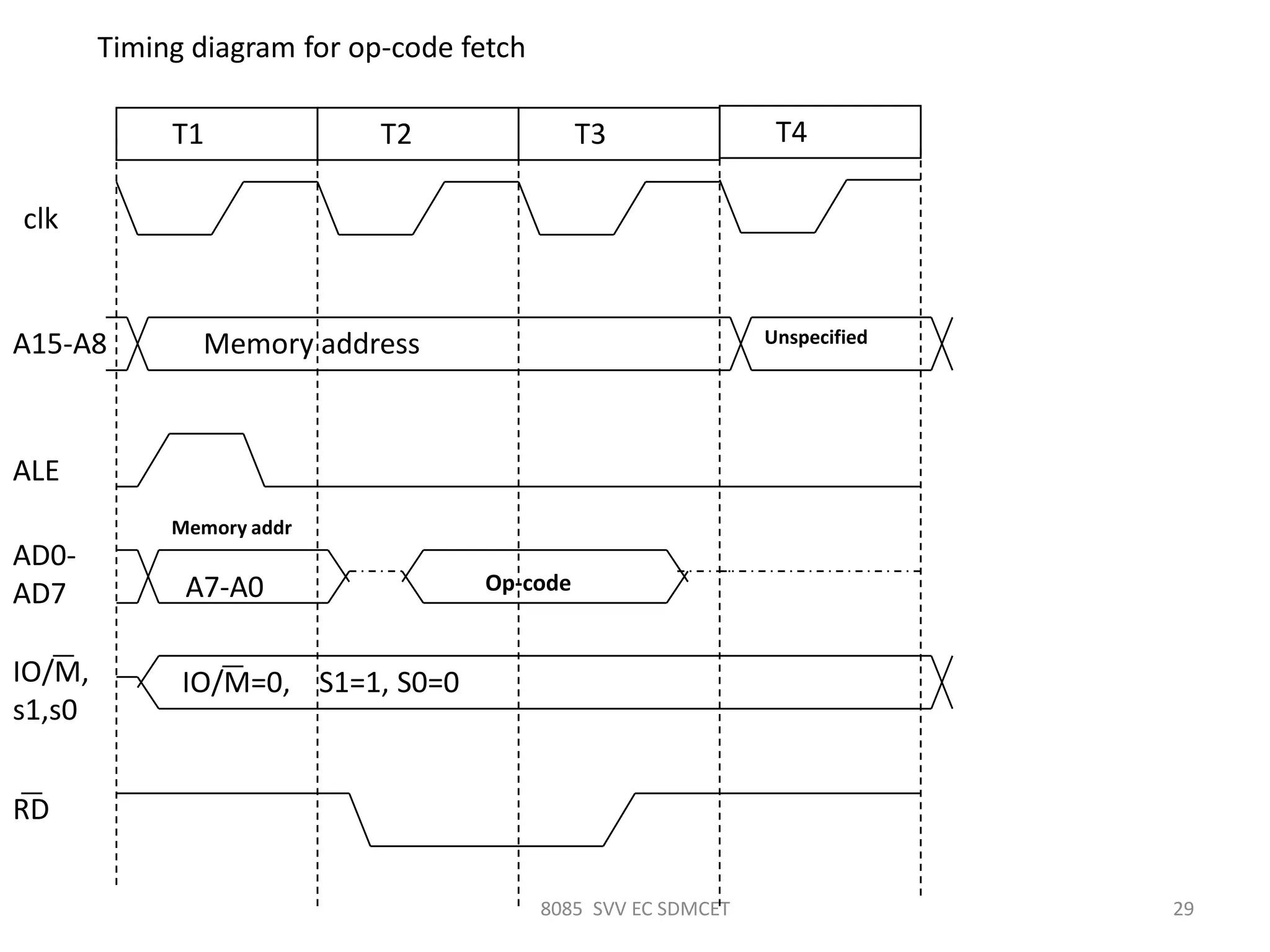

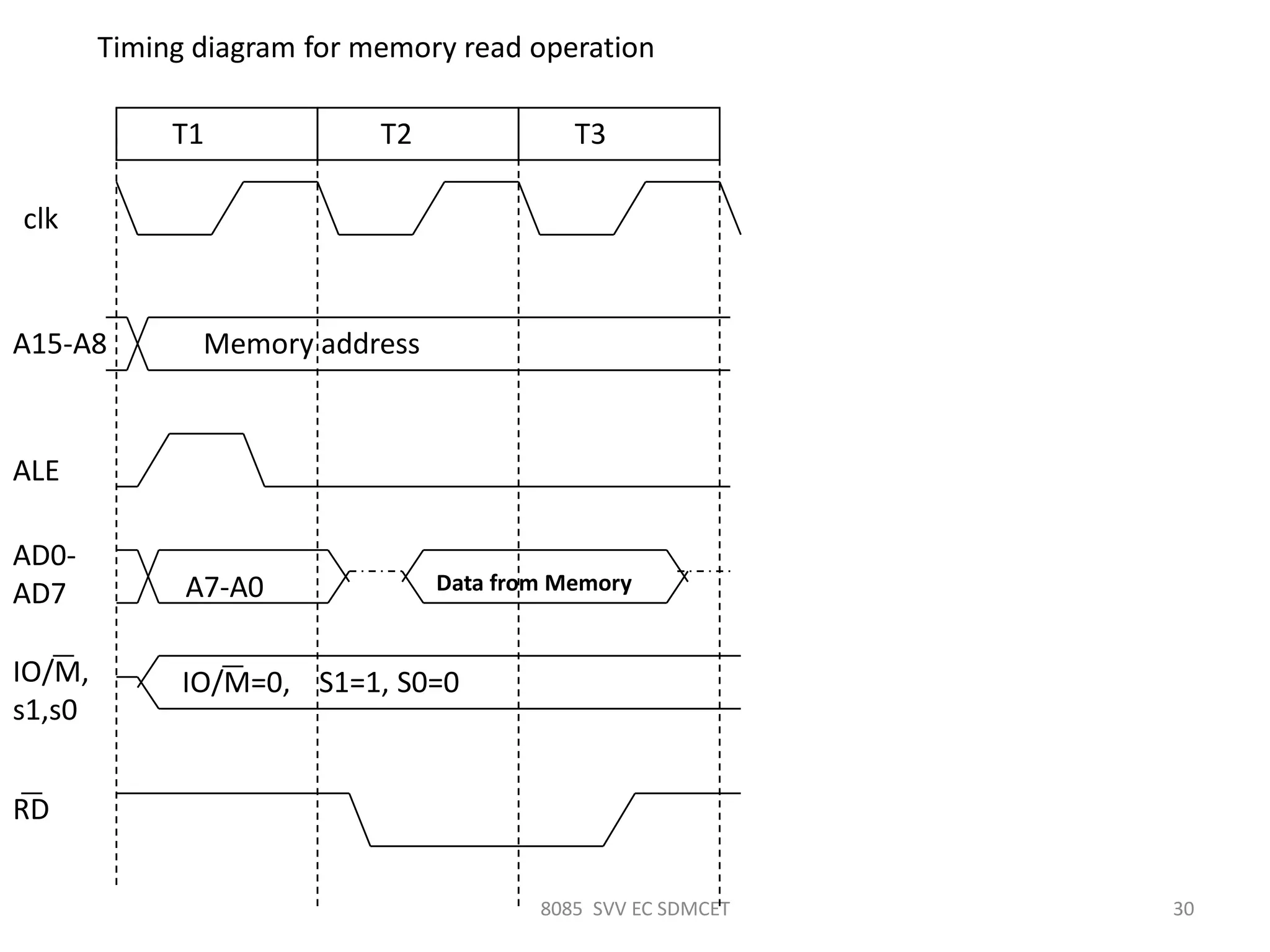

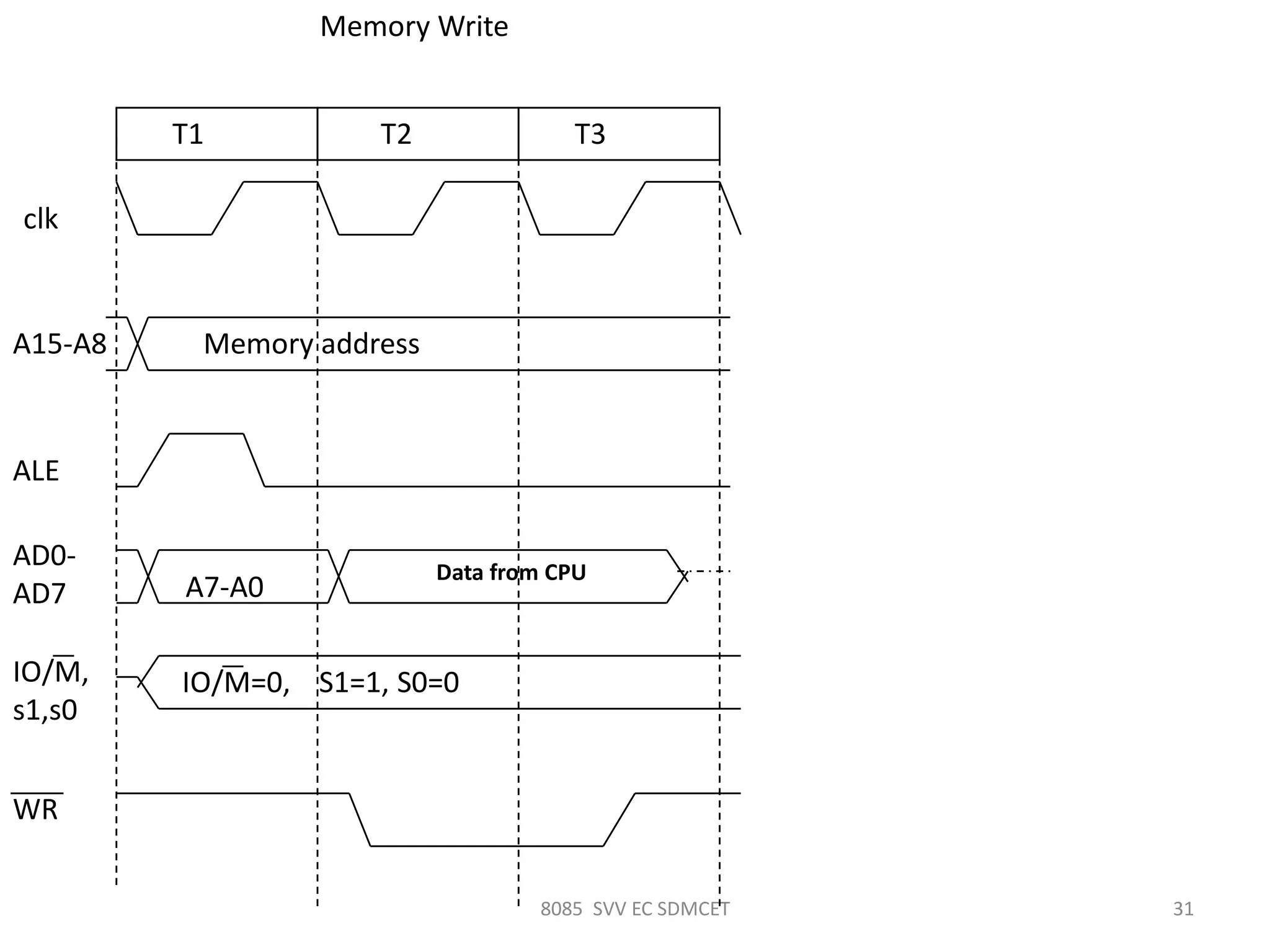

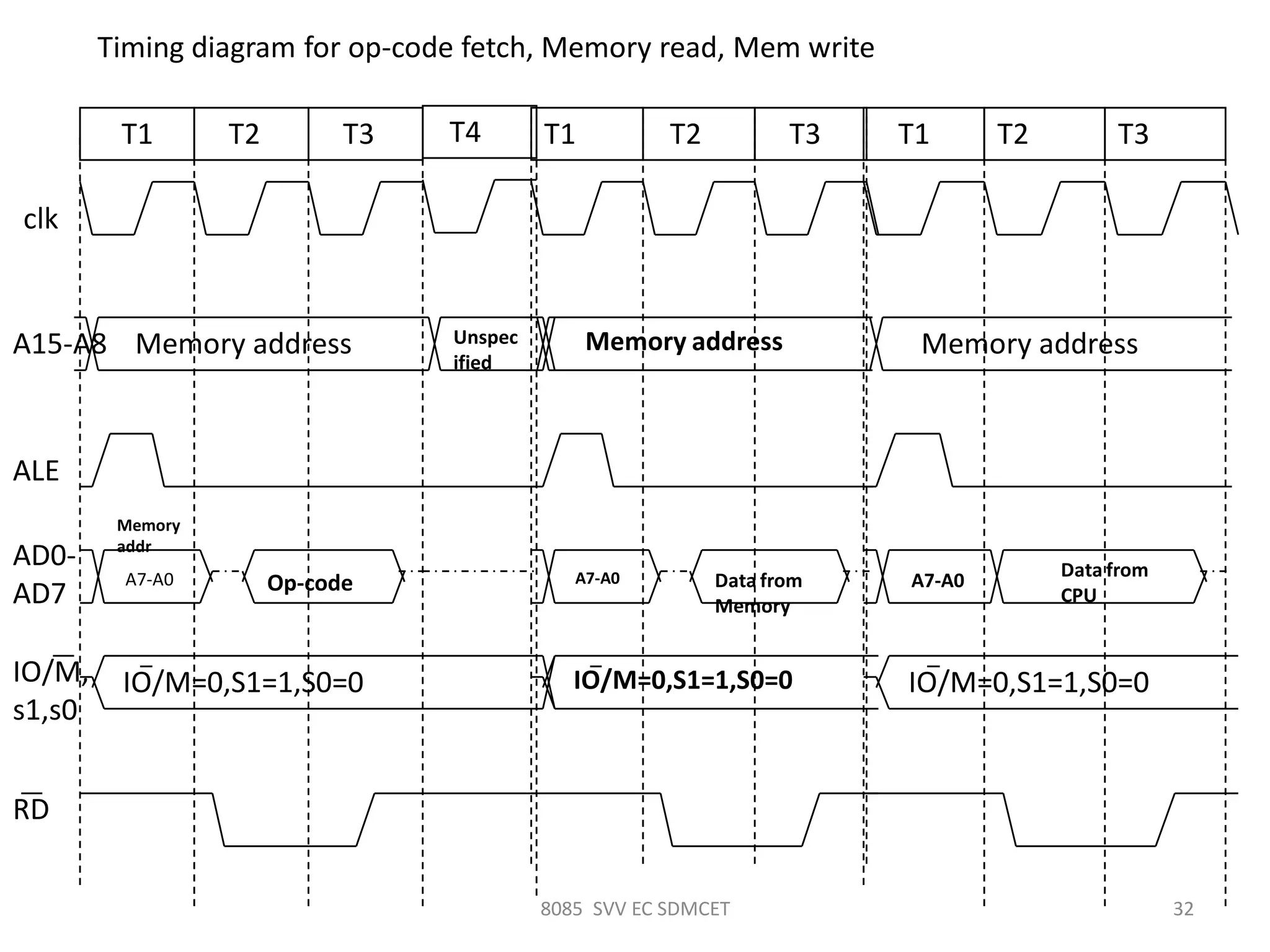

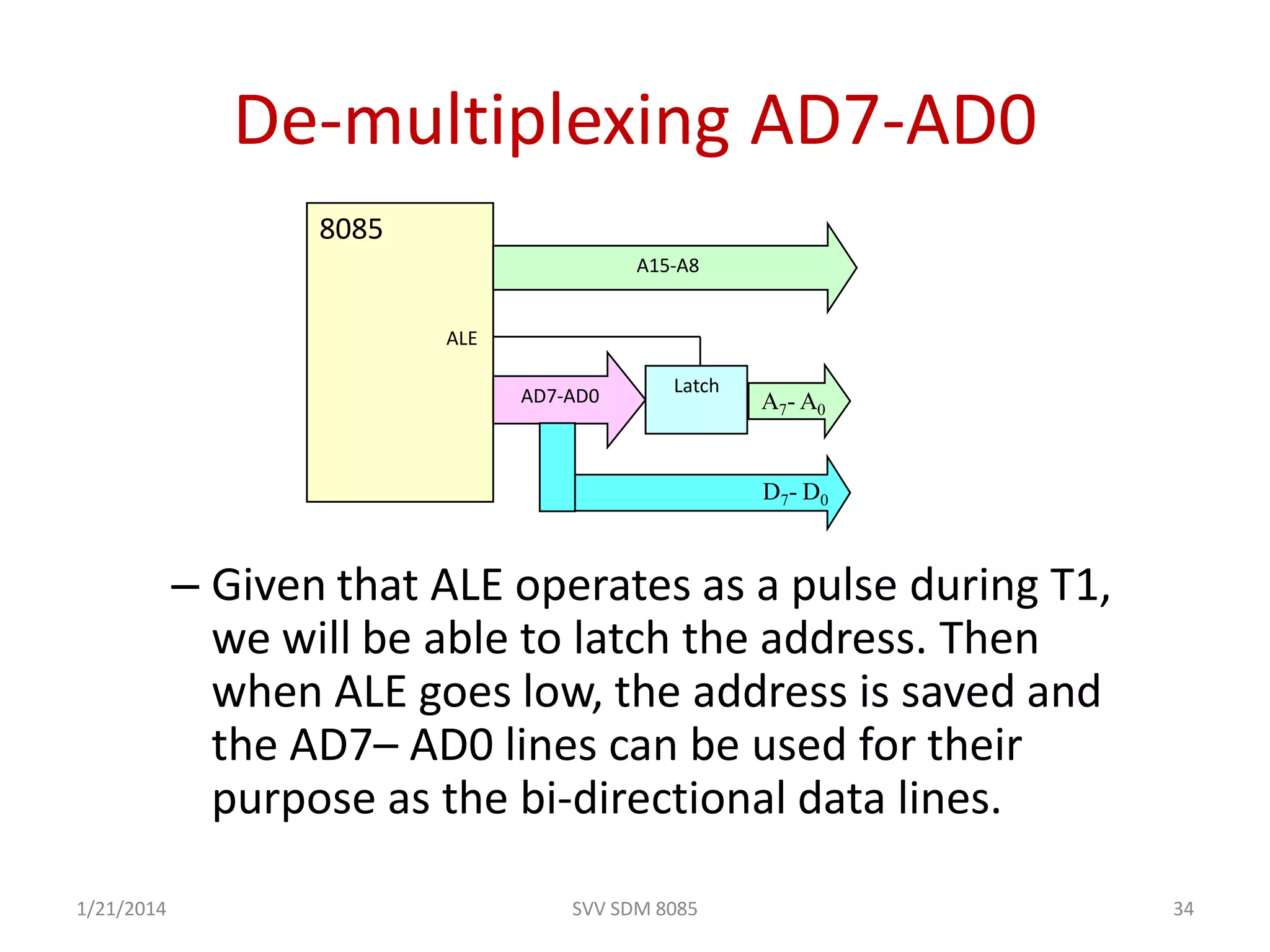

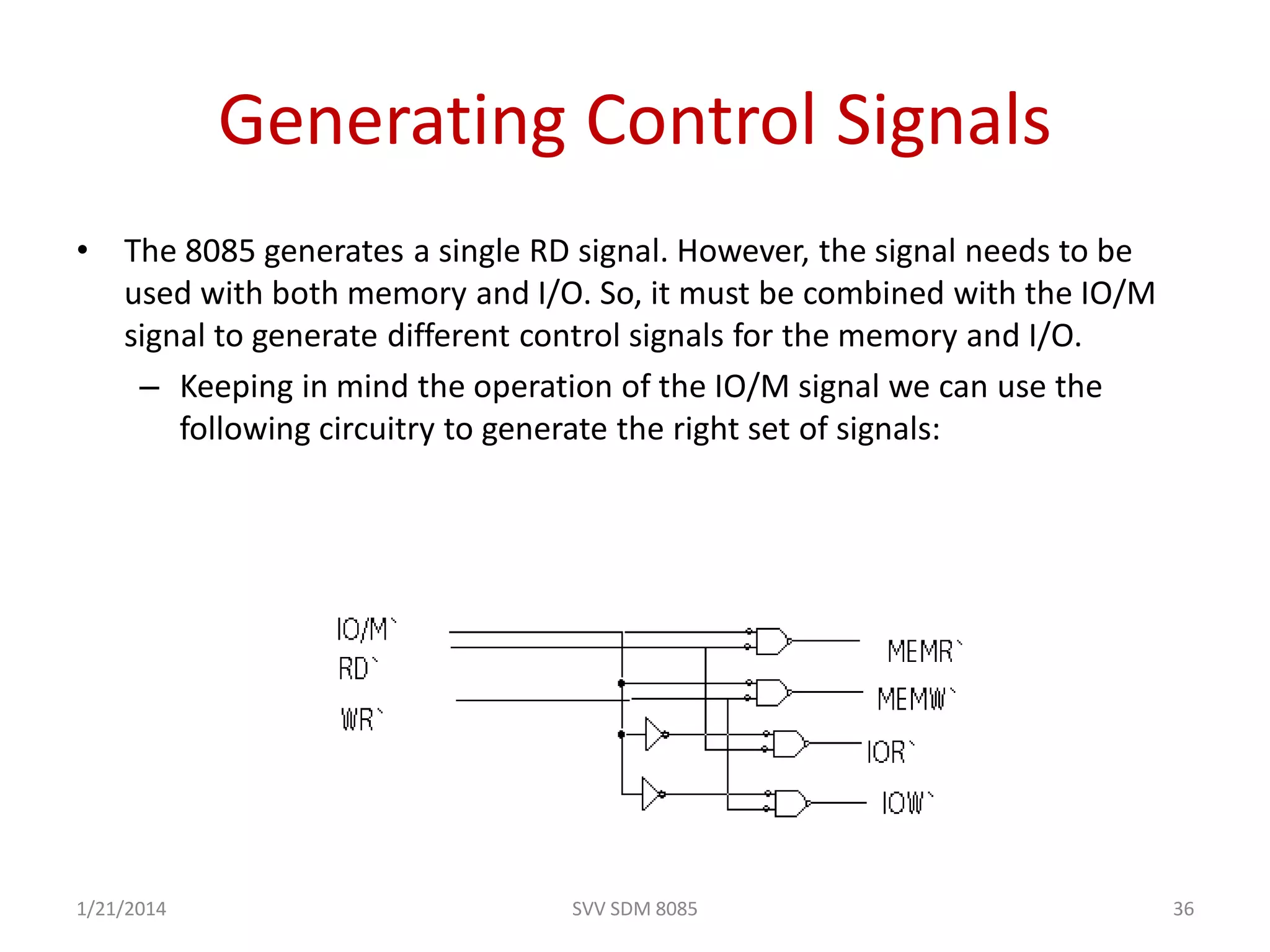

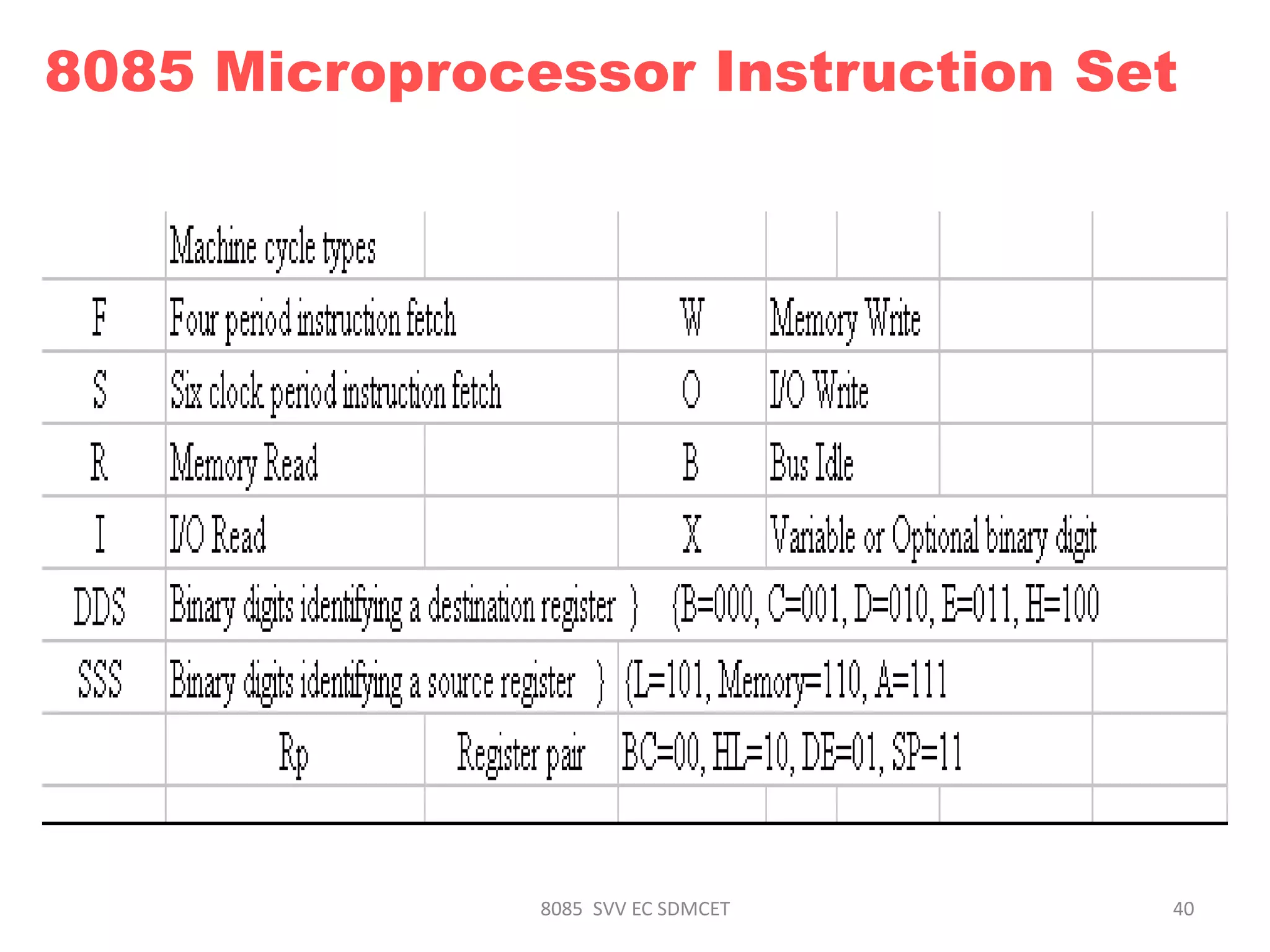

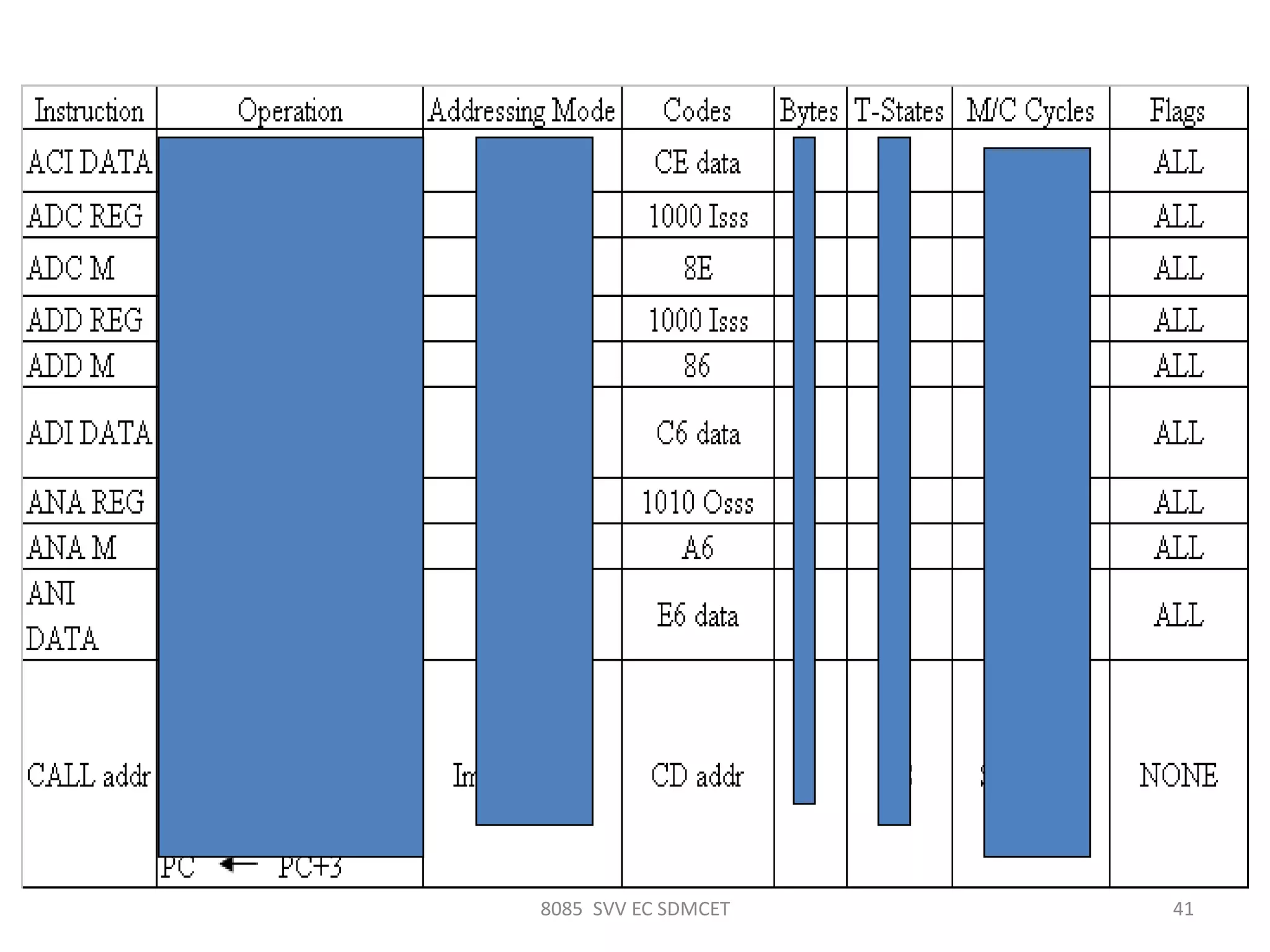

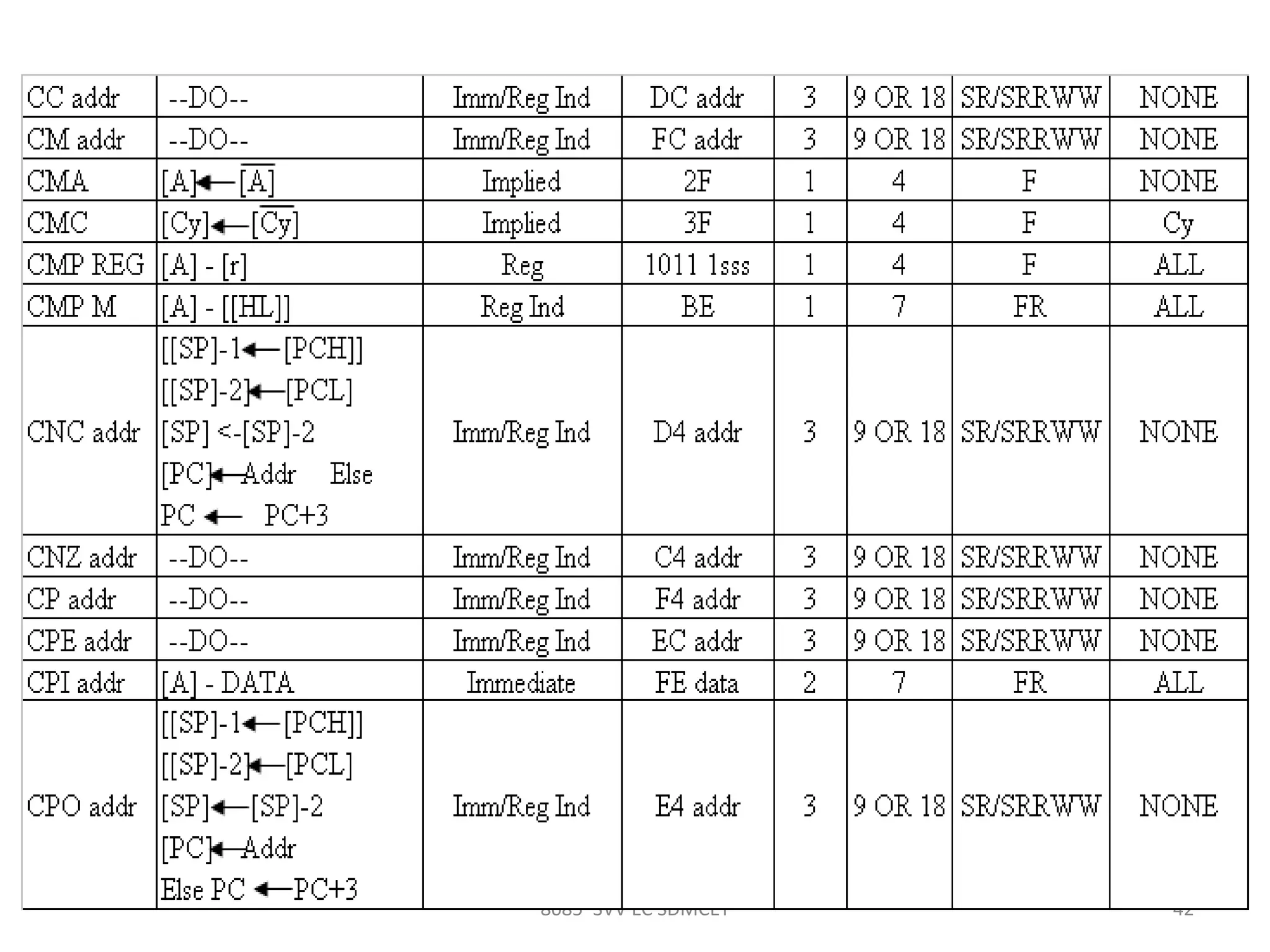

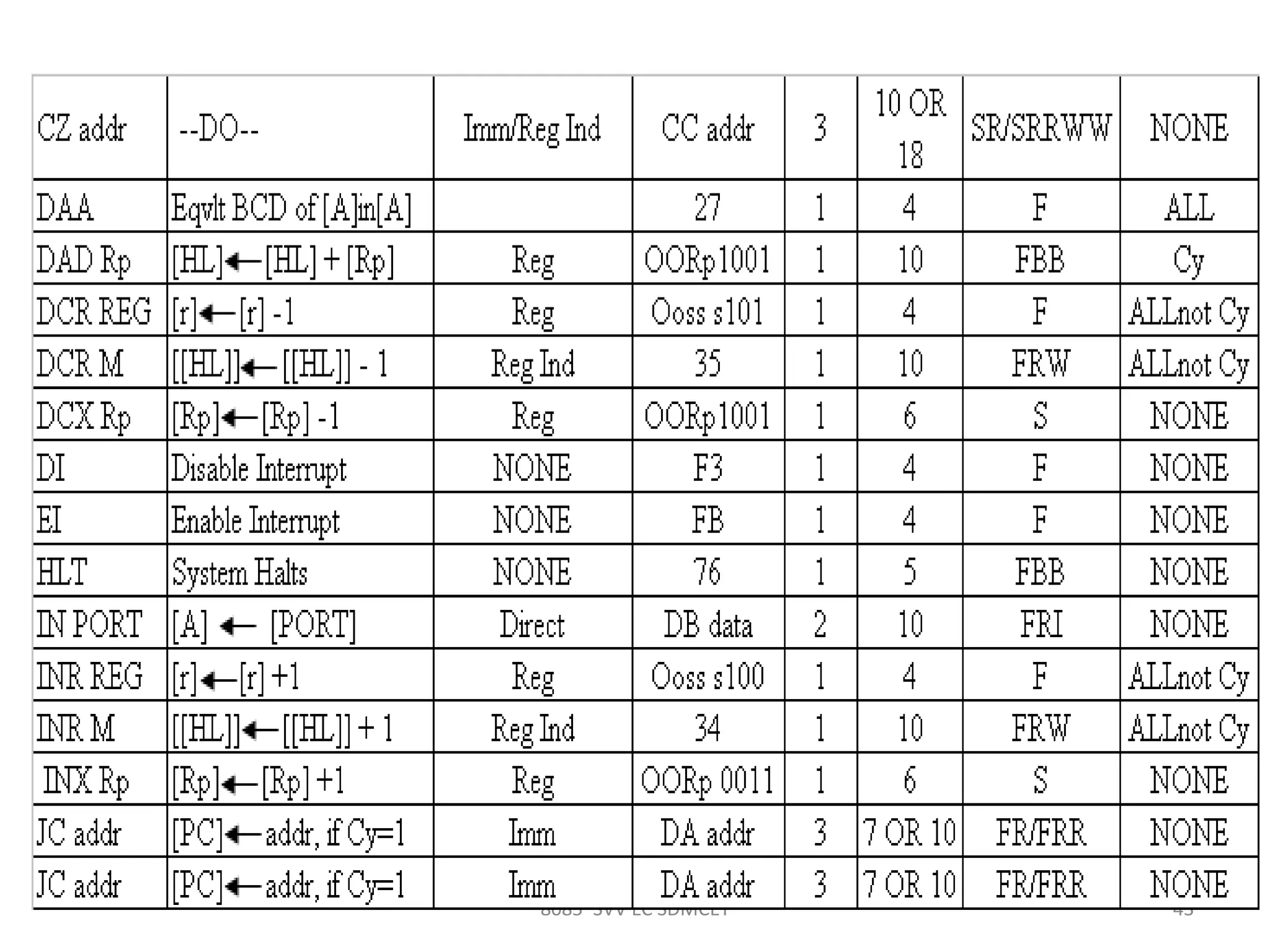

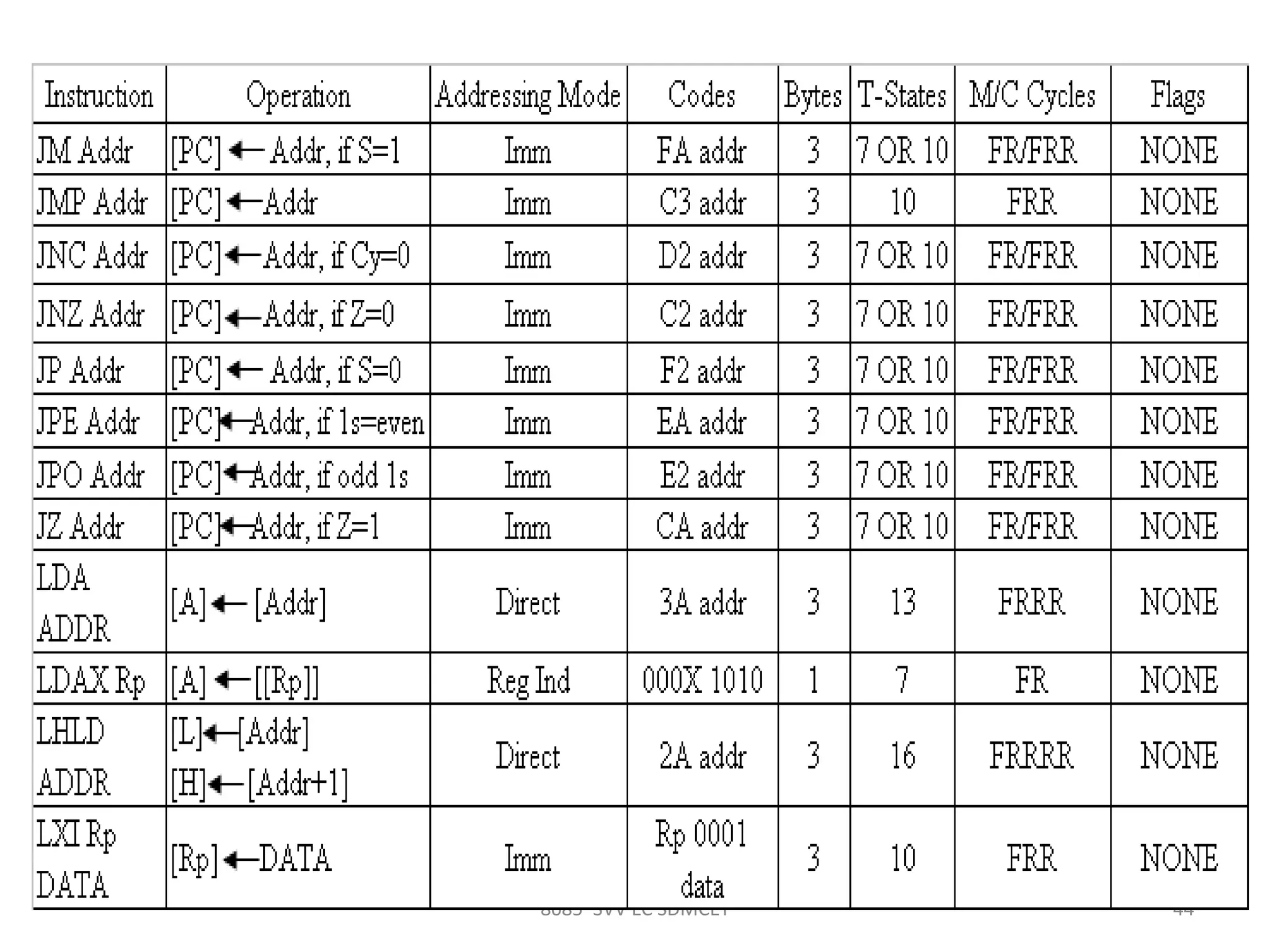

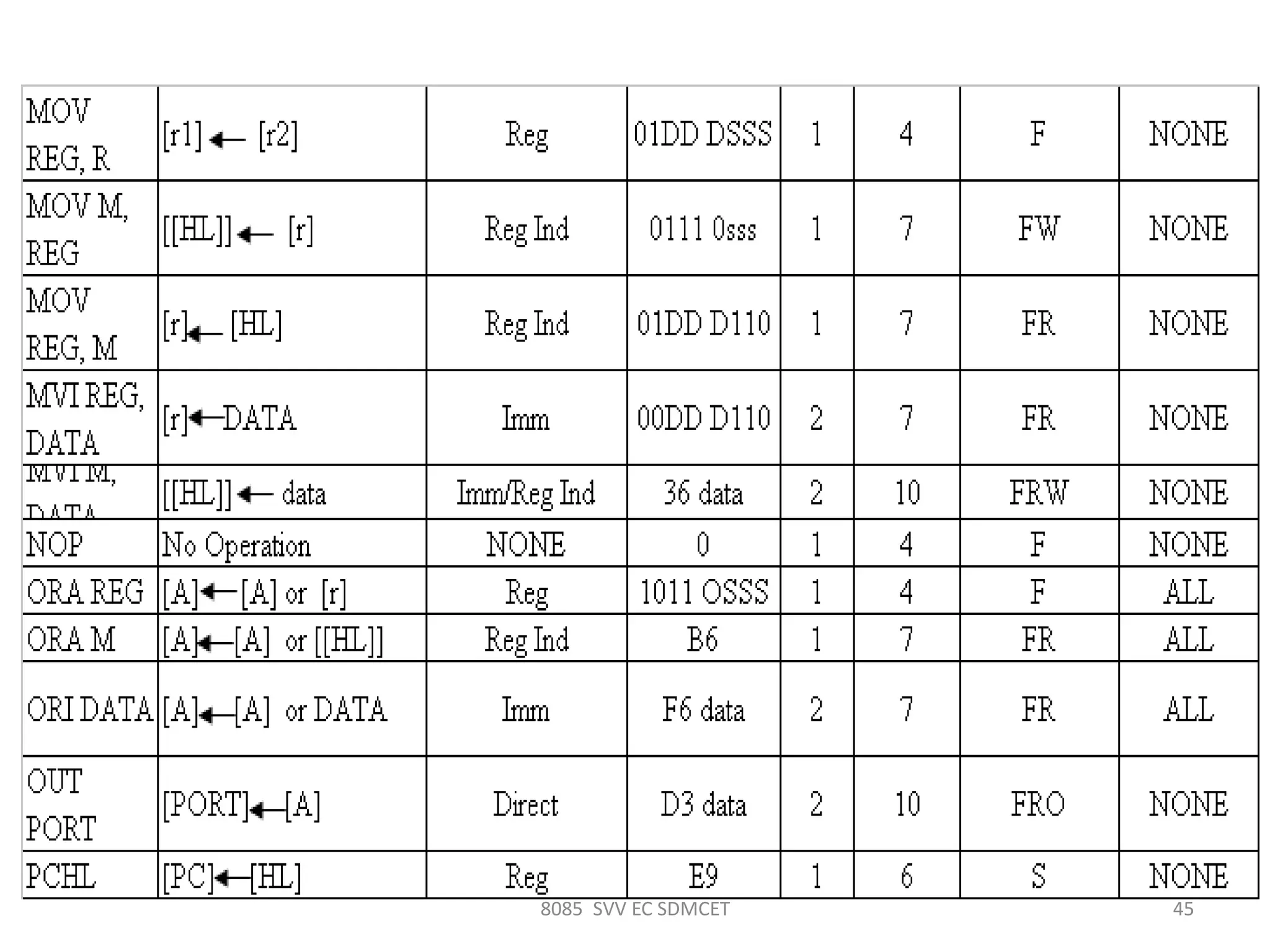

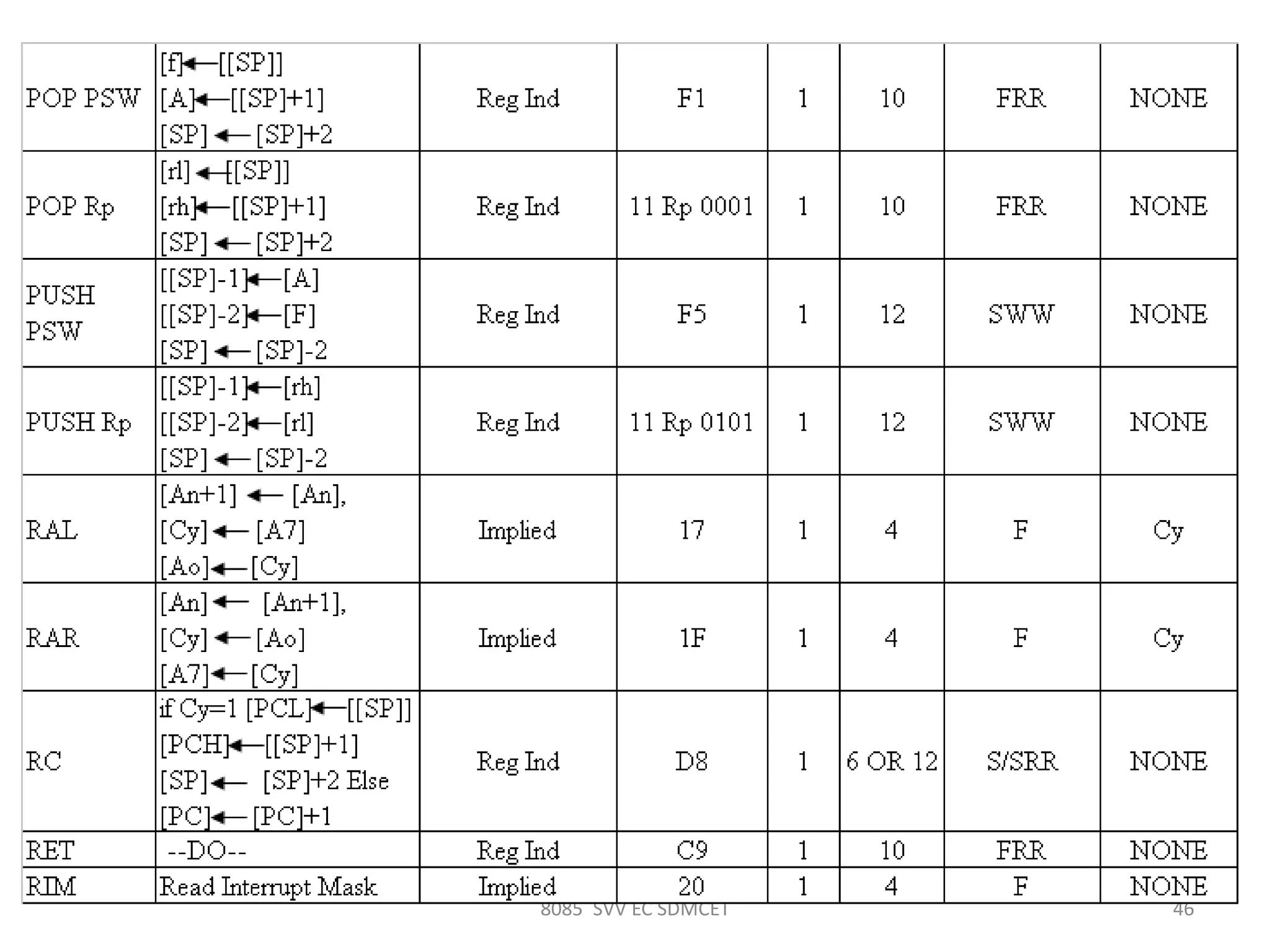

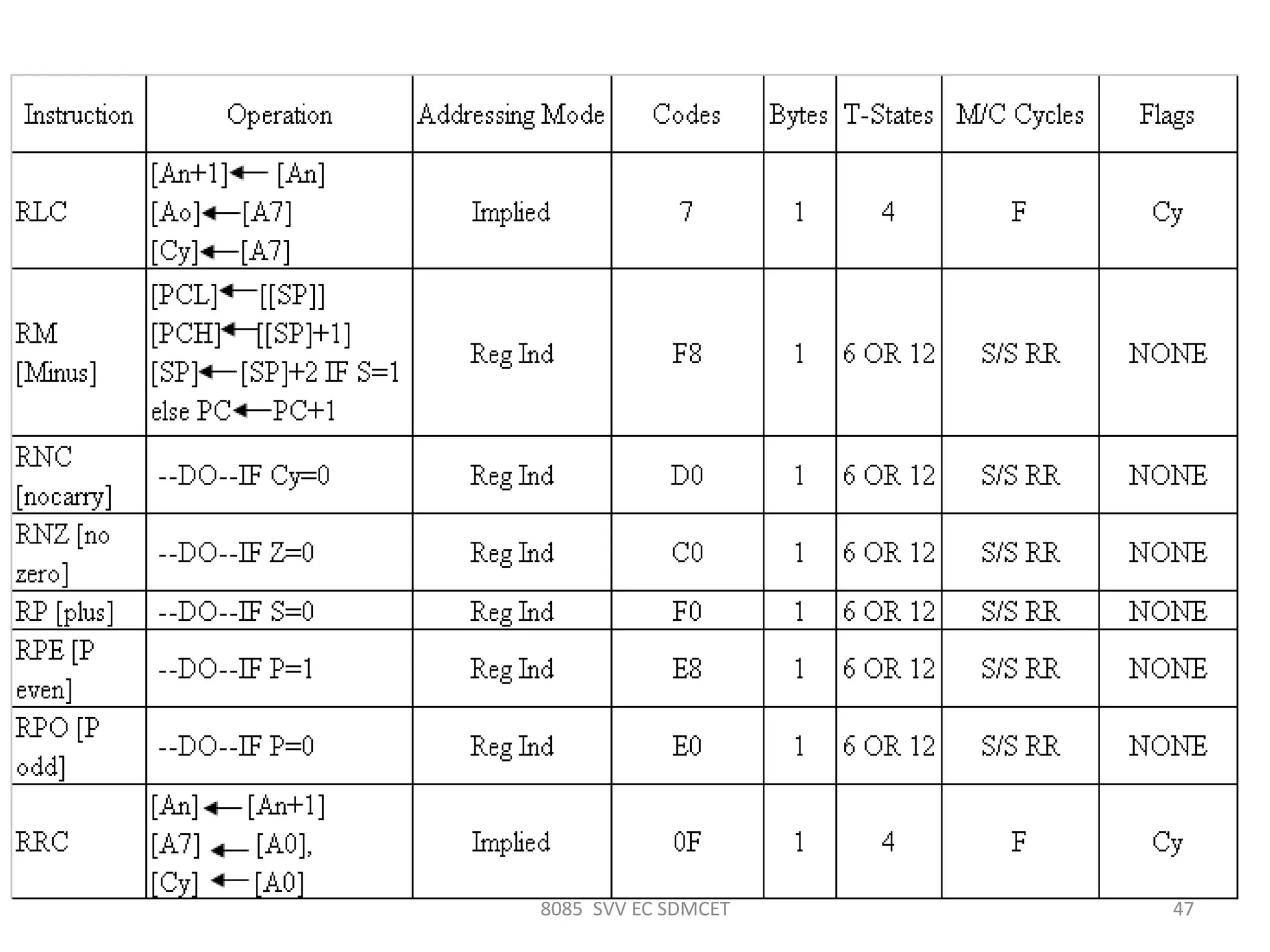

The document provides an introduction to the 8085 microprocessor. It discusses the basic components of a microcomputer including the CPU, memory (RAM and ROM), and I/O unit. It then describes the internal structure of the 8085 CPU including its registers, flag bits, program counter, and stack pointer. The document outlines the 8085 bus structure including its address bus, data bus, and control signals. It provides timing diagrams for opcode fetch, memory read, and memory write operations. Finally, it discusses addressing modes, instruction size, and includes a table of the 8085 instruction set.