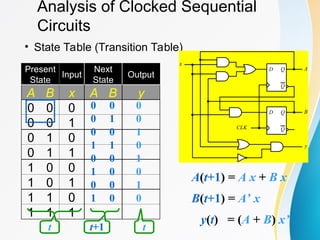

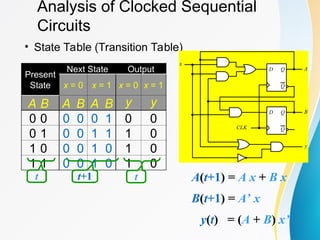

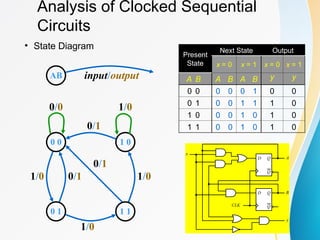

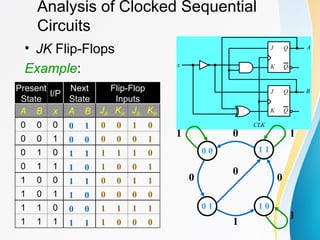

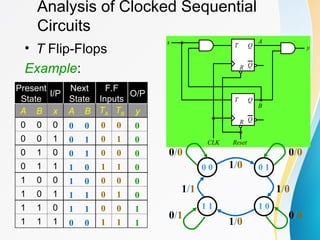

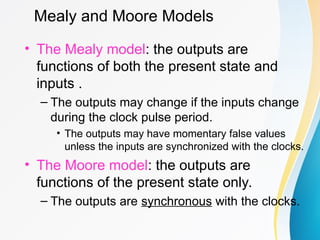

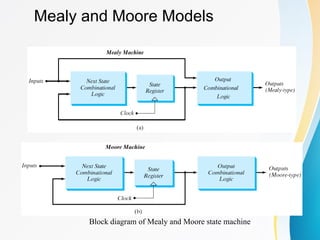

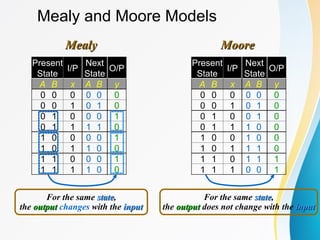

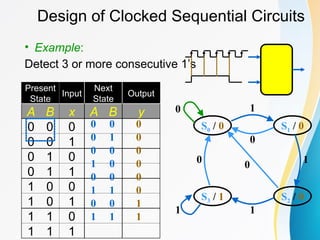

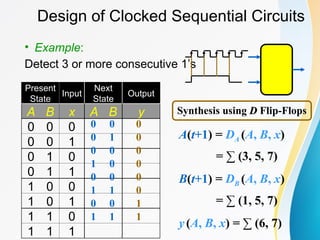

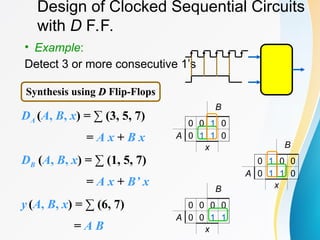

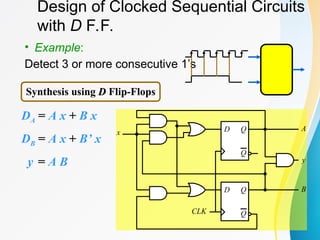

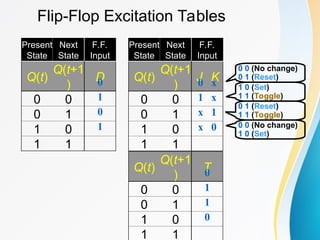

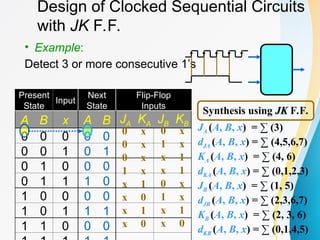

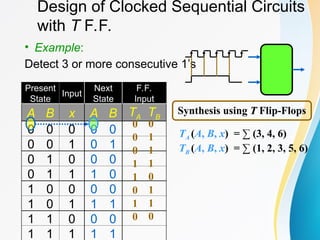

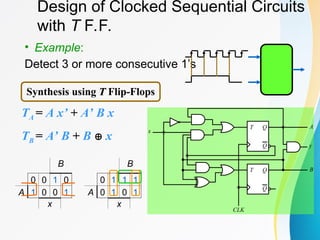

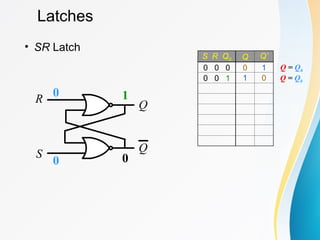

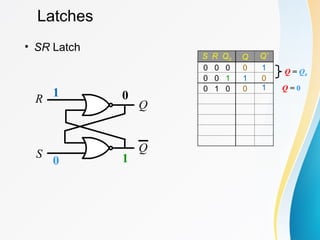

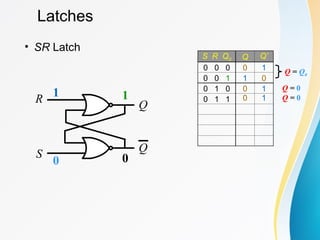

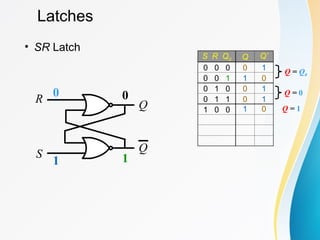

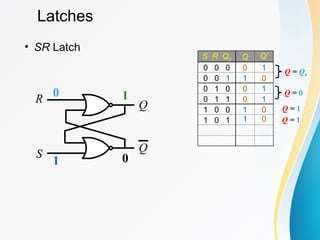

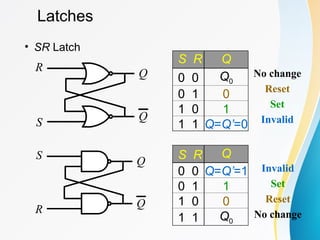

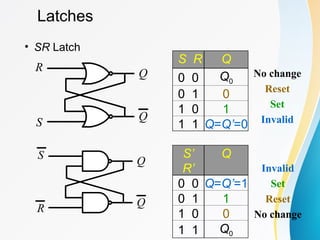

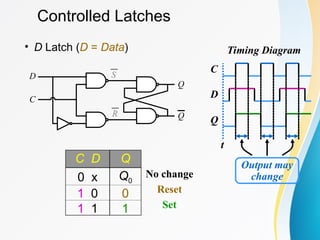

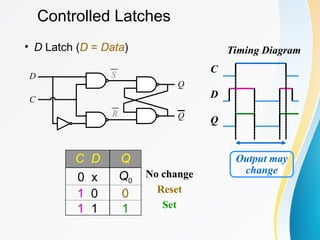

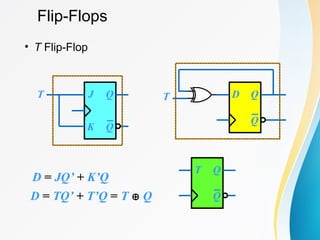

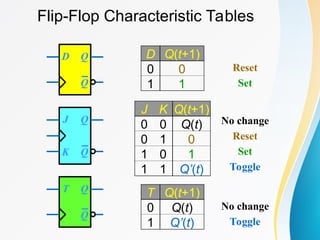

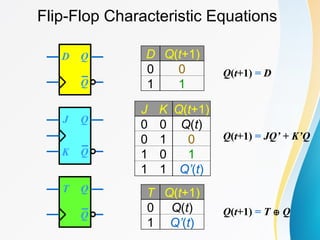

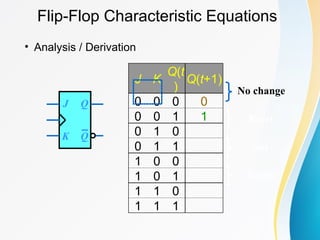

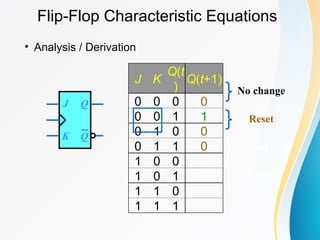

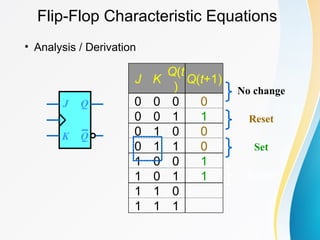

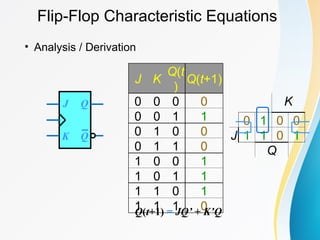

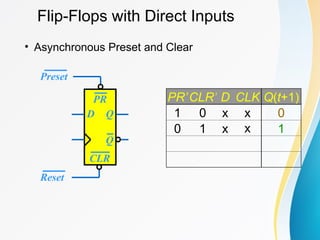

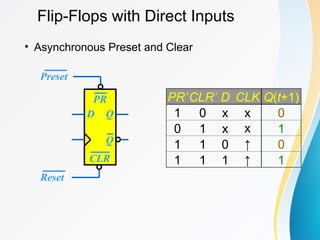

The document discusses various types of sequential circuits, focusing on combinational and memory elements like latches and flip-flops. It details the behavior and characteristics of SR latches, D latches, JK flip-flops, and T flip-flops, providing state equations and transition tables. Additionally, it highlights edge-triggered vs level-triggered methods and includes examples of clocked sequential circuits.

![Analysis of Clocked Sequential

Circuits

• State Equations

D Q

Q

CLK

D Q

Q

A

B

y

x

A(t+1) = DA

= A(t) x(t)+B(t) x(t)

= A x + B x

B(t+1) = DB

= A’(t) x(t)

= A’ x

y(t) = [A(t)+ B(t)] x’(t)

= (A + B) x’](https://image.slidesharecdn.com/cs6201unit3l01-250112105106-cb3420db/85/CS6201_UNIT3_L01-ppt-Digiital-Electronics-34-320.jpg)