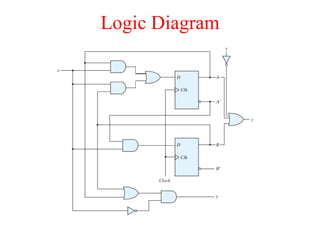

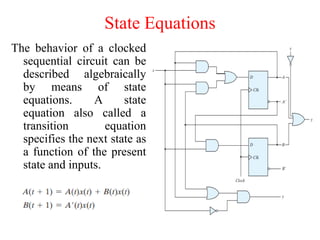

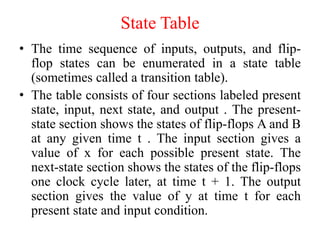

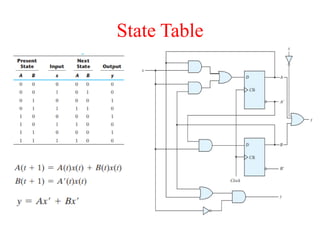

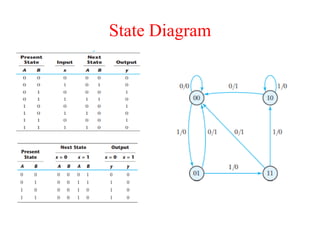

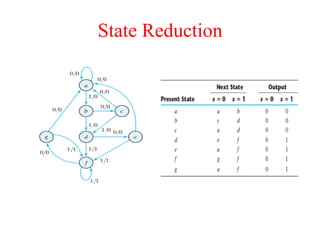

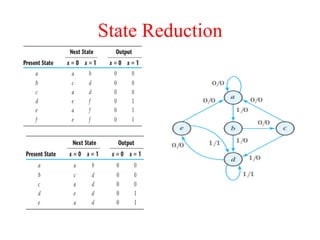

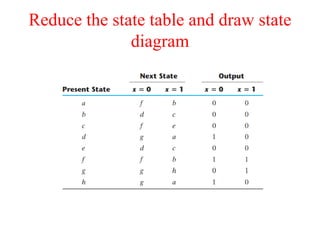

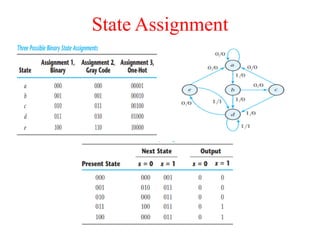

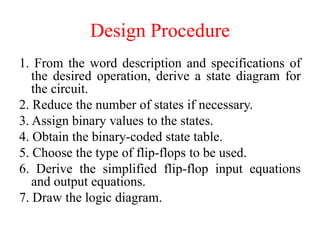

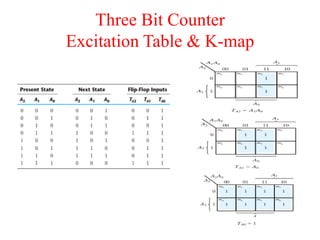

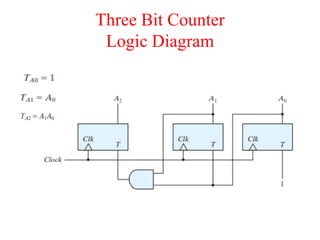

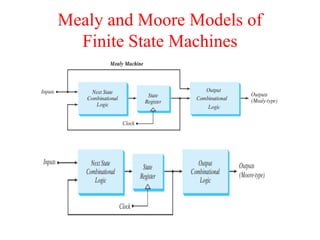

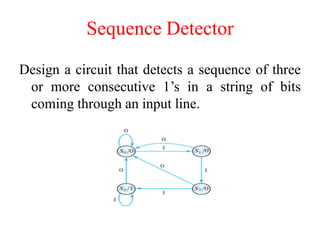

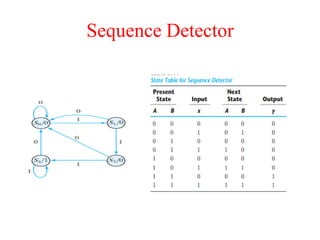

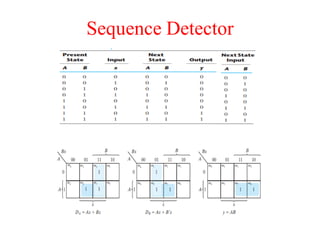

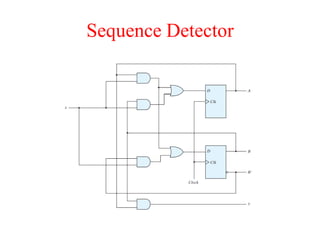

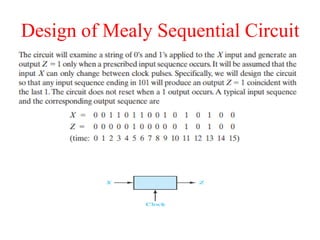

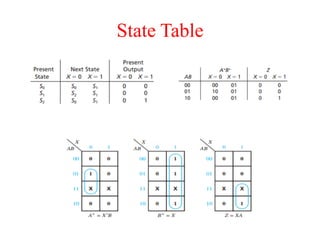

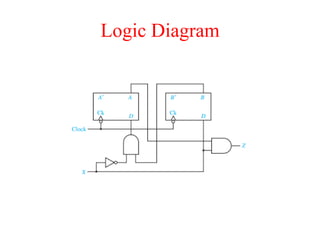

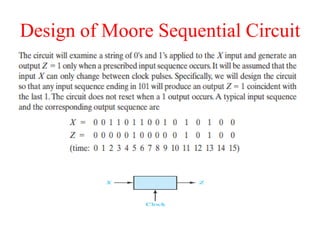

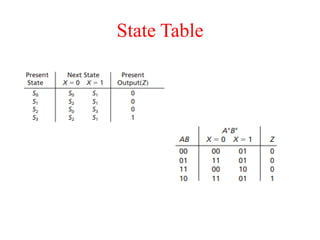

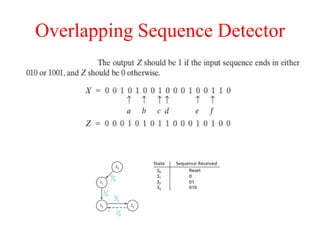

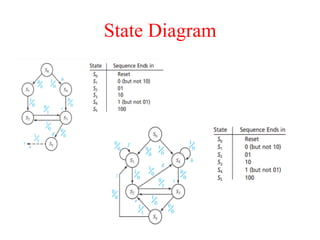

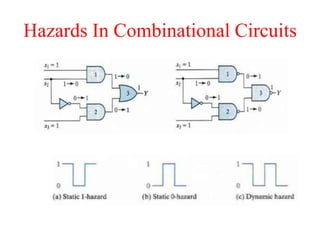

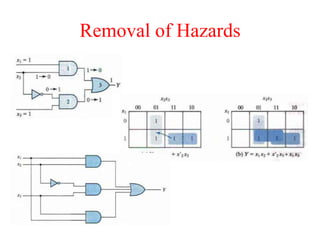

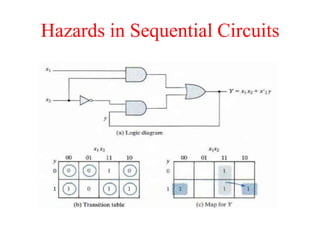

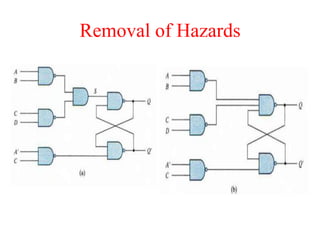

The document outlines the objectives and key concepts of a course on digital electronics, focusing on digital fundamentals, combinational circuit design, and synchronous sequential circuits. It details the analysis of state machines, including Mealy and Moore models, state tables, state diagrams, and the implications of hazards in circuit design. The goals include enhancing understanding of circuit behavior, designing logic circuits, and managing hazards to ensure proper functionality in digital systems.