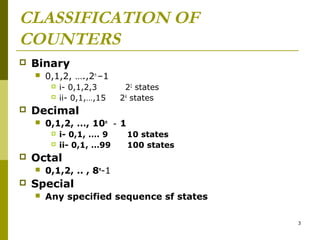

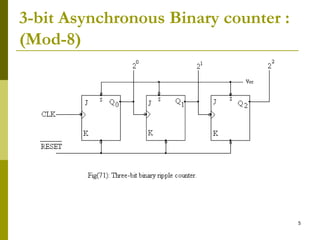

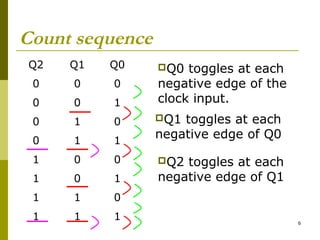

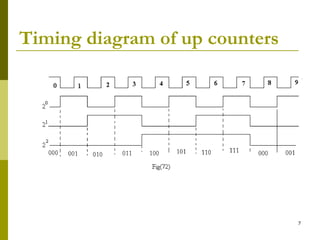

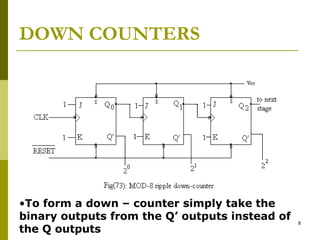

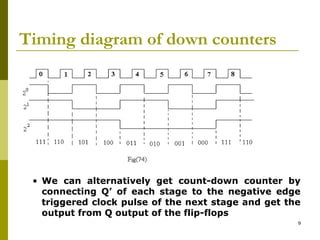

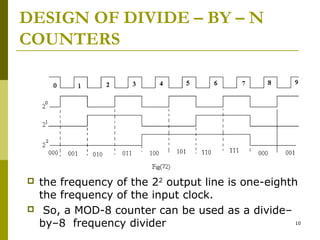

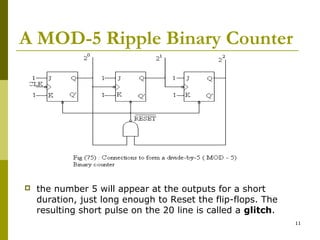

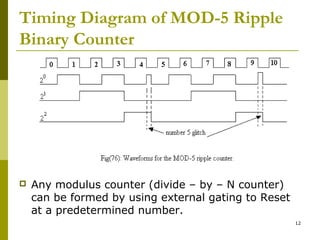

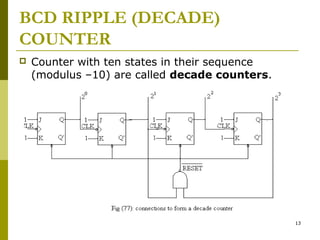

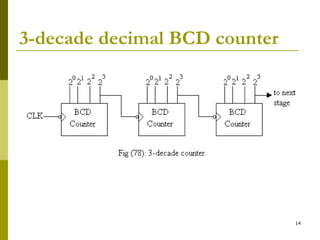

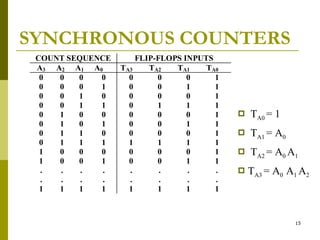

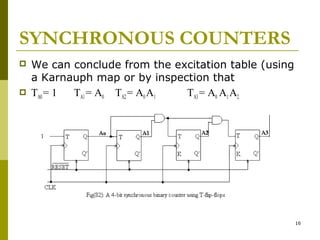

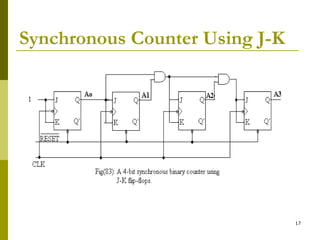

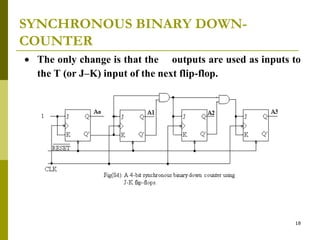

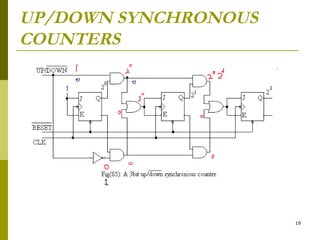

This document discusses different types of counters. It begins by classifying counters as either asynchronous (ripple) or synchronous. It then describes binary, decimal, octal and special counters based on their counting sequences. The document provides examples of 3-bit asynchronous and synchronous up/down counters. It explains how to create divide-by-N counters using MOD-N ripple counters. BCD ripple counters and 3-decade decimal counters are also illustrated. Finally, the timing and operation of synchronous counters is examined along with synchronous down and up/down counters.