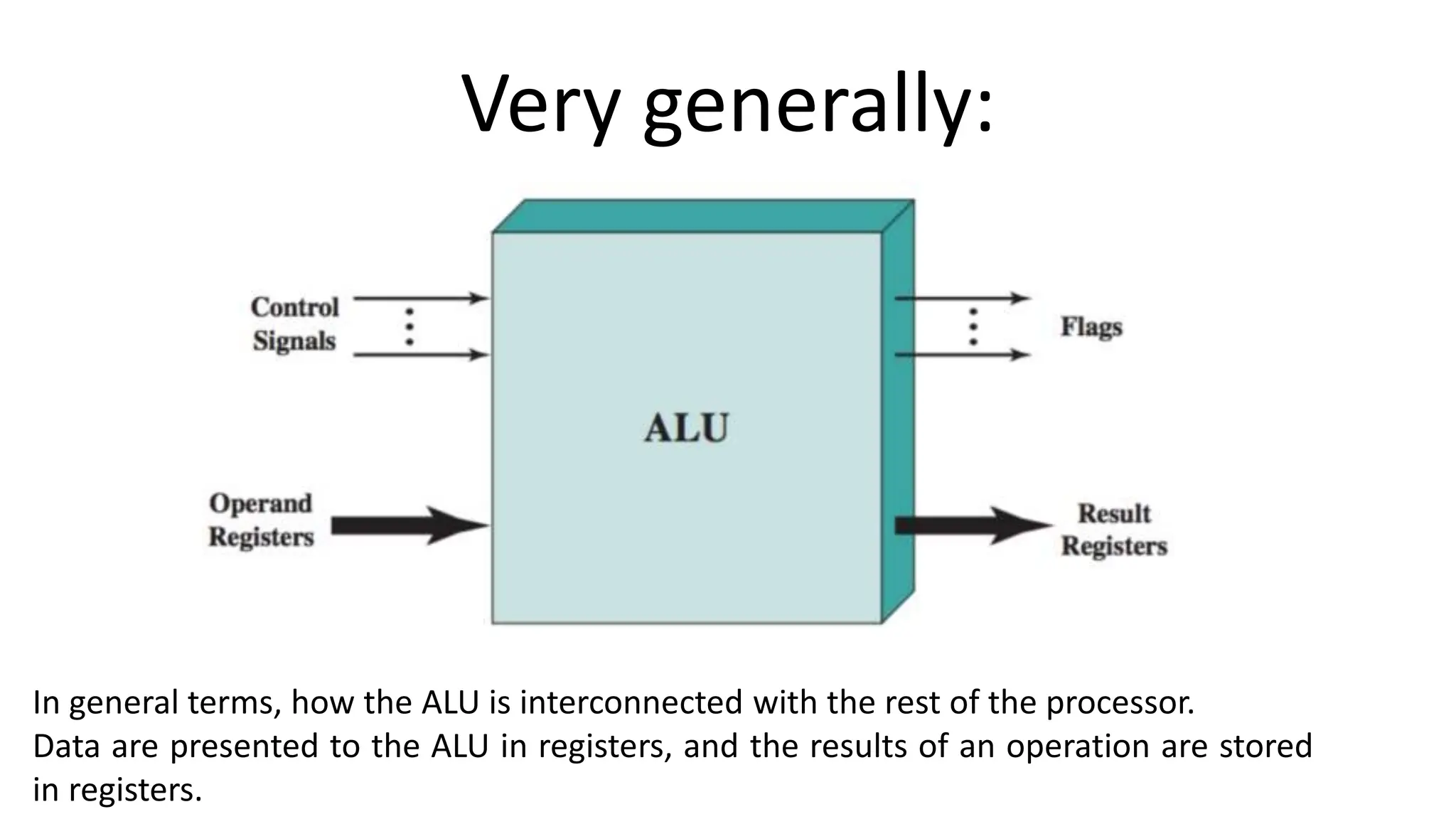

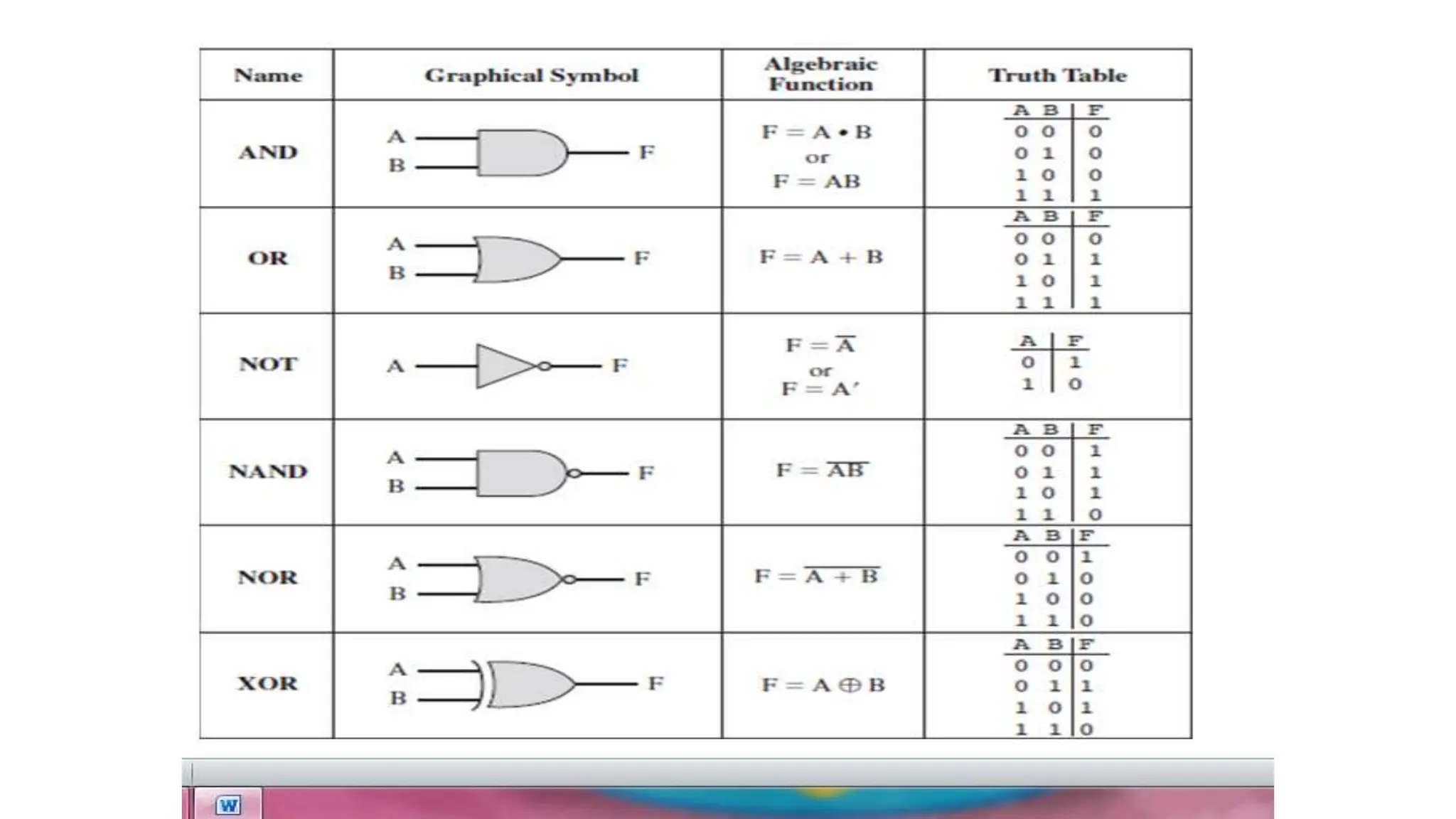

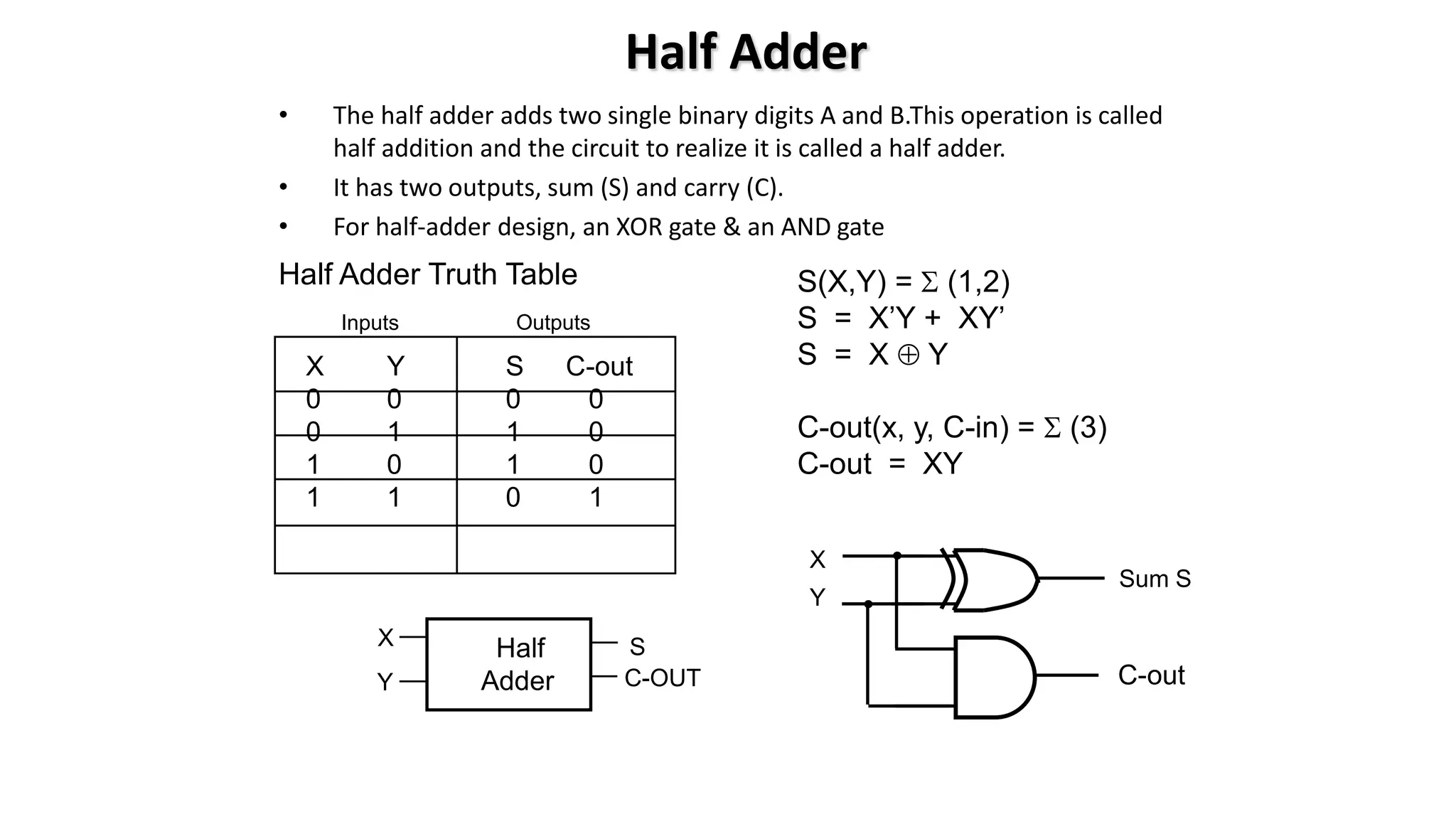

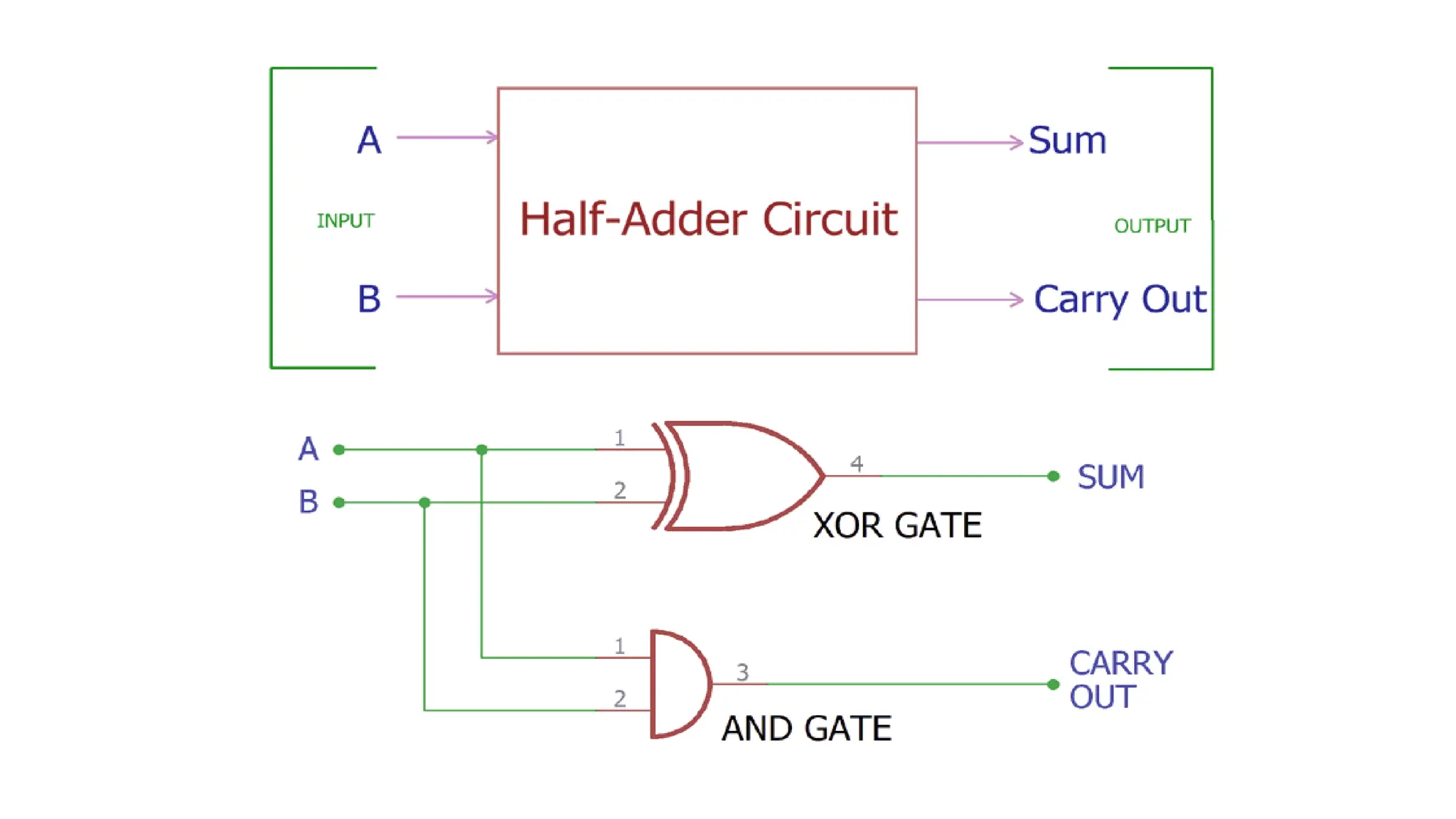

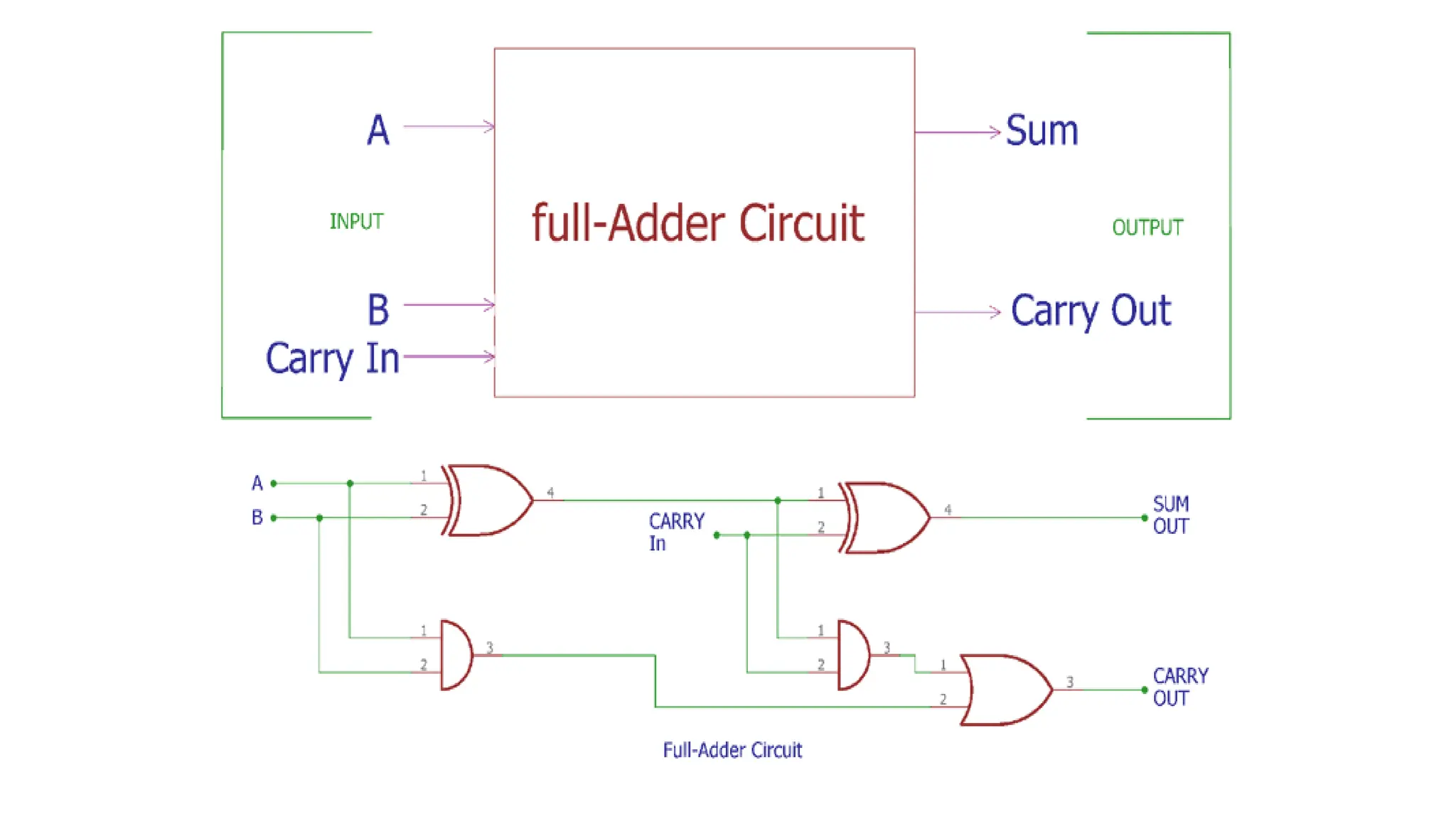

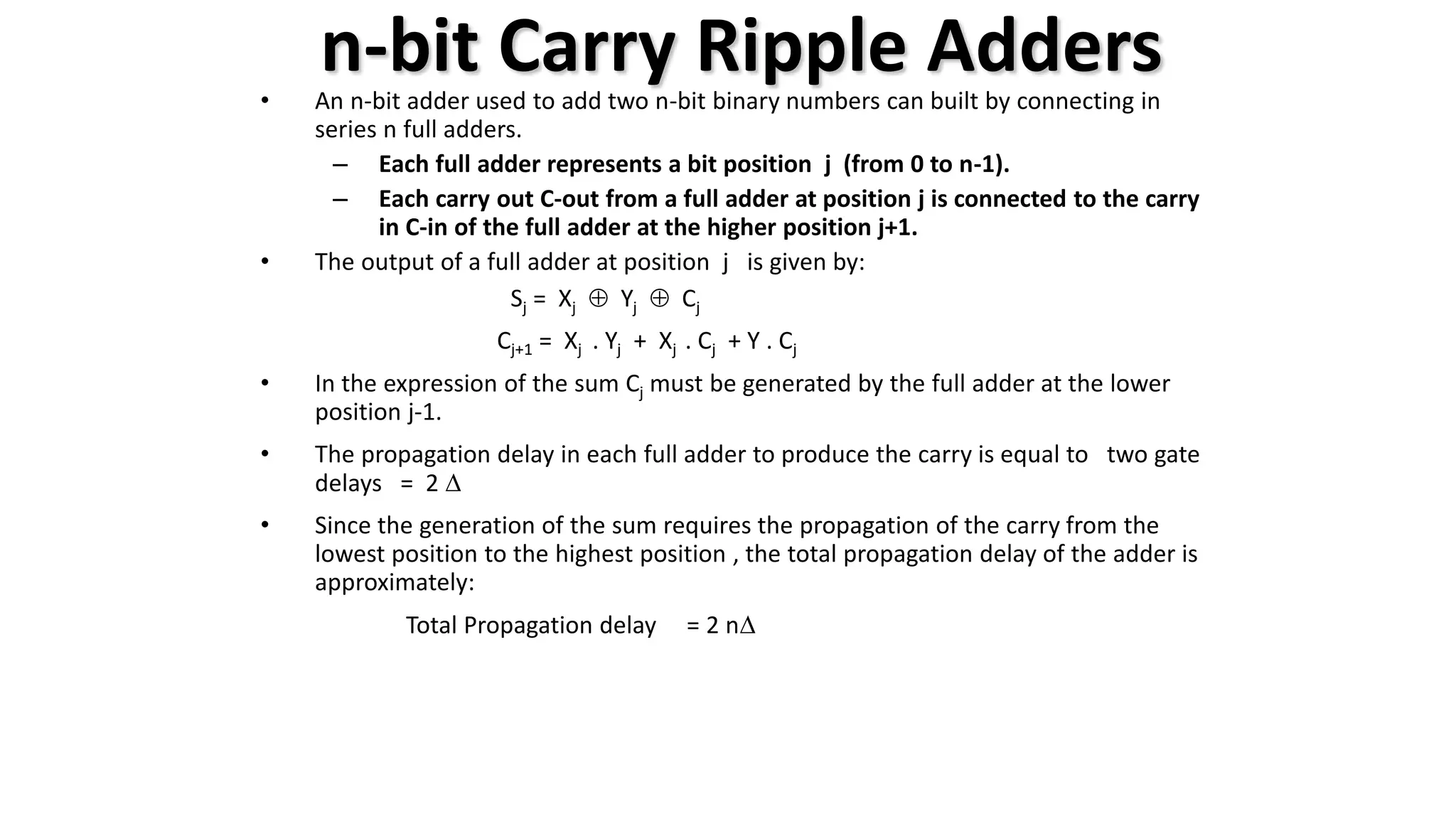

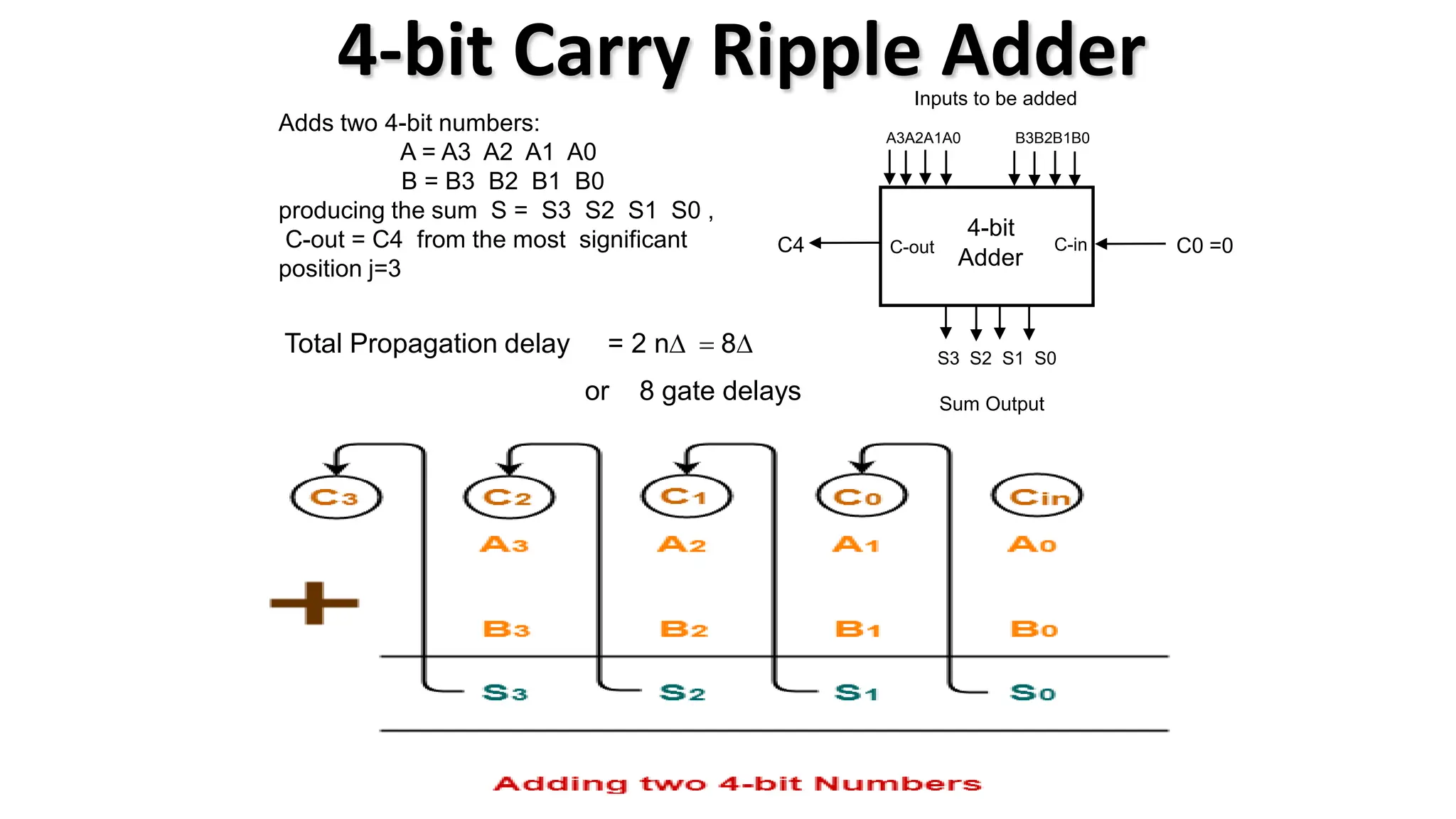

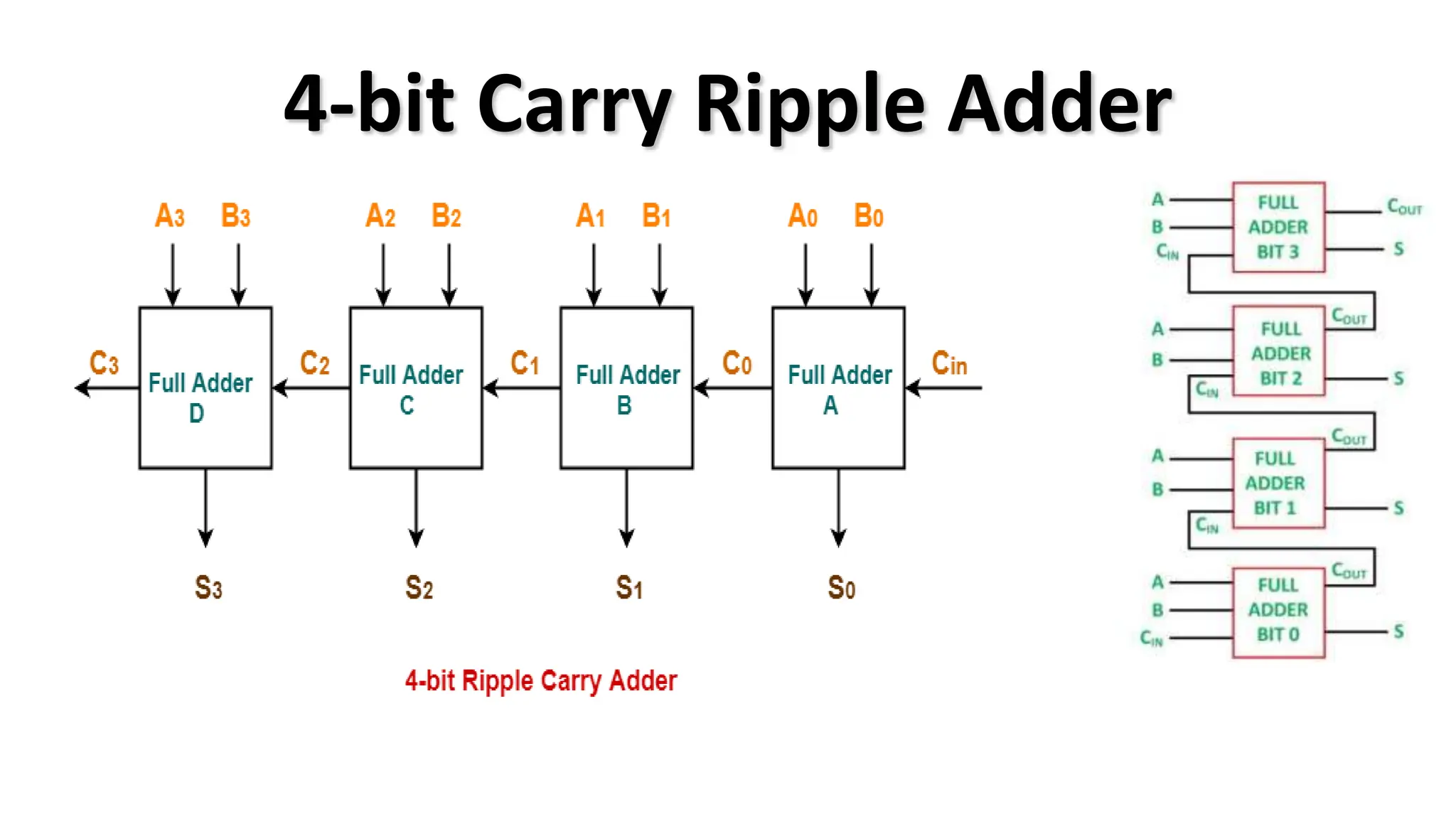

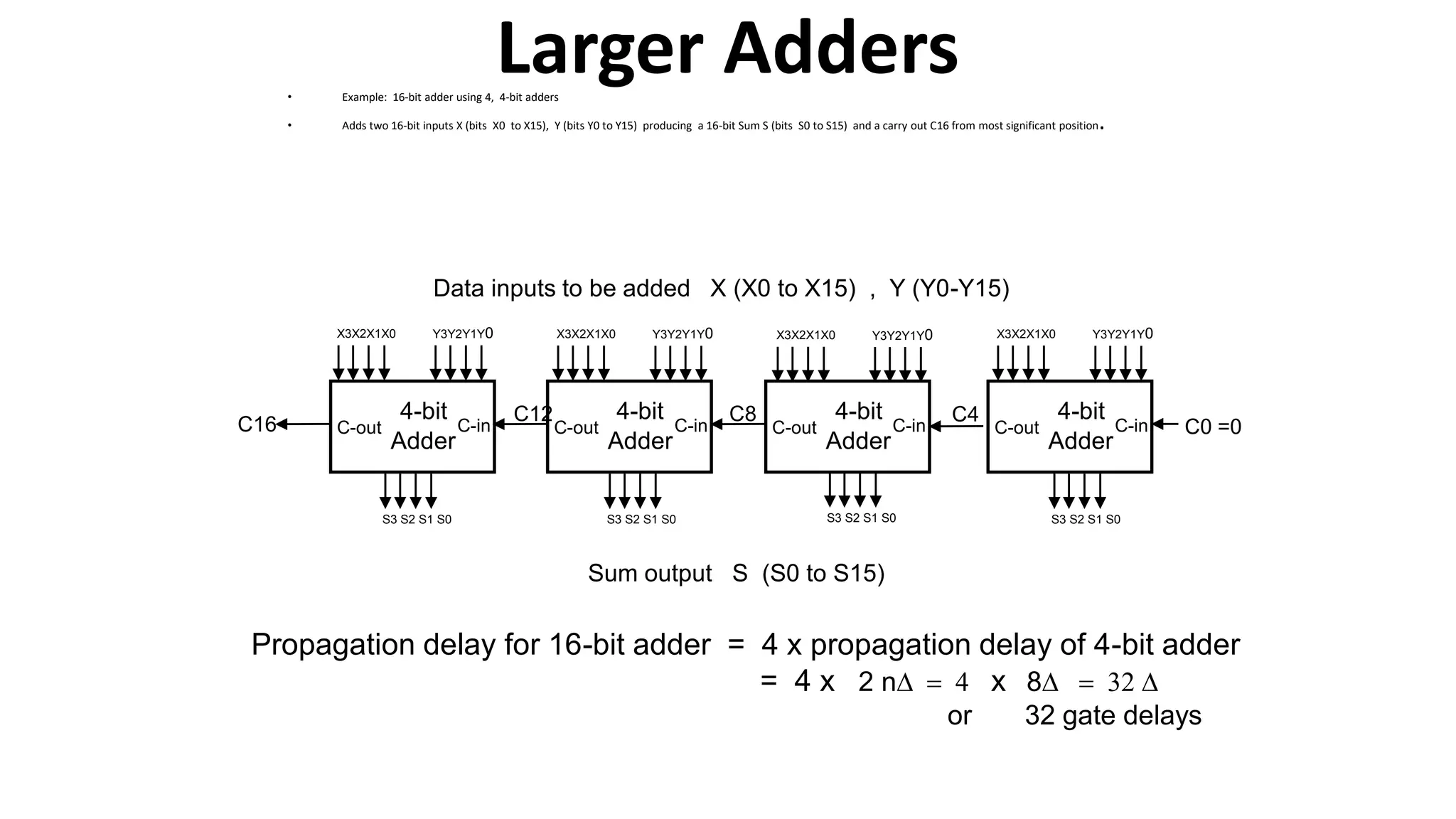

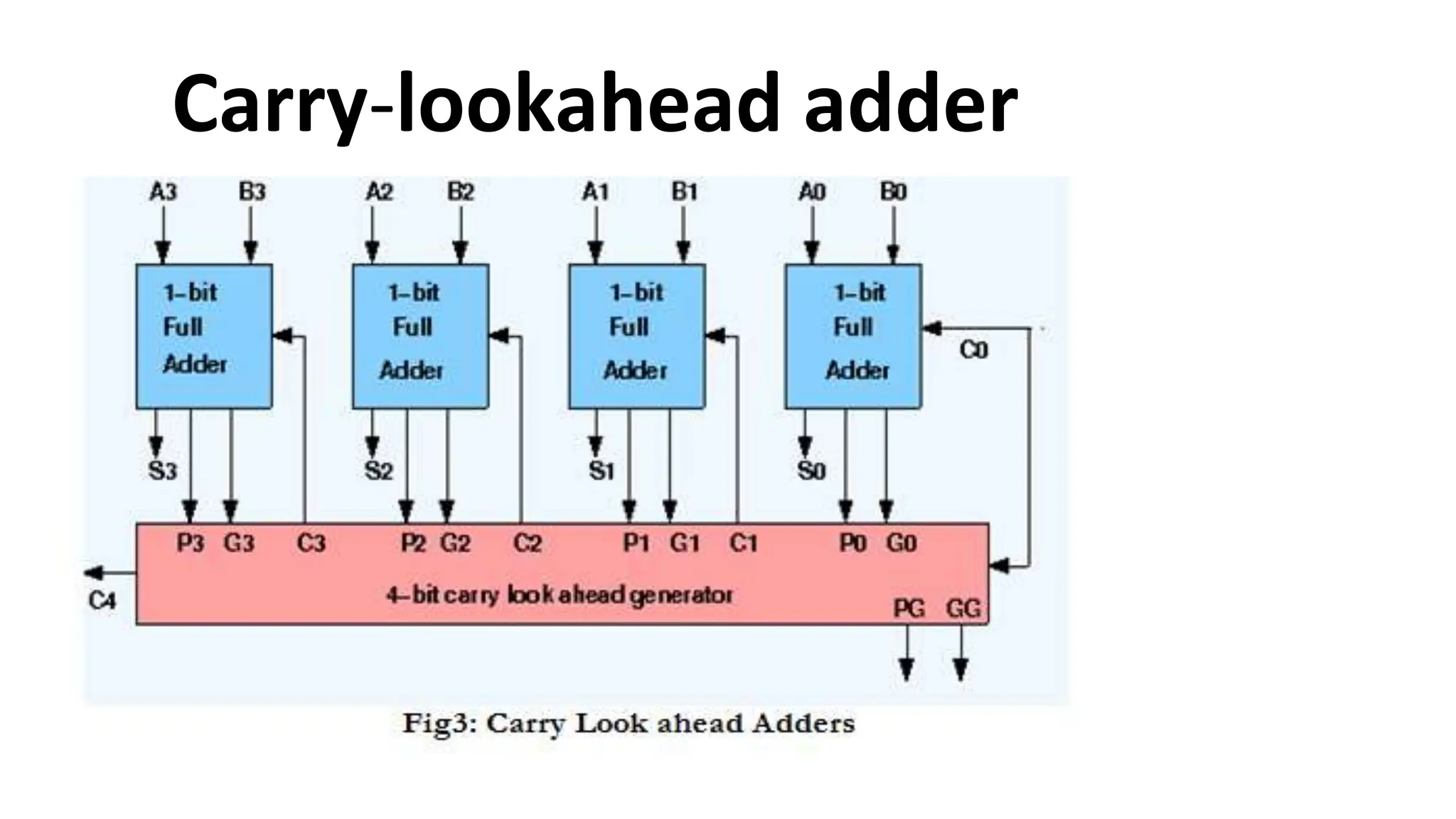

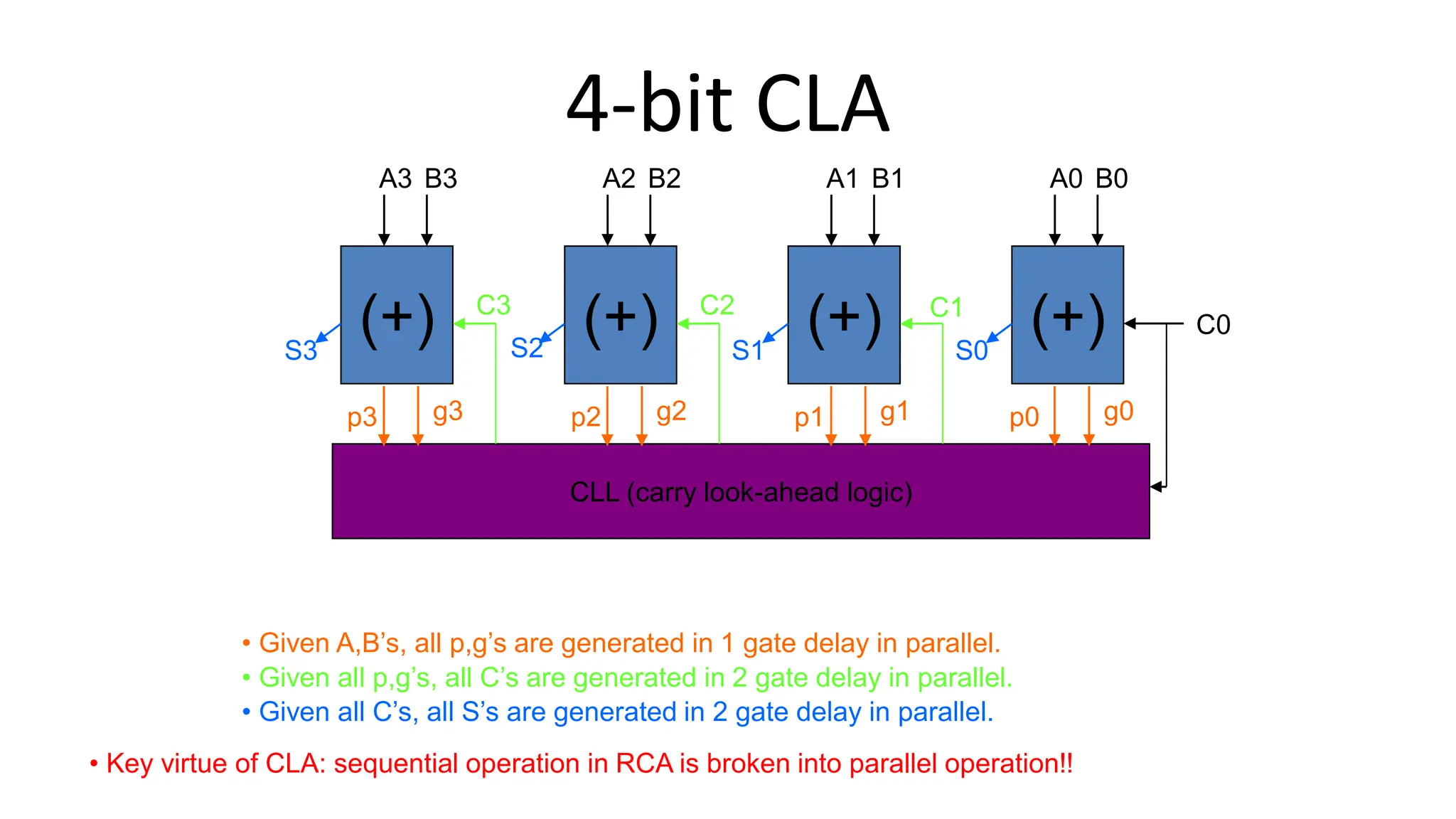

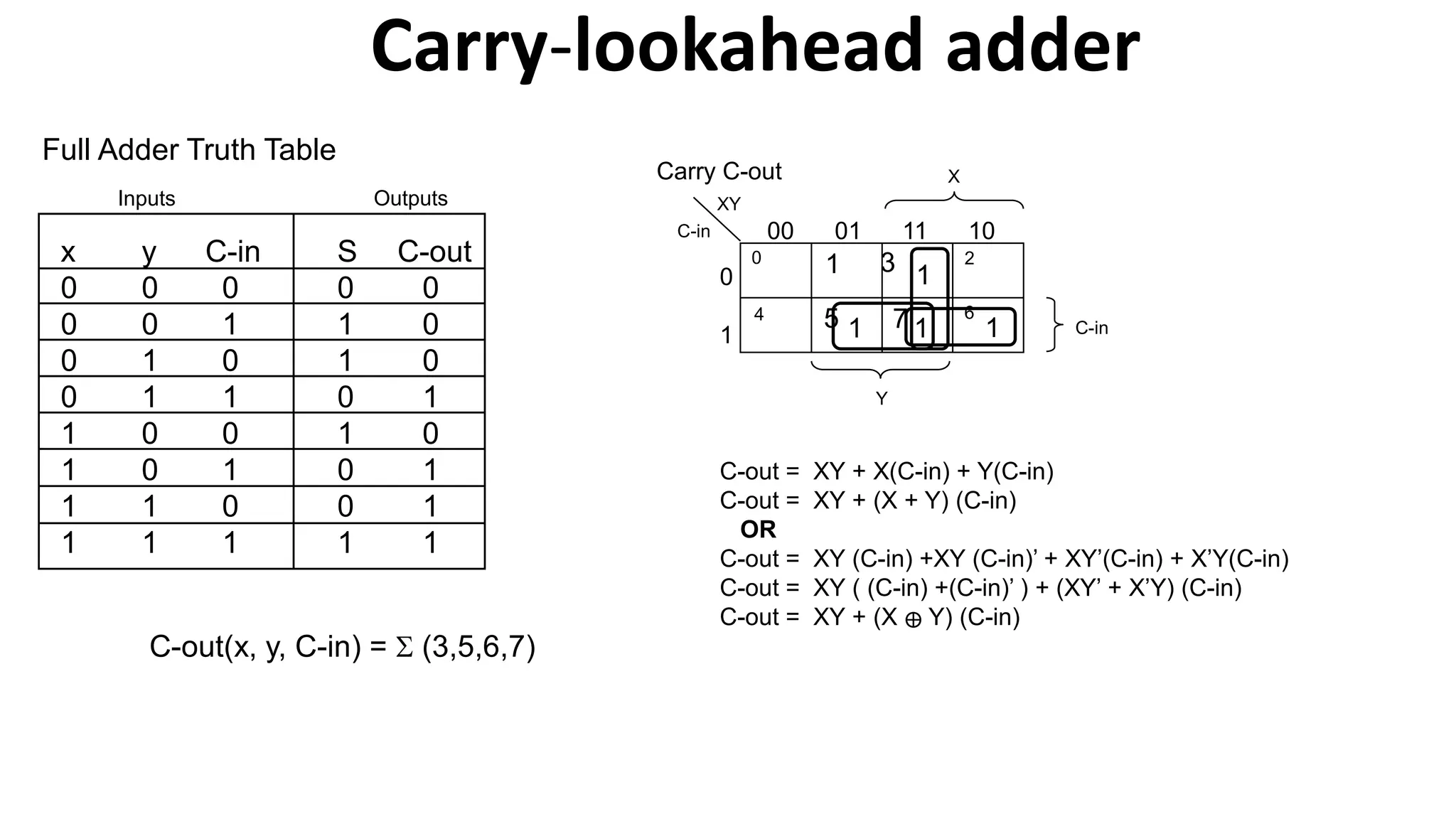

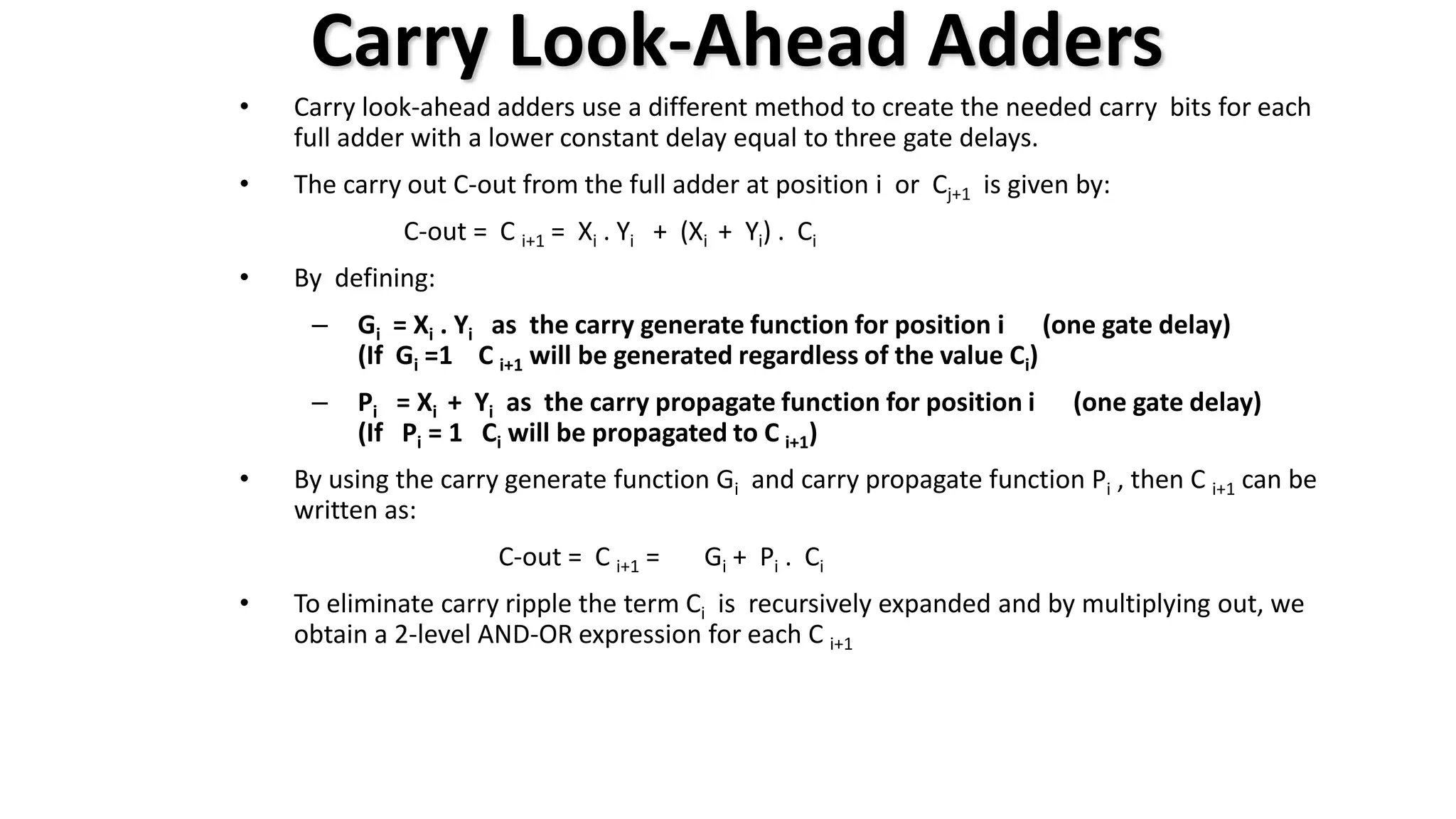

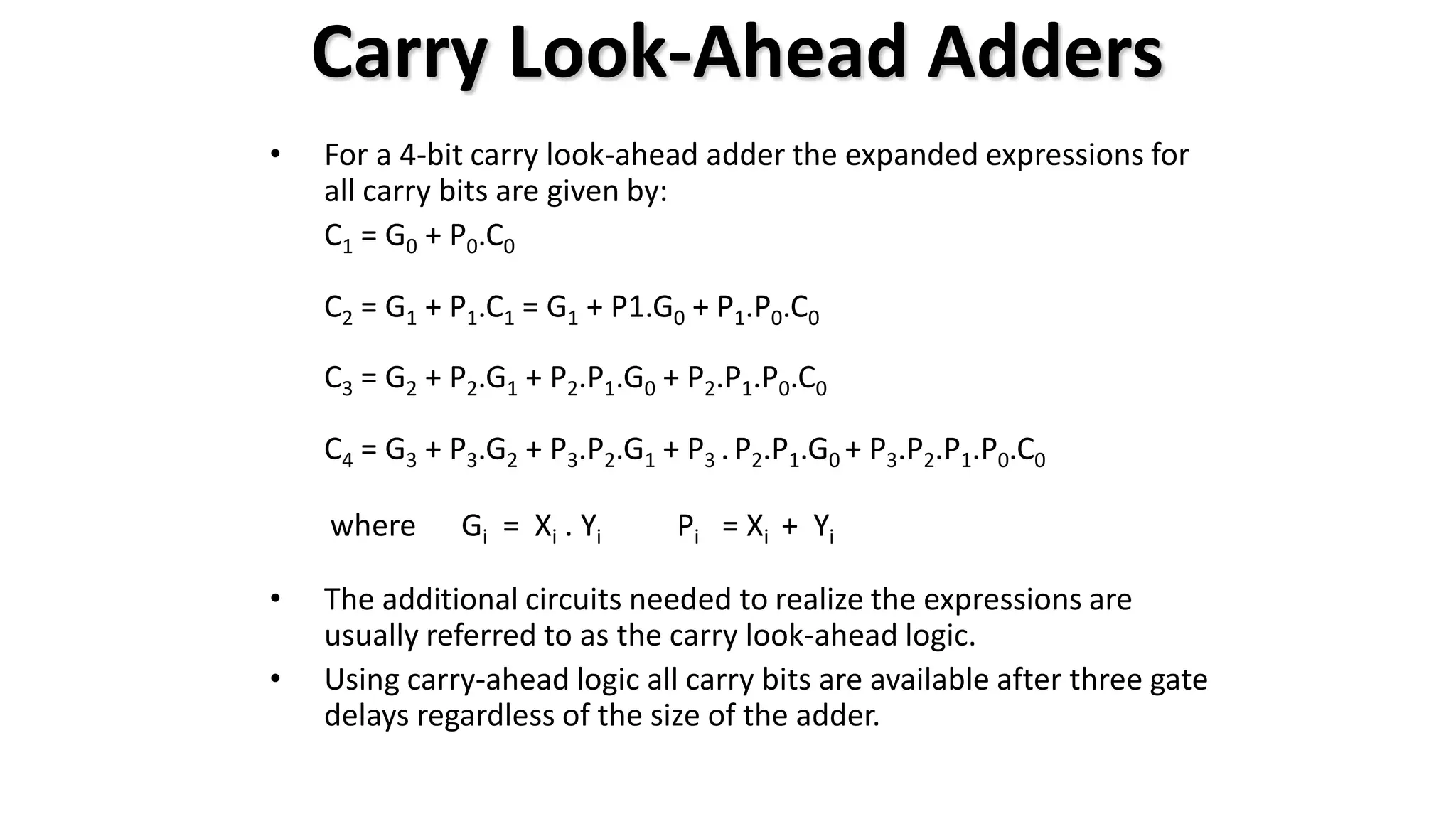

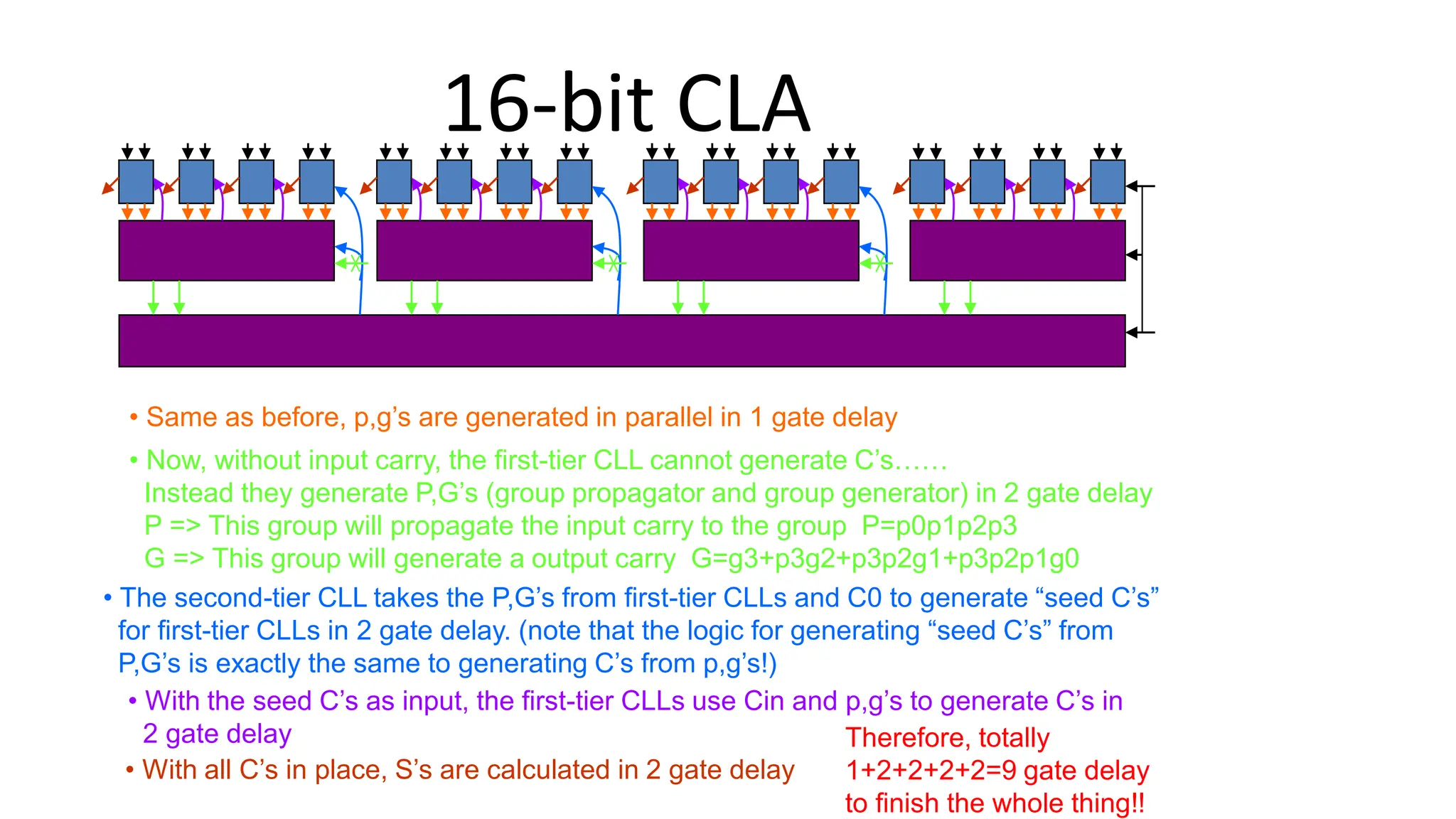

The document discusses the arithmetic and logic unit (ALU) in computer organization, detailing its role in performing arithmetic and logical operations, as well as the various logic gates it utilizes. It covers types of adders, including half adders and full adders, and explains the concept of carry ripple adders and carry-lookahead adders, highlighting their designs and advantages. Key concepts such as propagation delay and methods to speed up addition processes with carry-lookahead logic are also addressed.