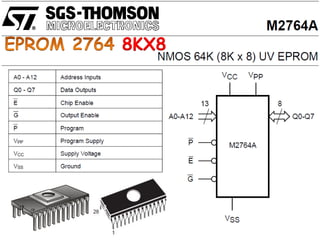

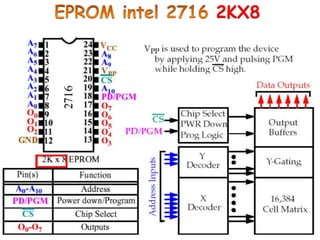

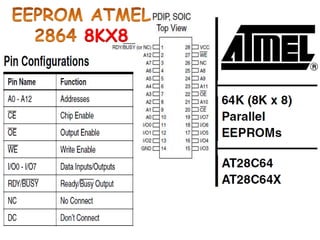

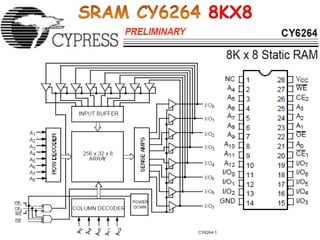

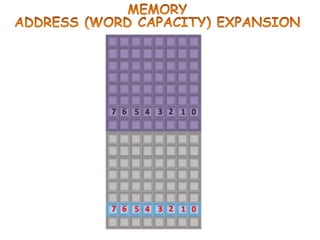

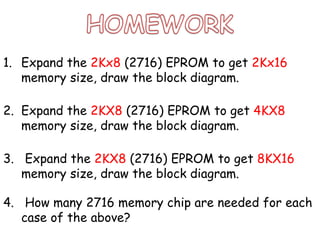

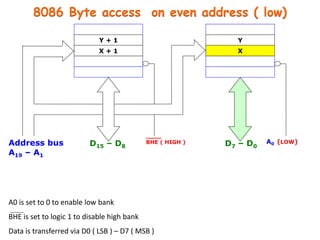

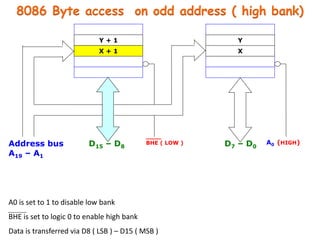

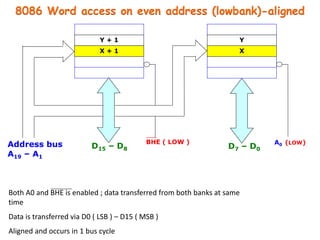

This document discusses different types of computer memory technologies including ROM, RAM, and their variants. It also provides examples of memory expansion by combining multiple memory chips. Specifically, it shows how to expand a 2Kx8 EPROM chip to larger memory sizes like 2Kx16, 4Kx8, and 8Kx16 by using multiple chips. Additionally, it demonstrates 8086 memory access for byte and word sizes using the address bus, data bus and control lines like BHE and A0.