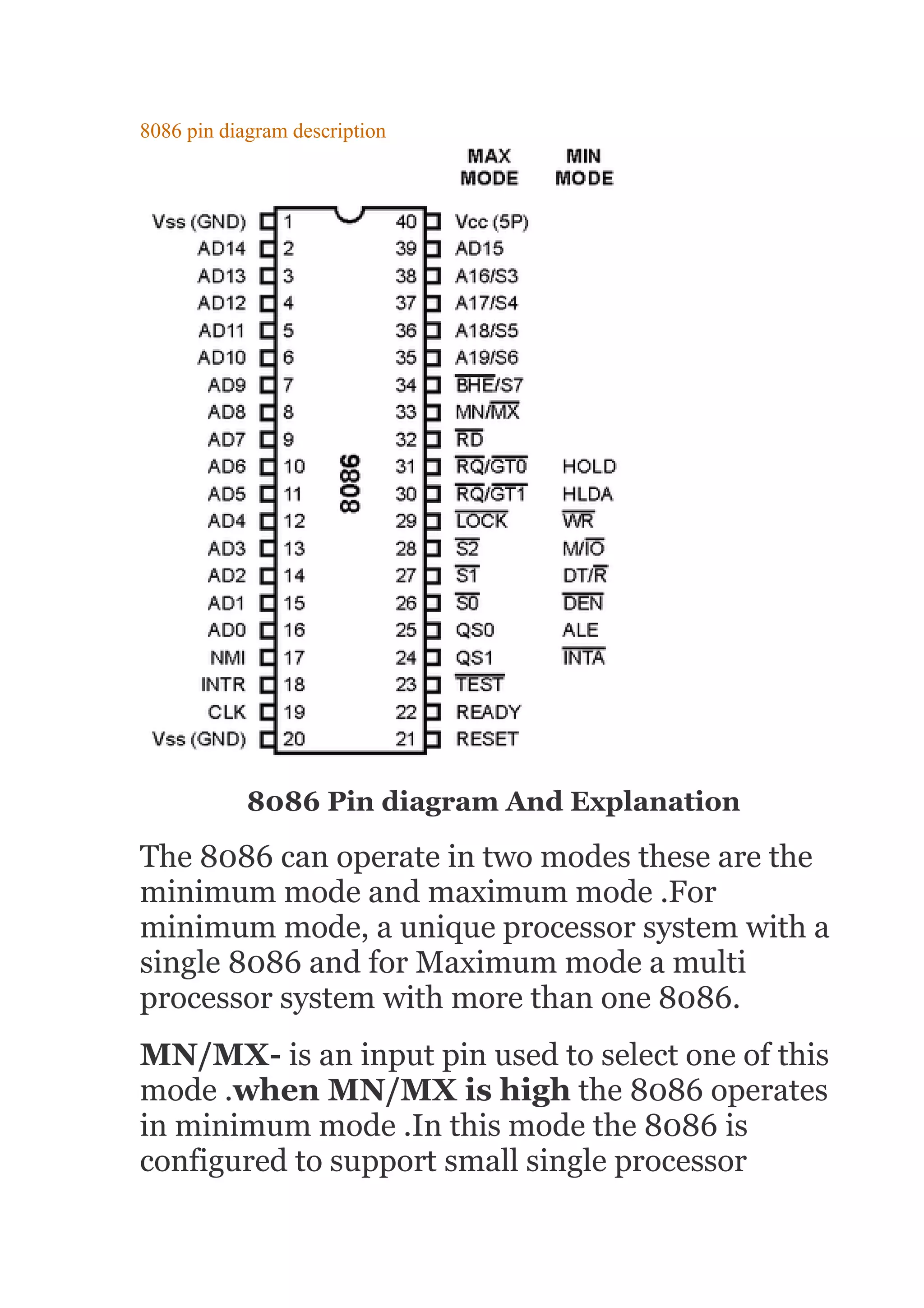

The document describes the pins of the 8086 microprocessor. It operates in either minimum or maximum mode depending on the state of the MN/MX pin. The AD0-AD15 pins are used for the lower 16-bits of addressing or data. The upper 4 address lines are multiplexed with status signals. The BHE/S7 pin is used for bus high enable during instruction execution.