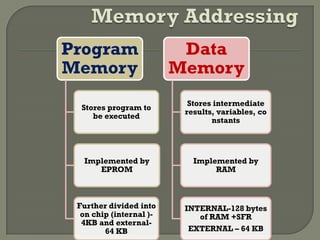

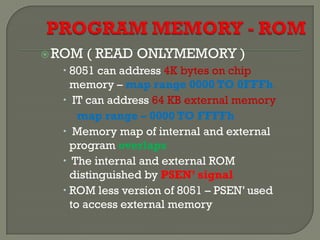

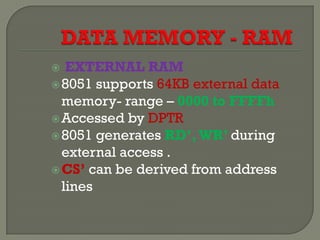

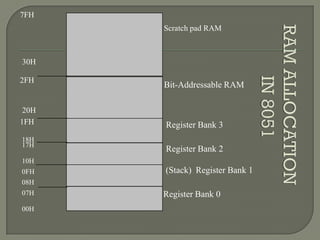

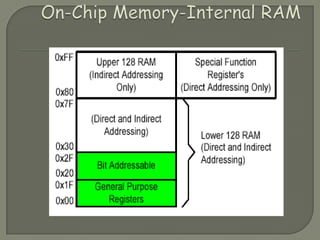

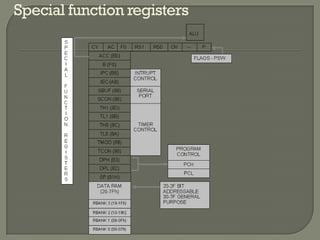

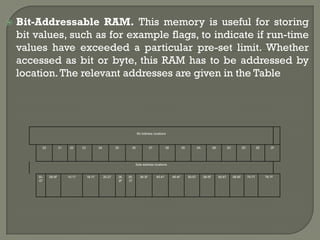

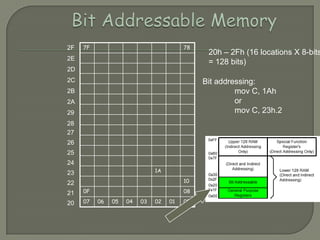

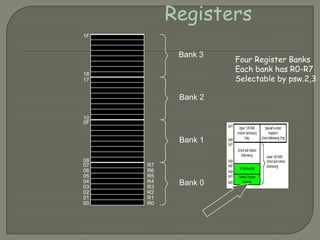

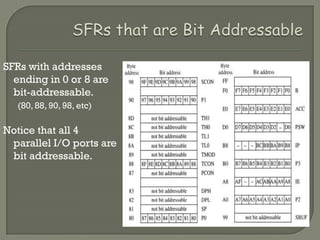

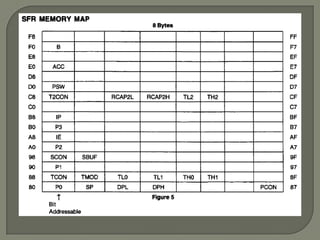

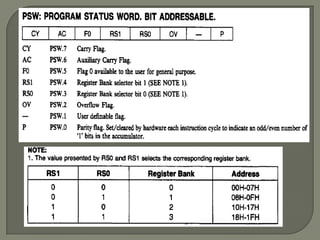

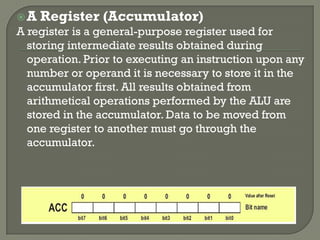

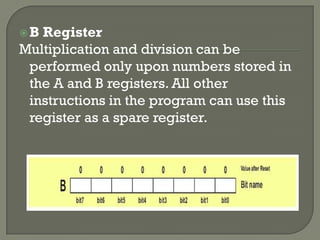

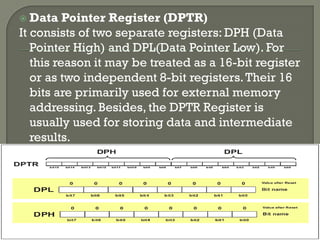

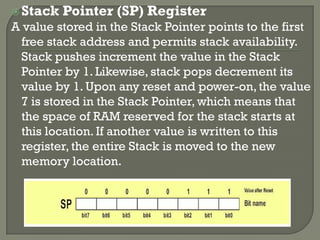

The document discusses the memory organization and registers of the 8051 microcontroller. It describes the program memory and data memory, which are implemented using EPROM and RAM respectively. It then discusses the different registers of the 8051 including the accumulator, B register, data pointer register, stack pointer register, and special function registers. The special function registers are used for tasks like timer control and interrupt control.