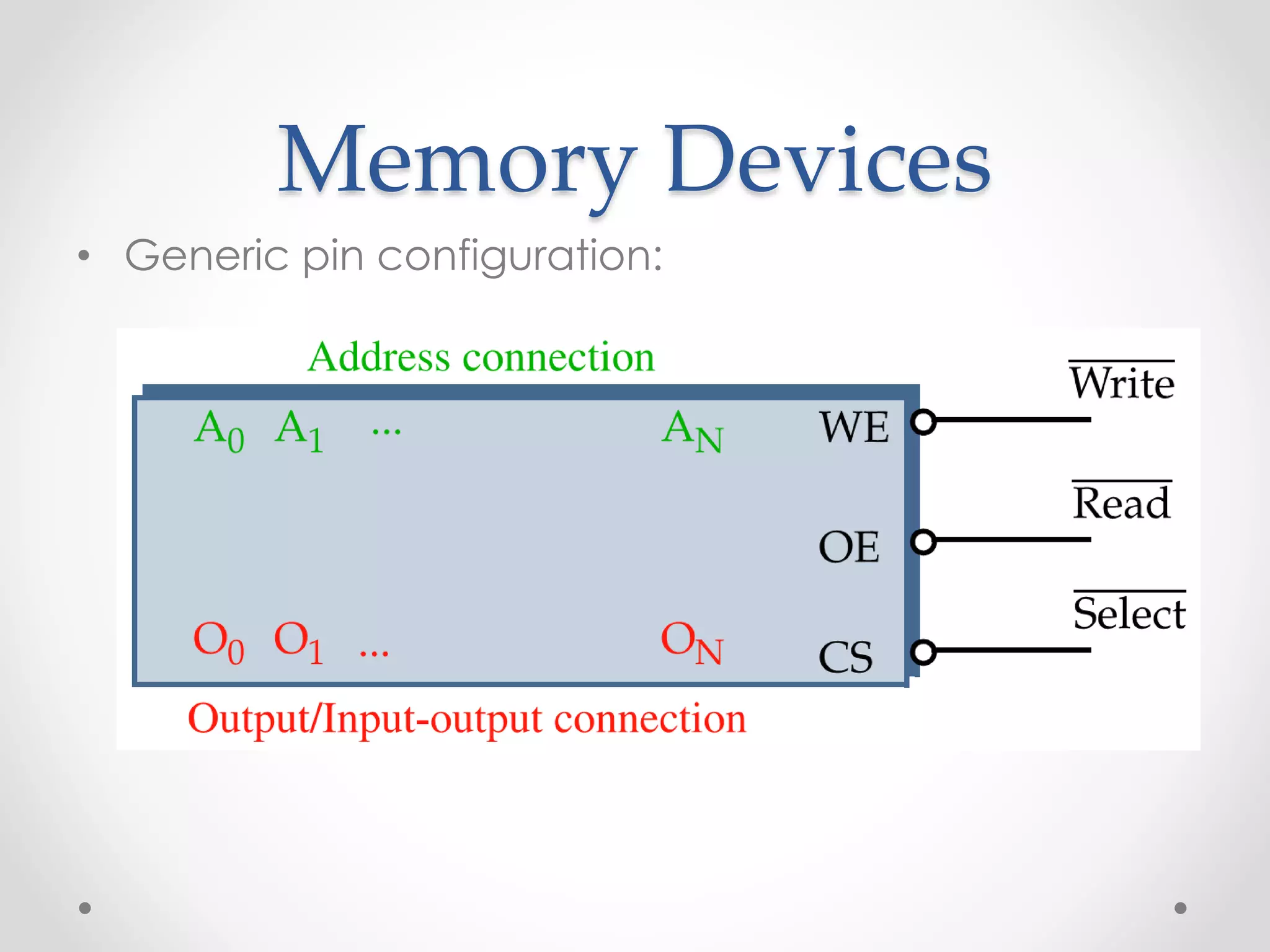

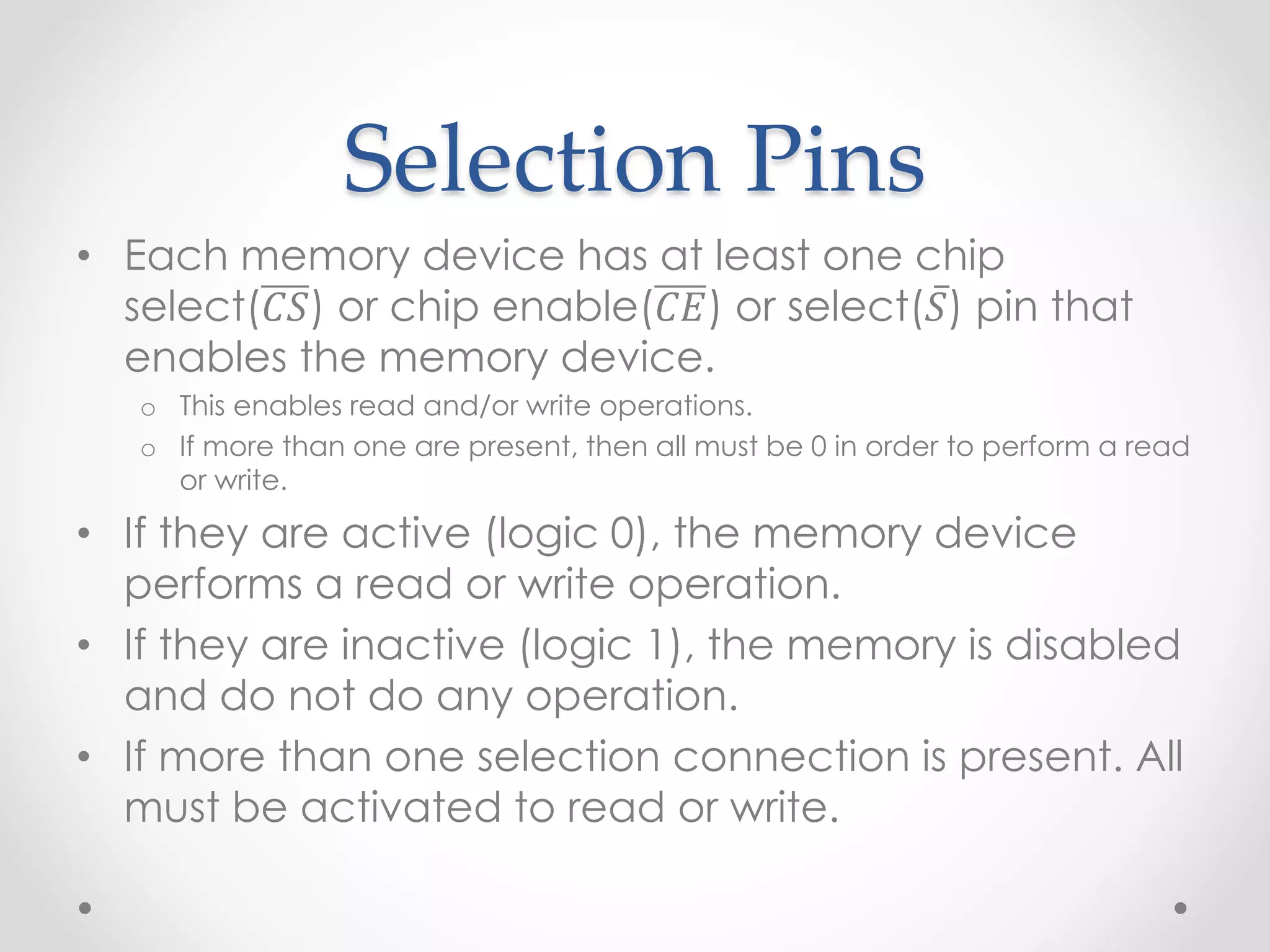

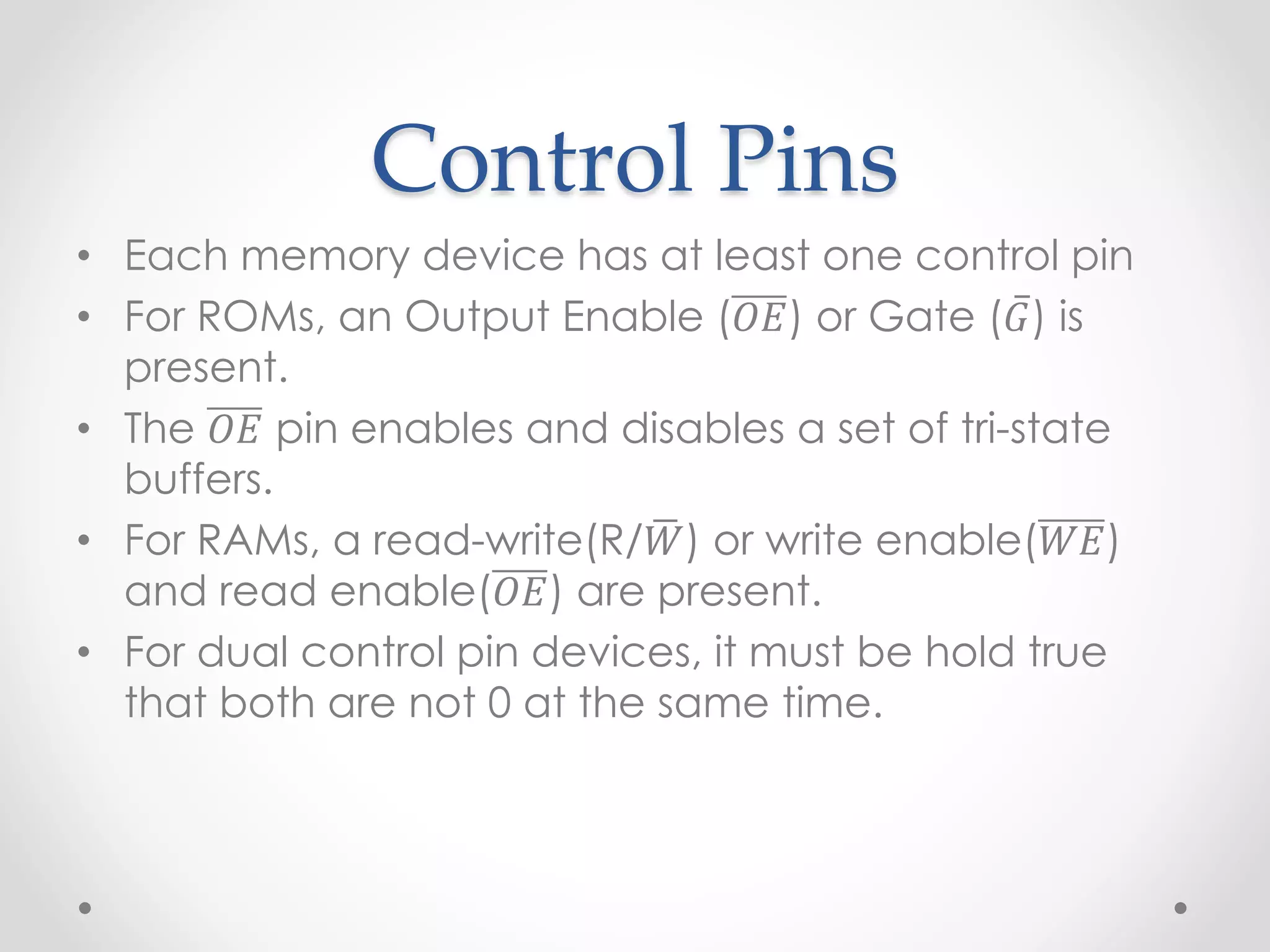

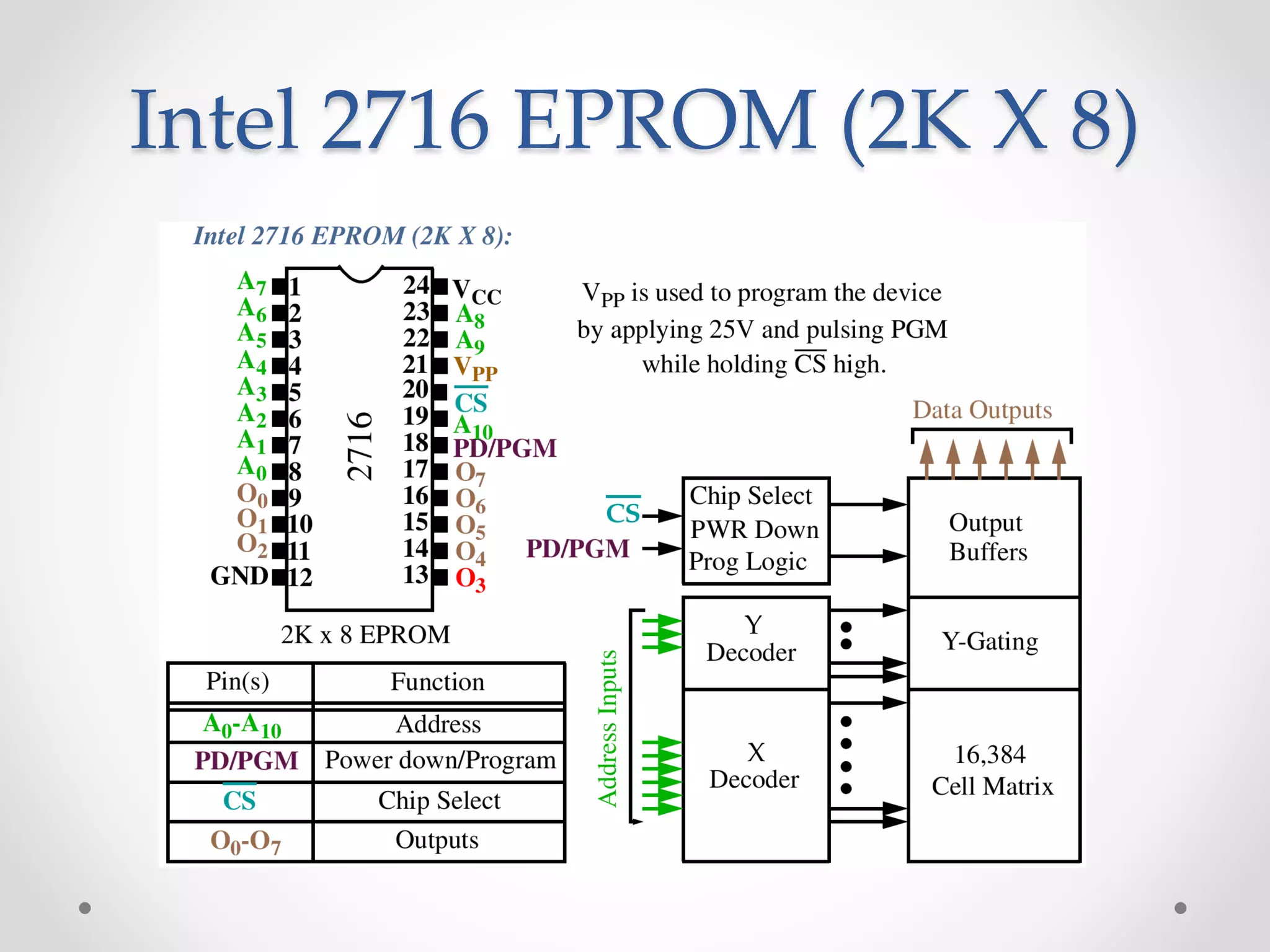

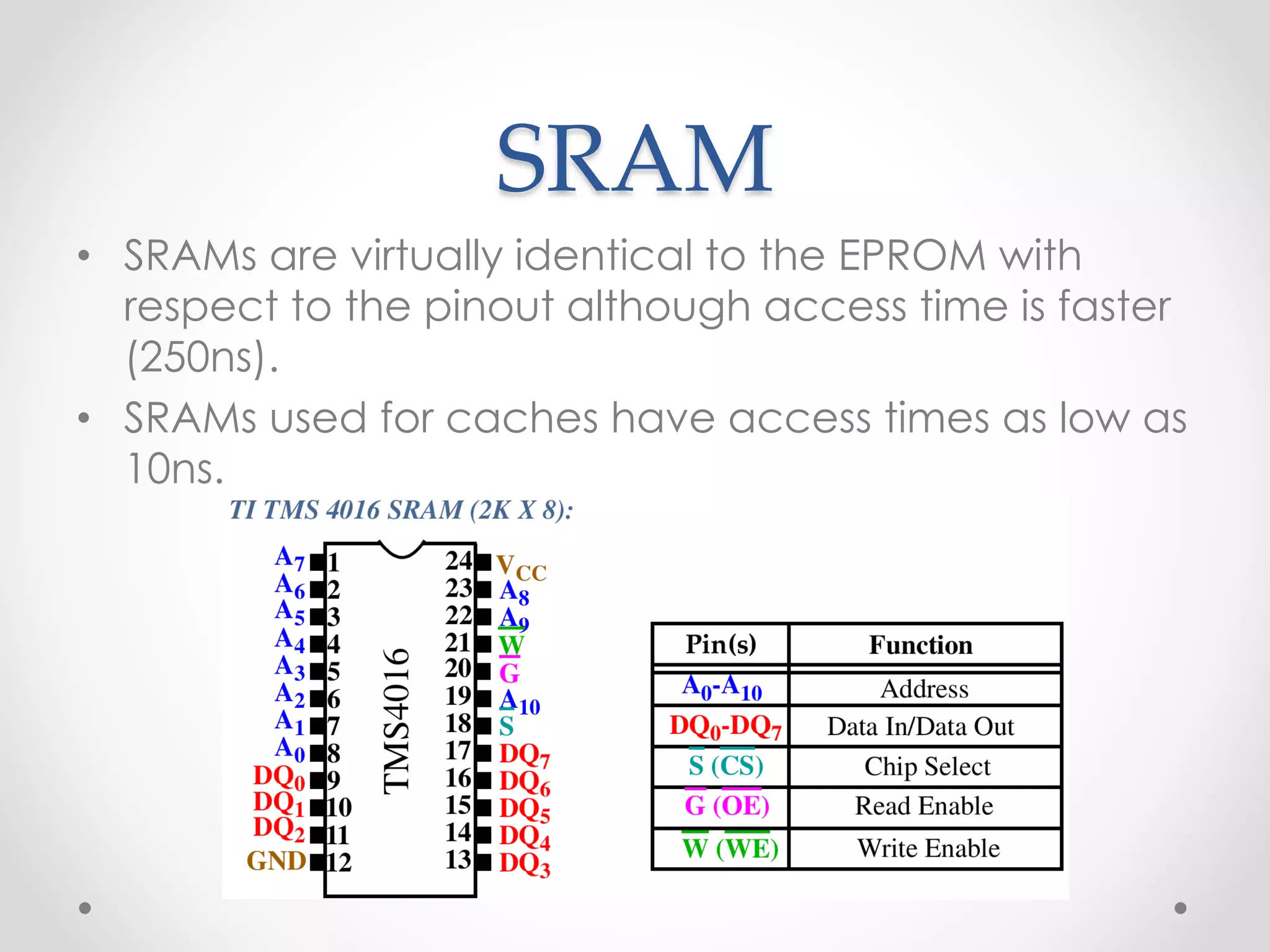

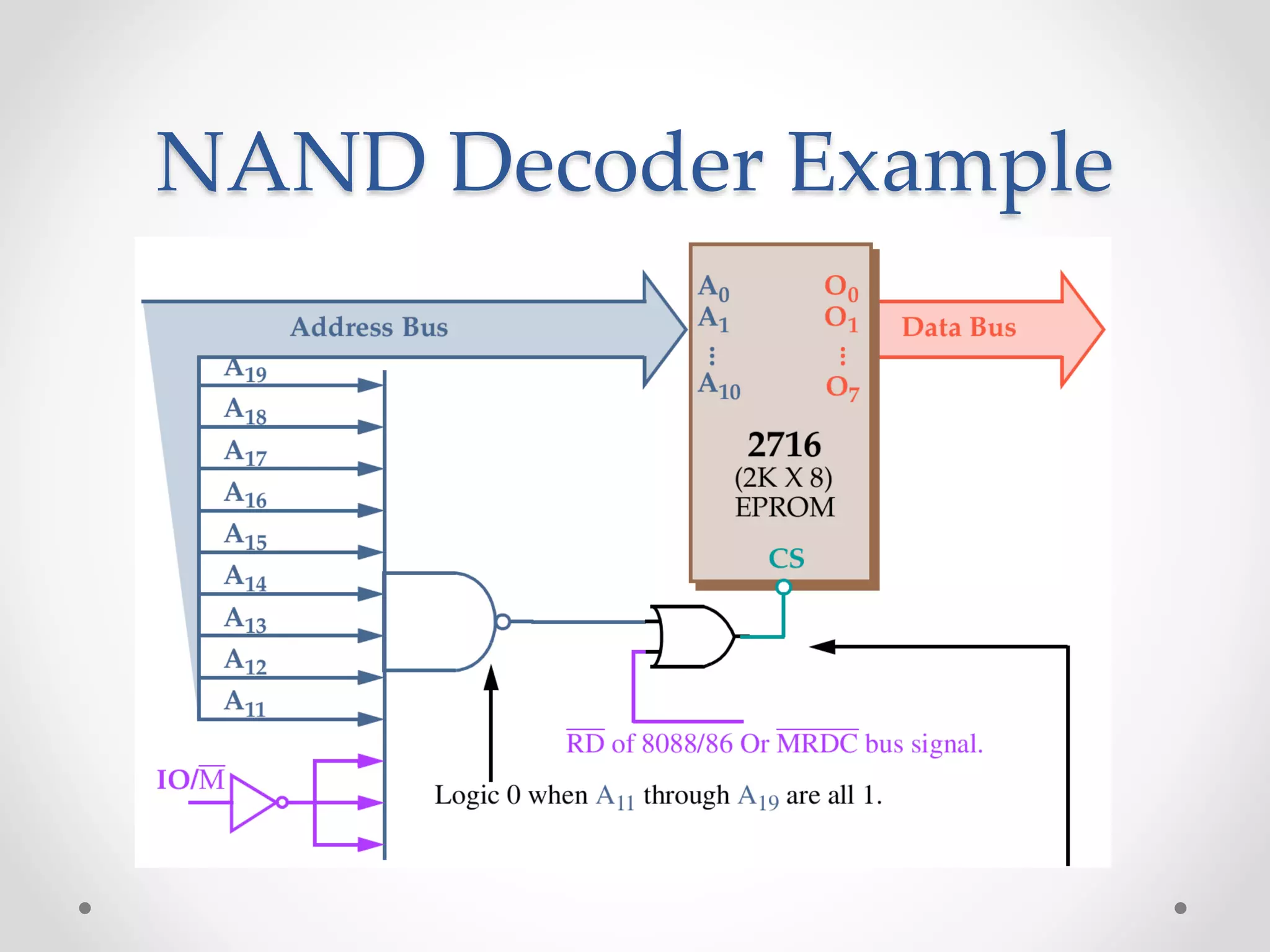

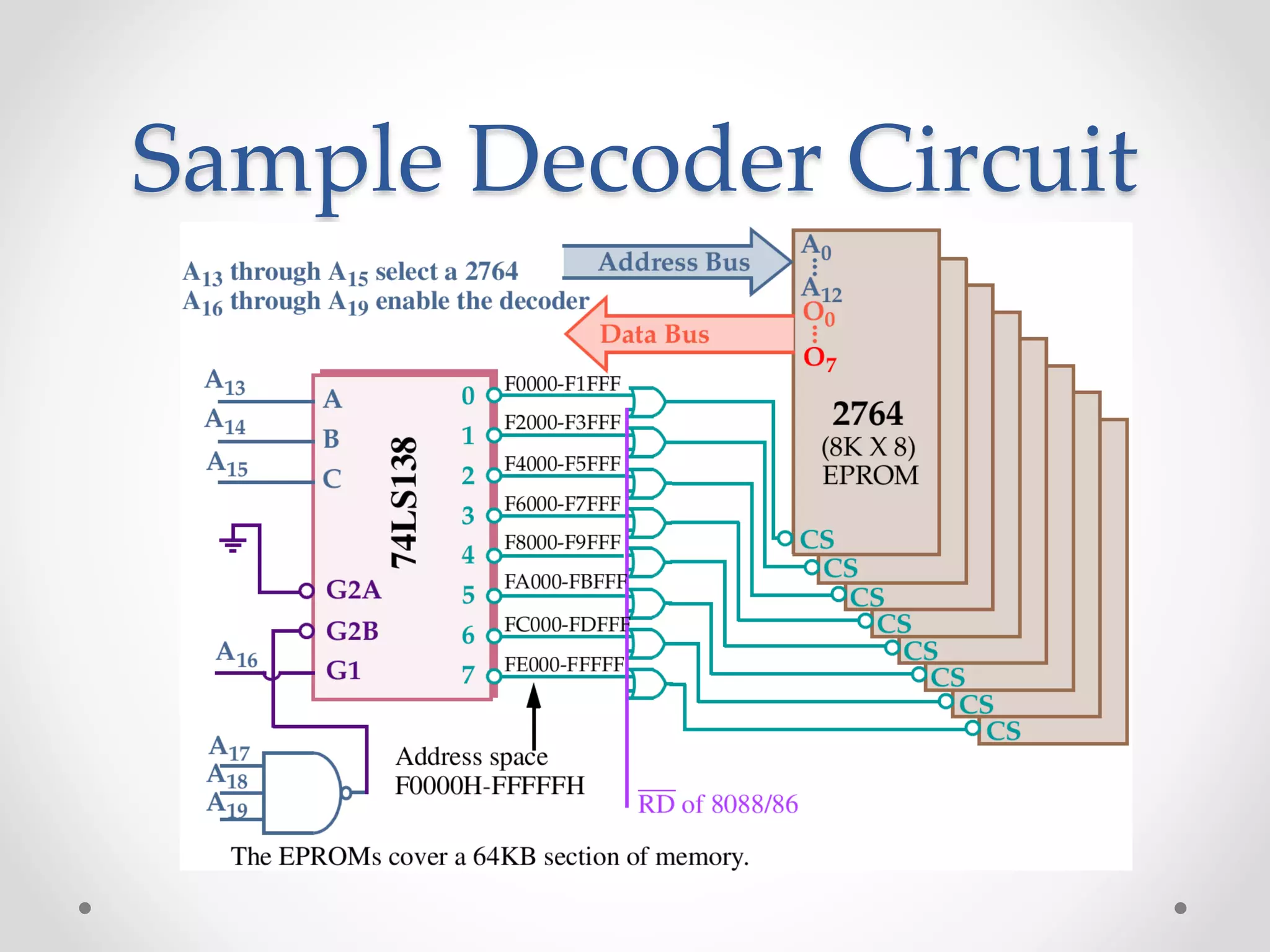

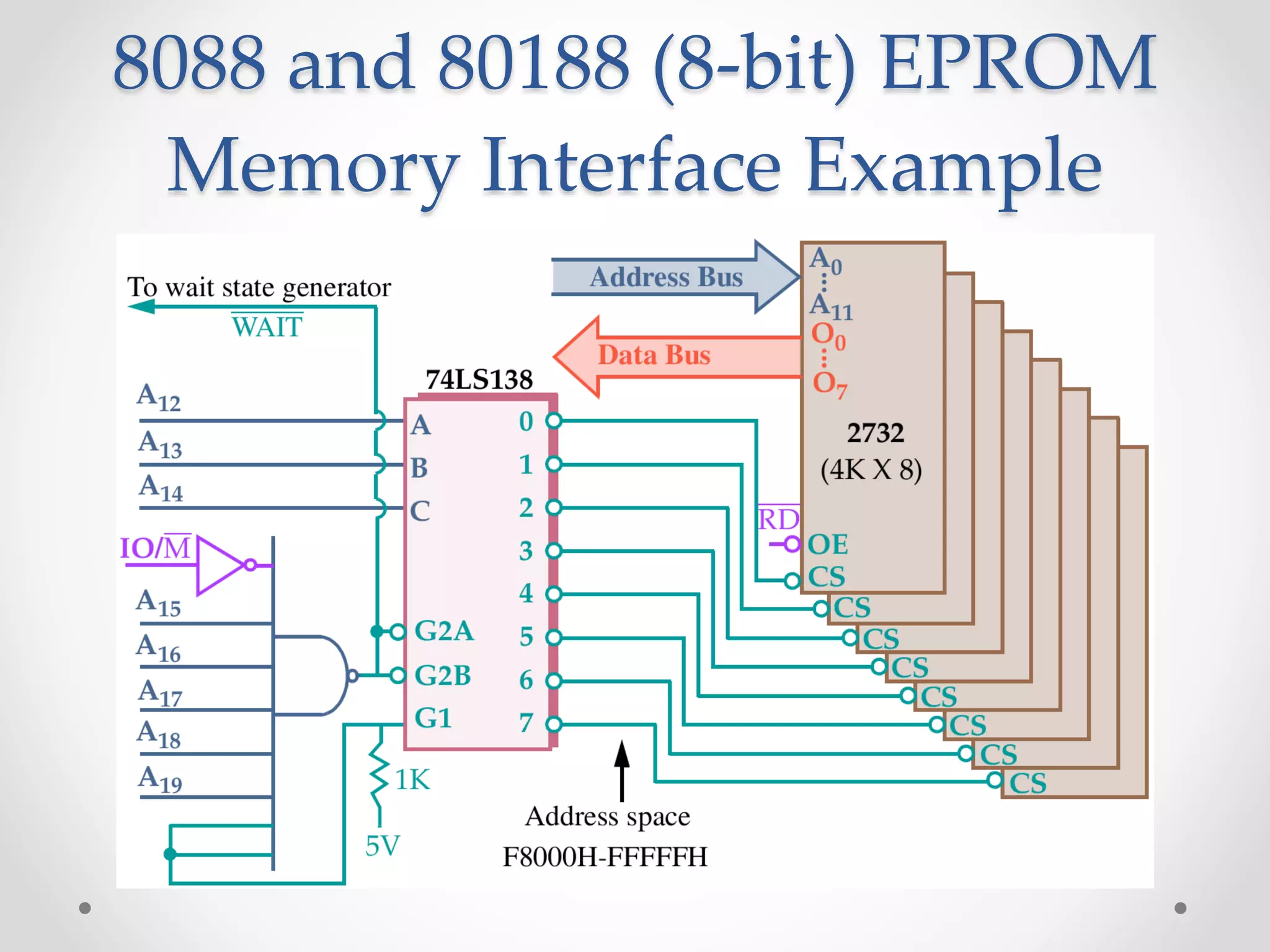

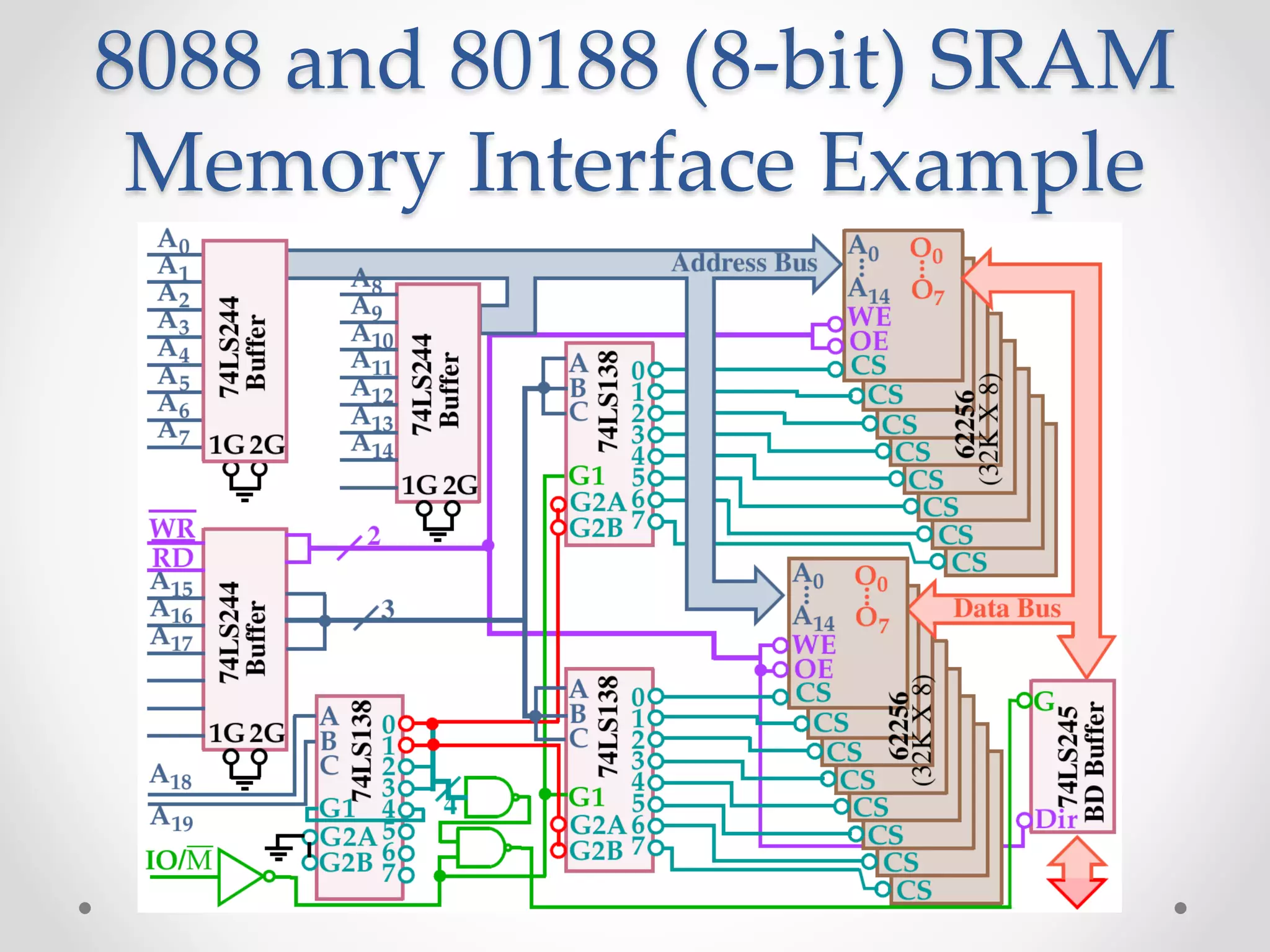

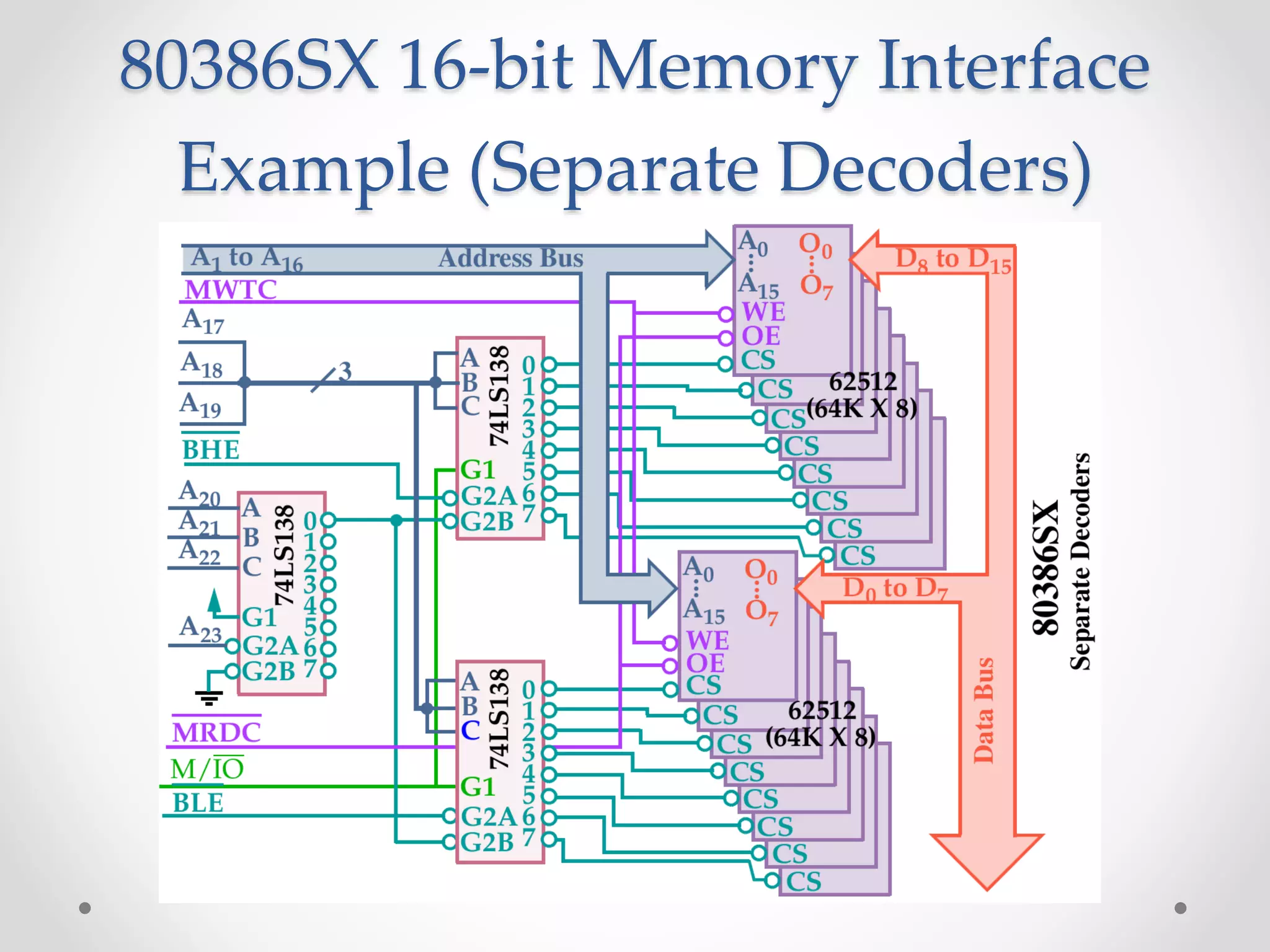

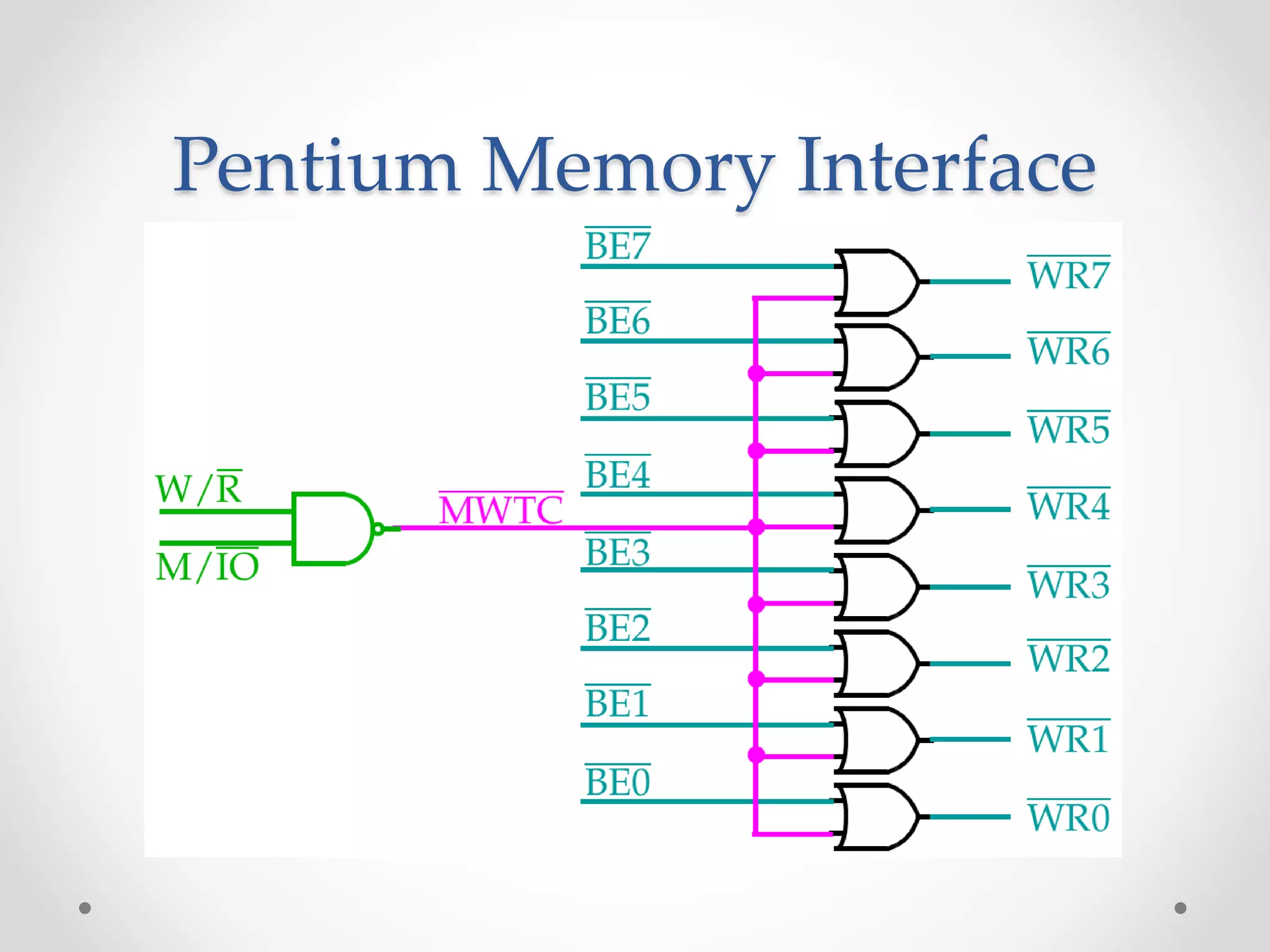

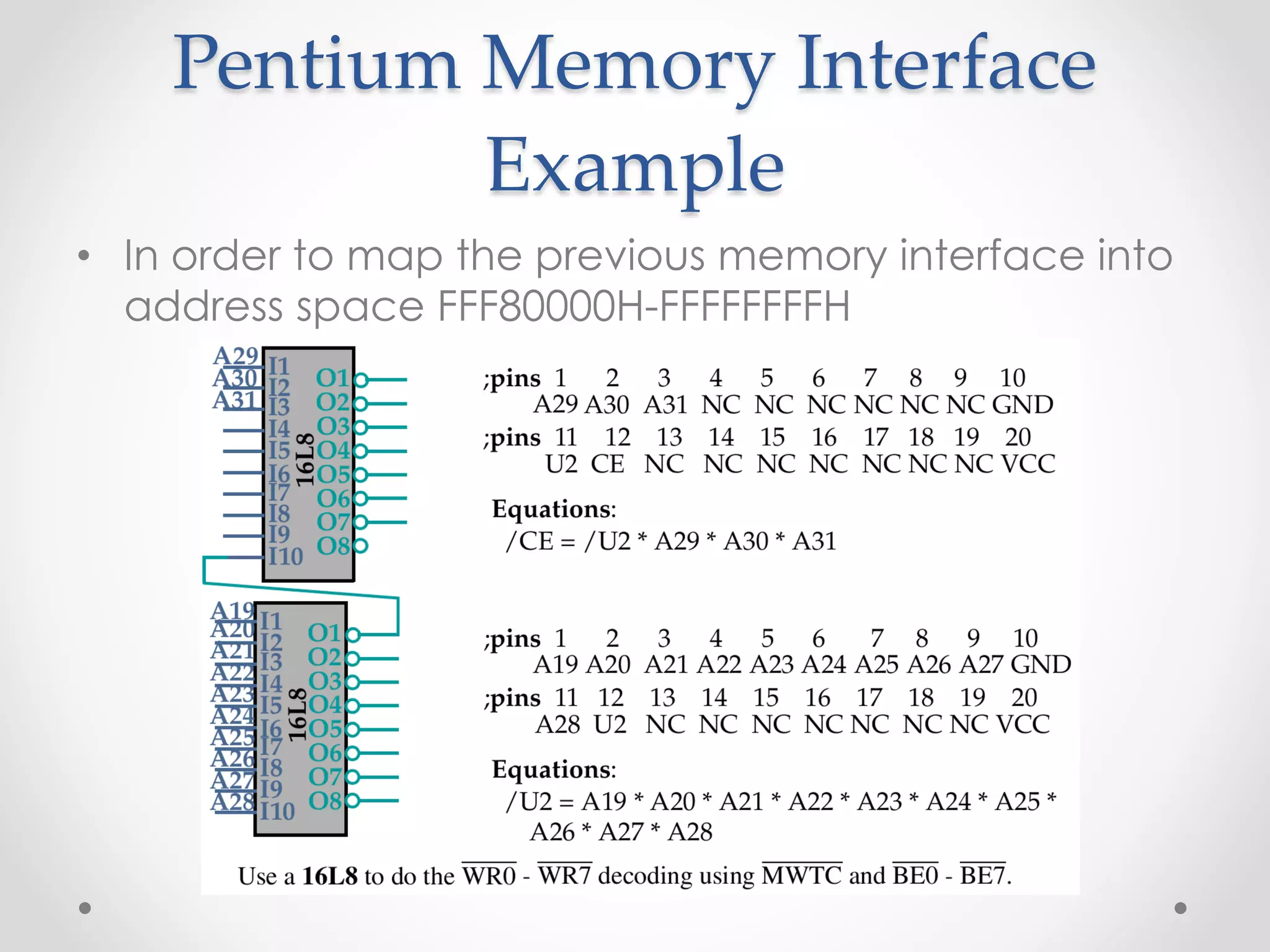

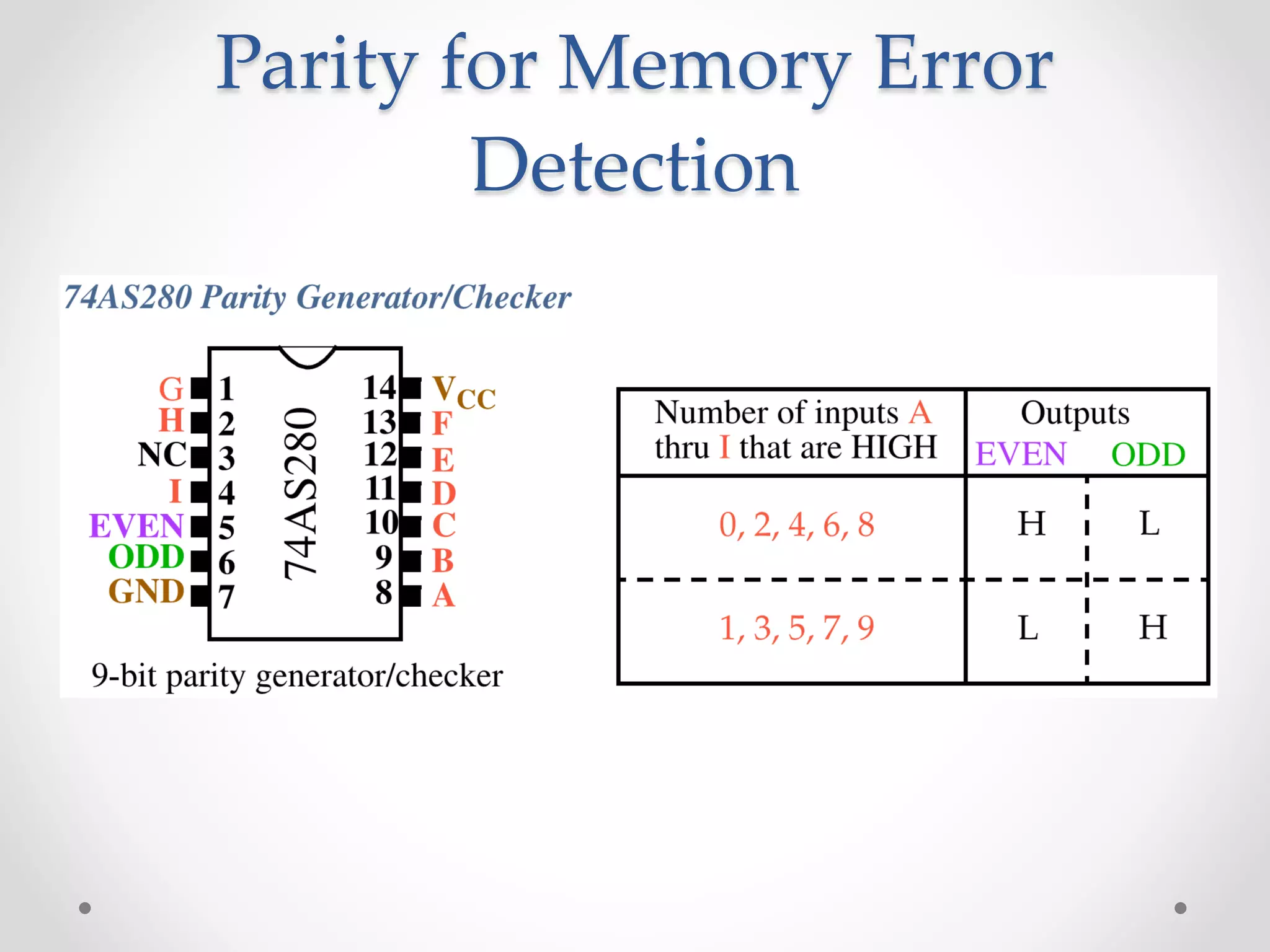

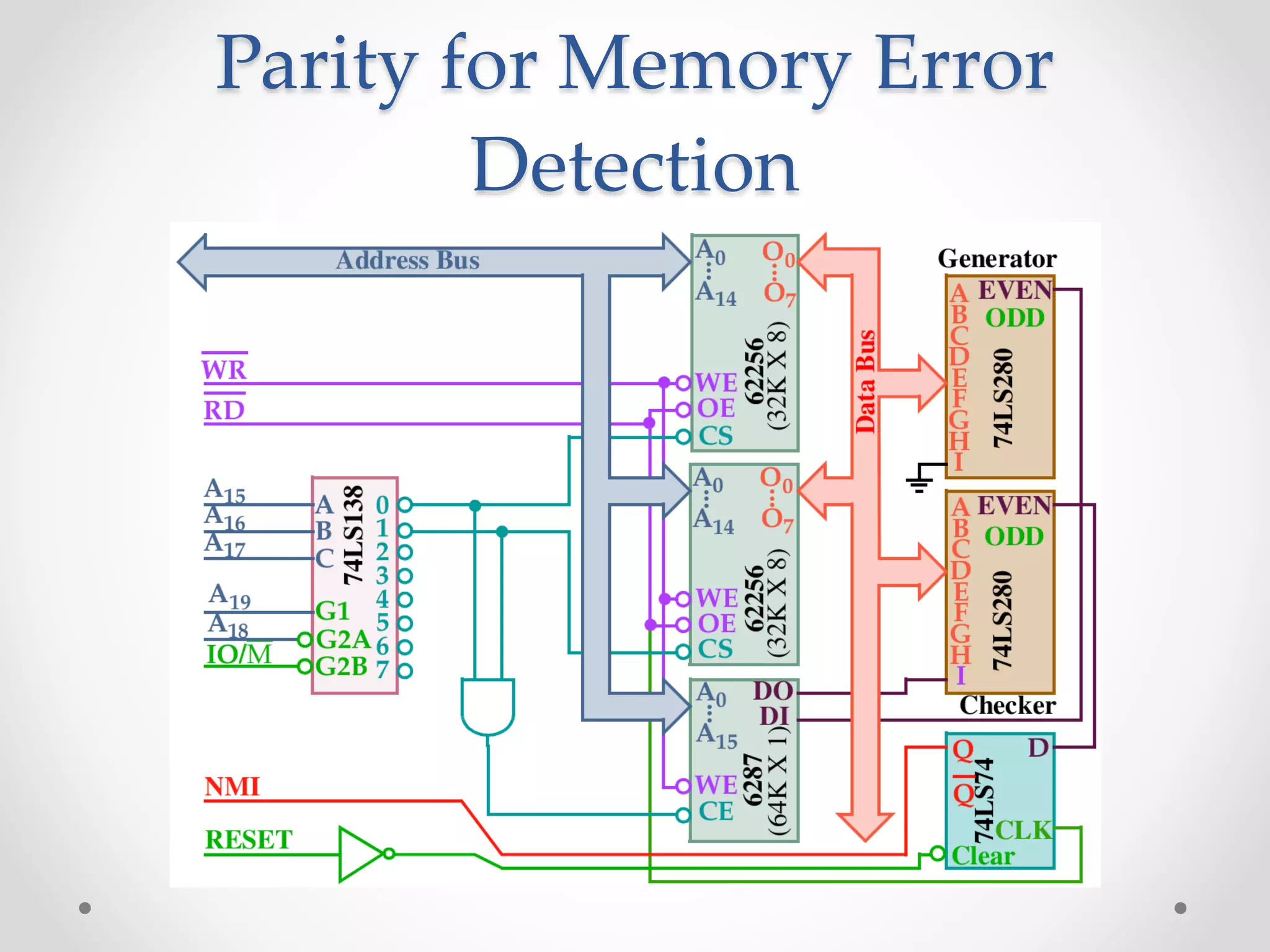

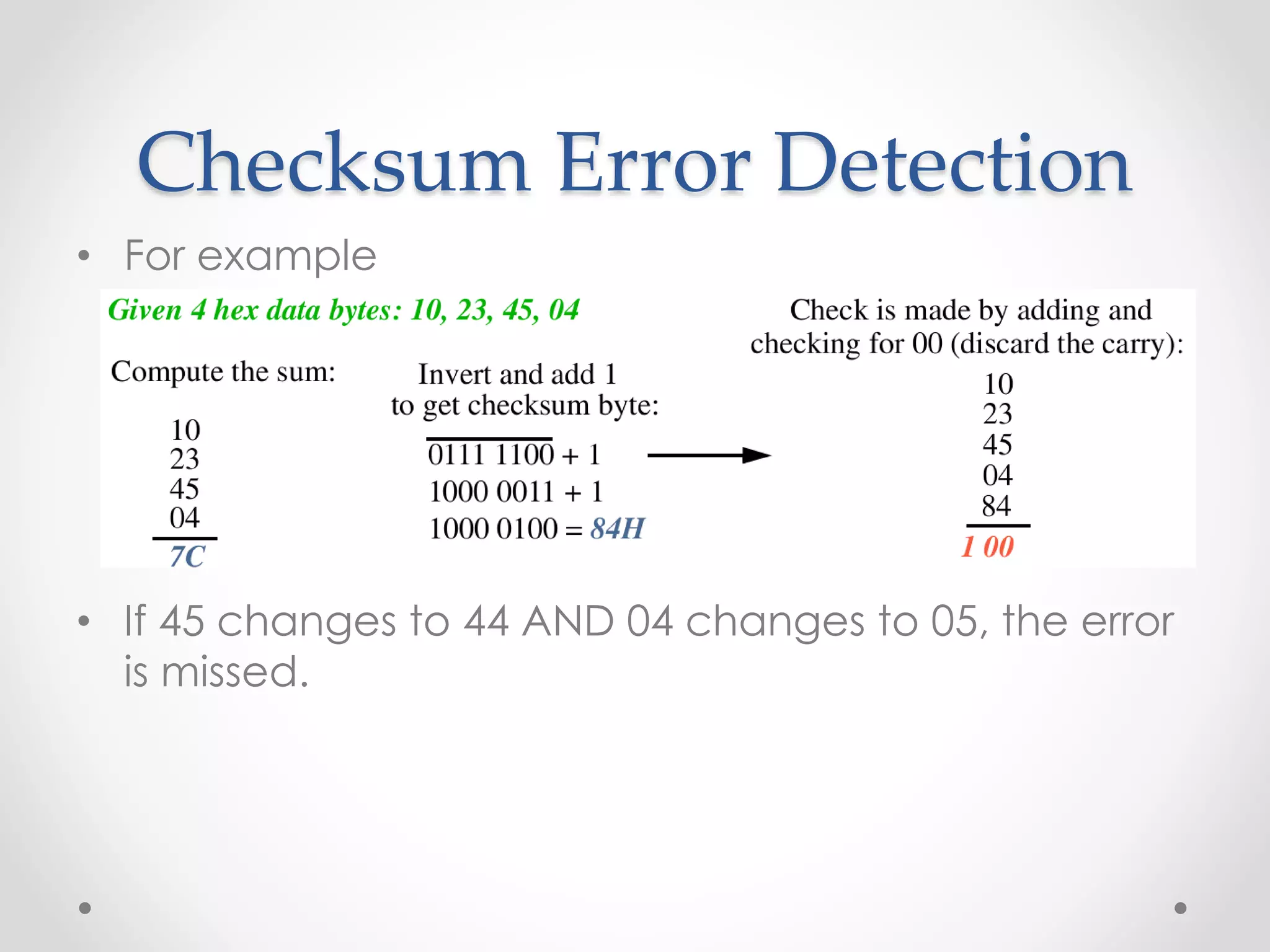

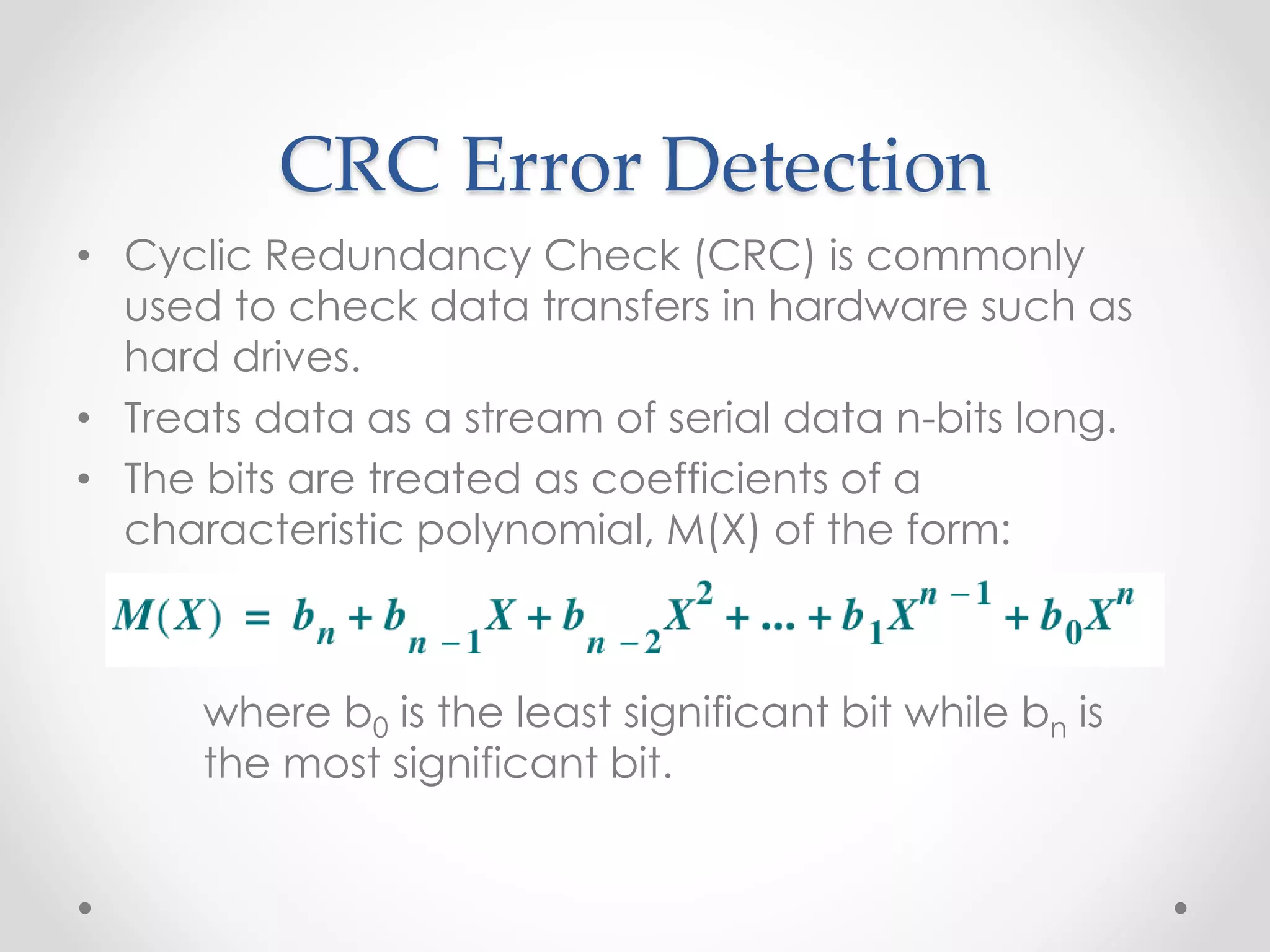

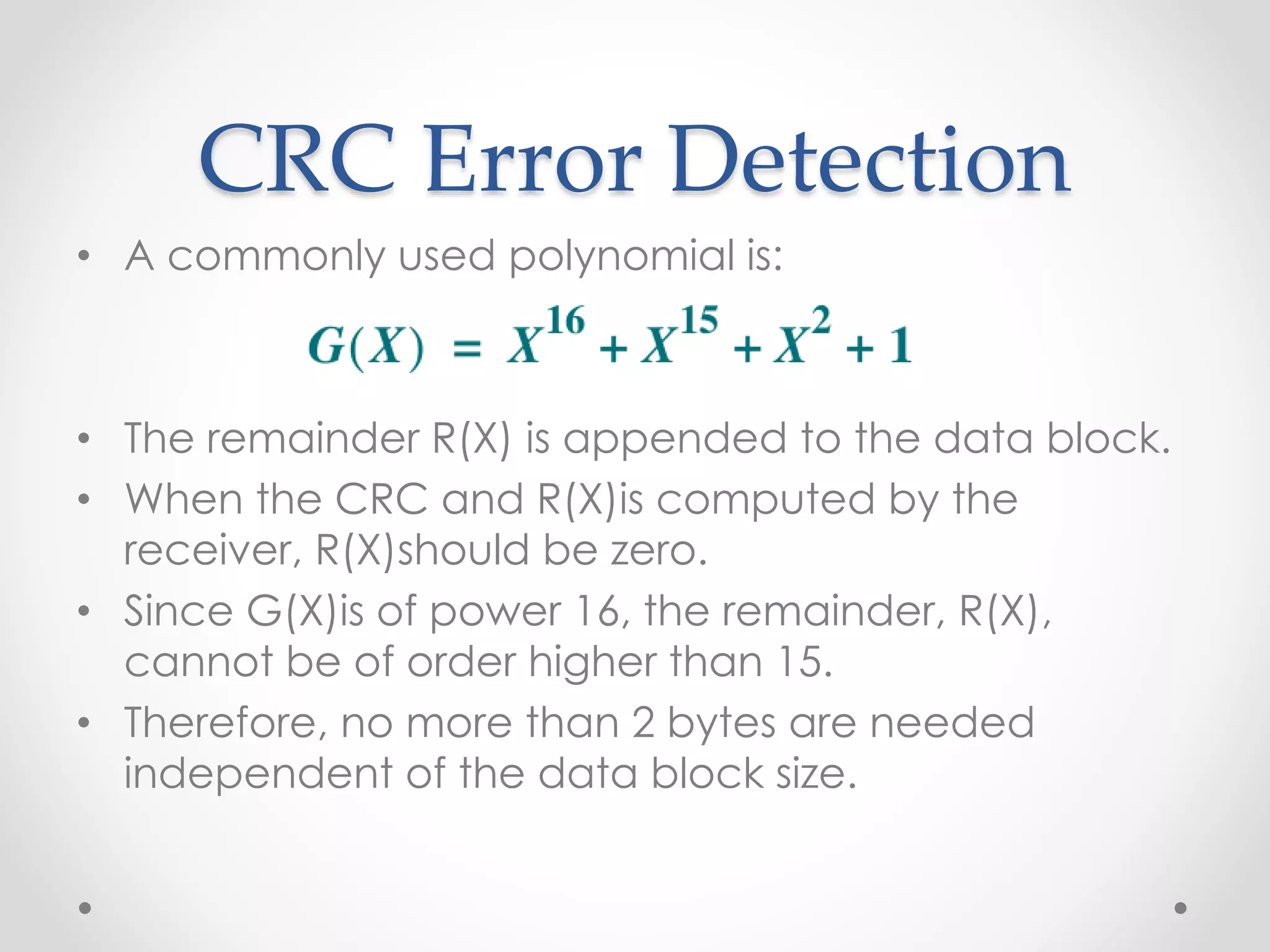

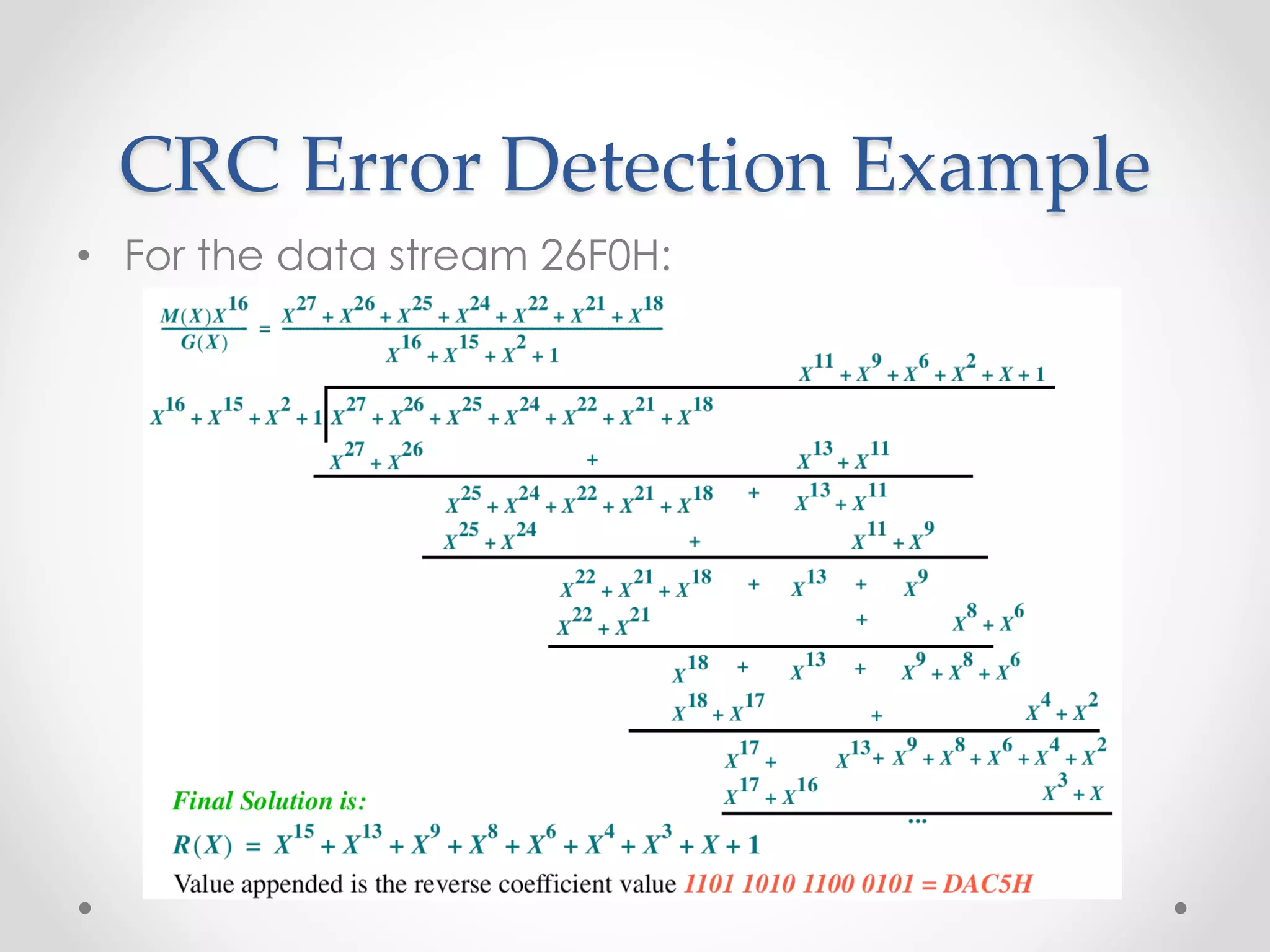

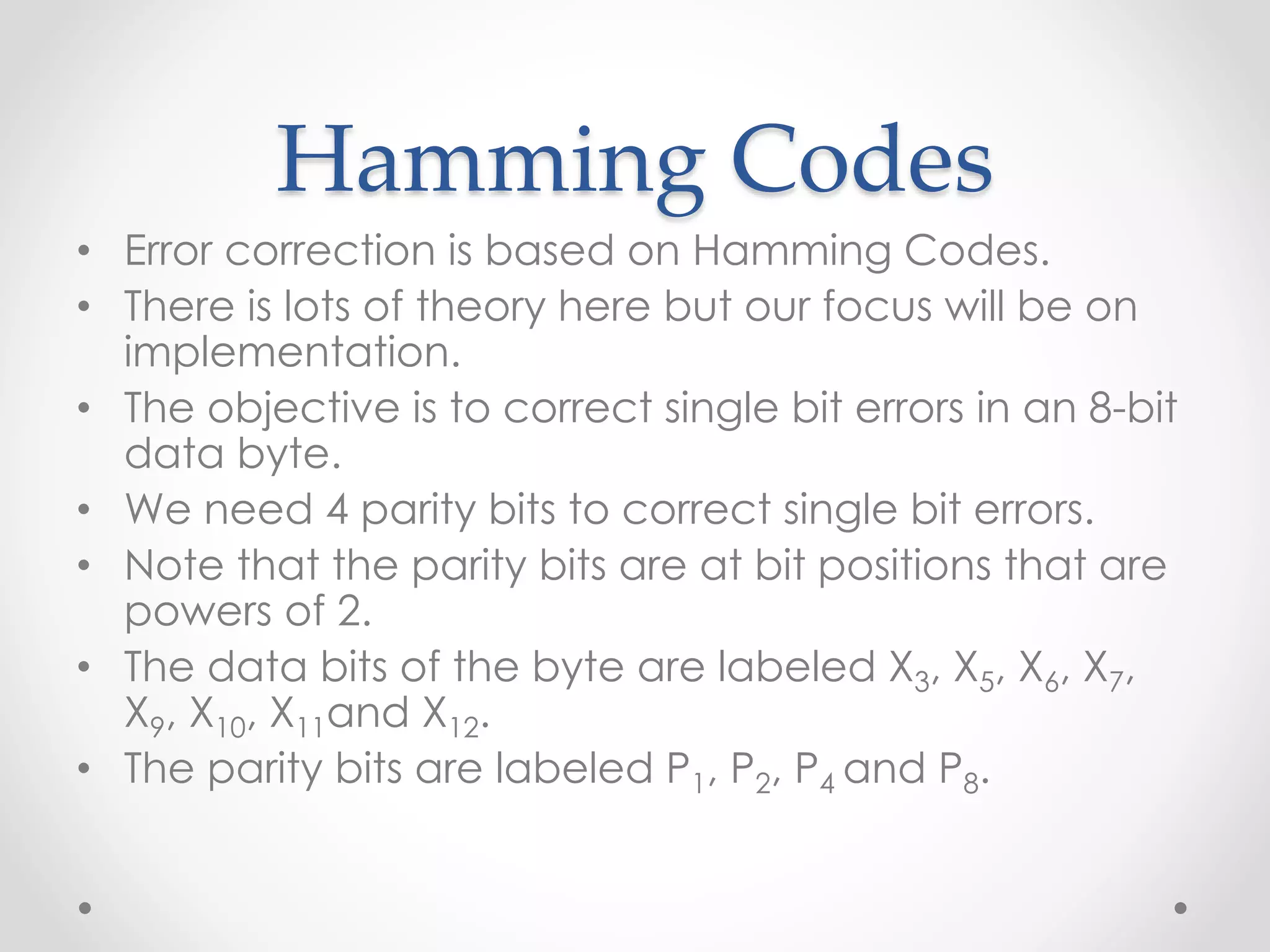

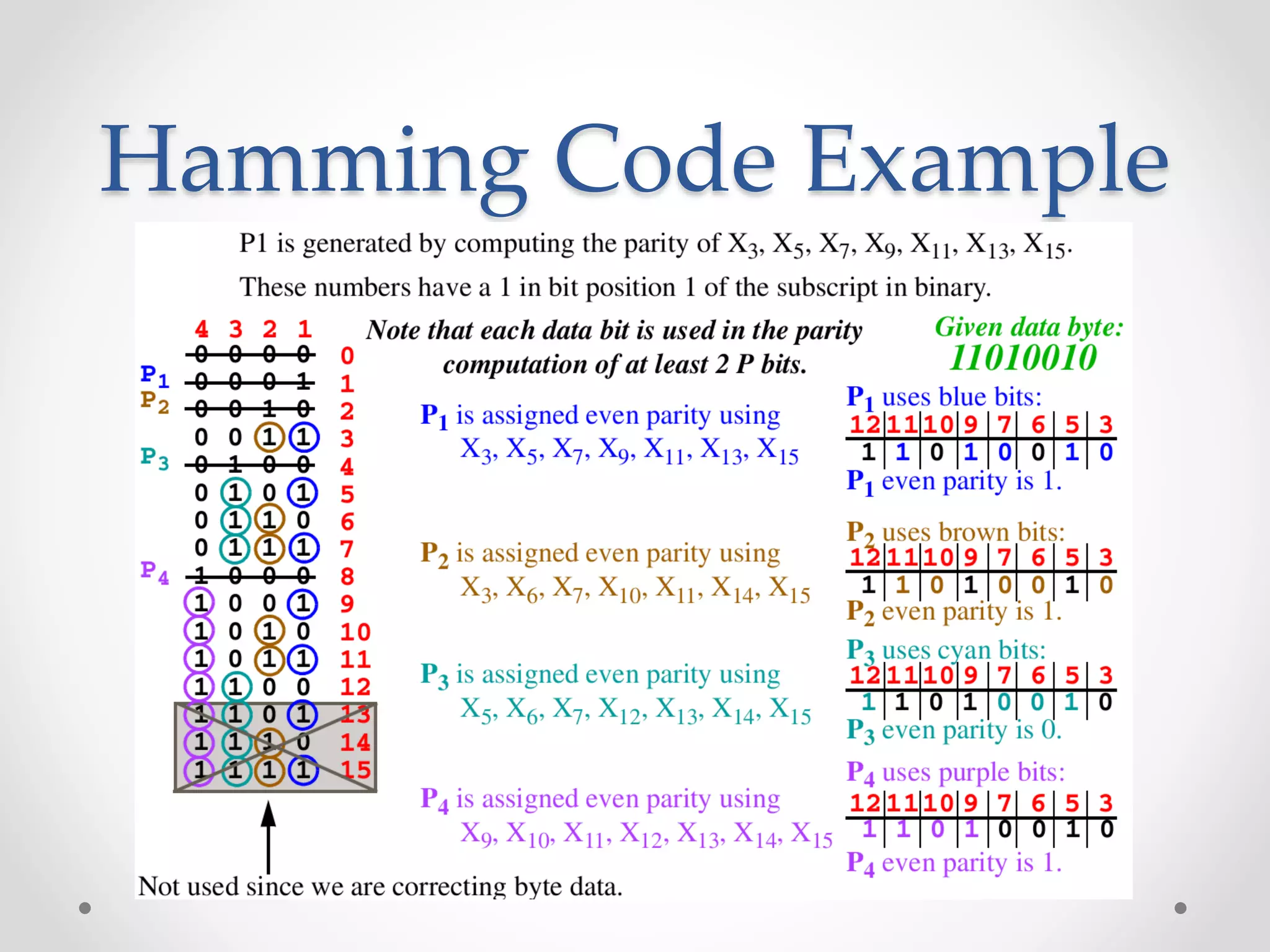

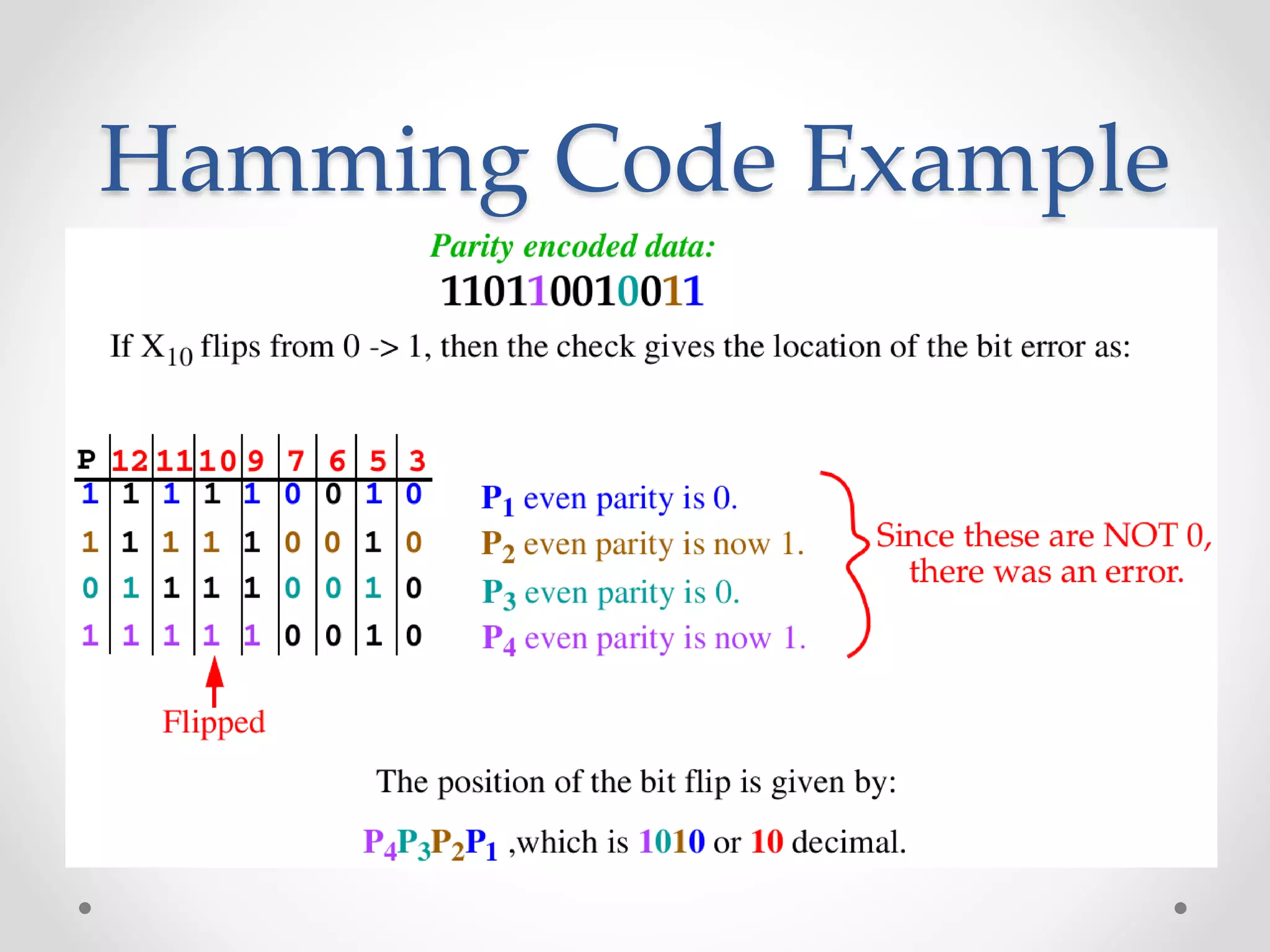

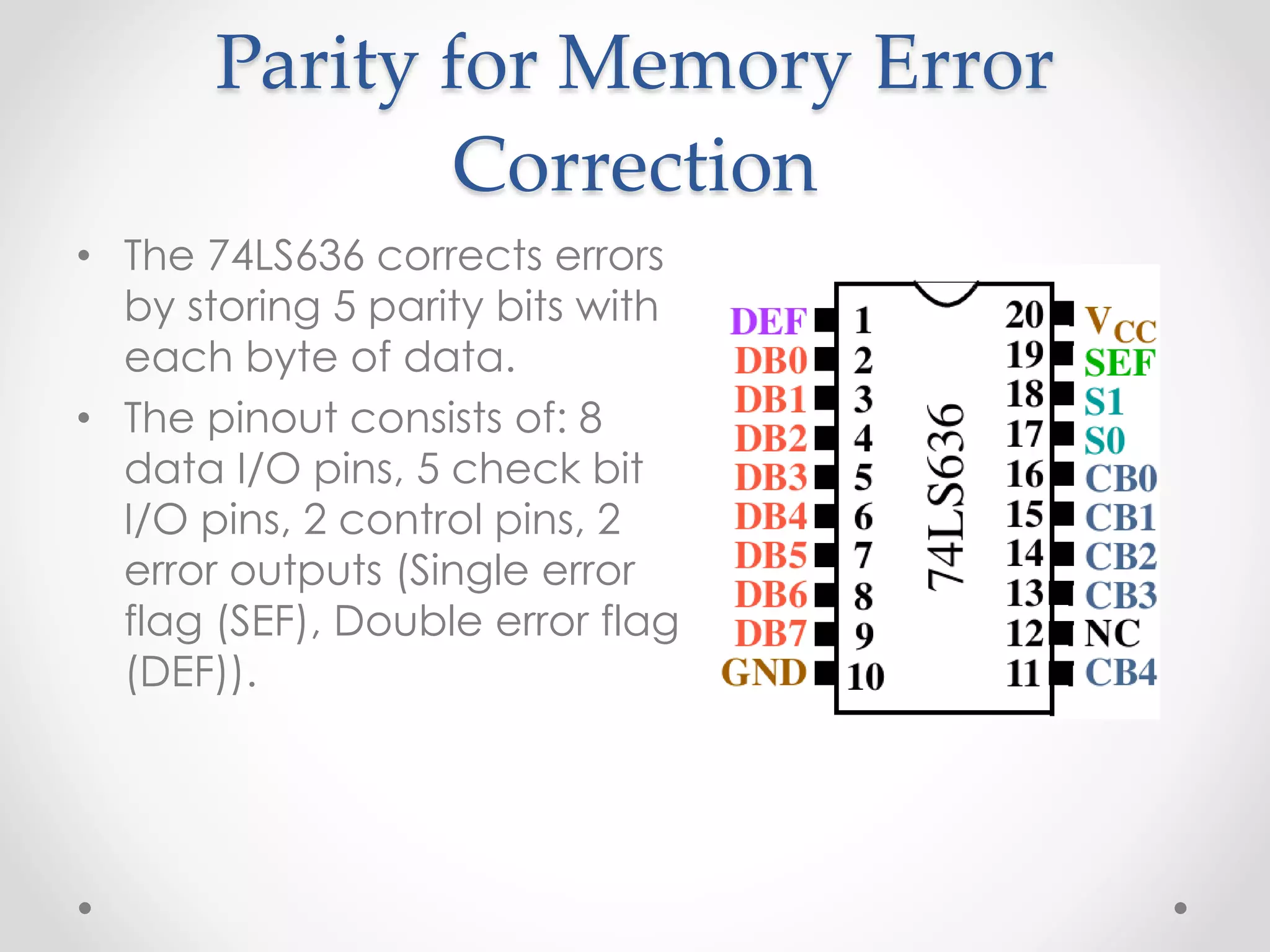

This document discusses different types of memory devices and interfaces. It describes ROM, EEPROM, SRAM, and DRAM memory types. It discusses address decoding and provides examples of memory interfaces for the 8088, 8086, 80386, and Pentium processors. The document also covers error detection techniques like parity checking, checksums, and cyclic redundancy checks (CRC). It provides an example of how Hamming codes can be used for error correction in memory.