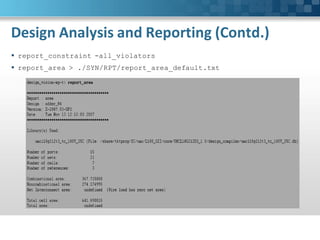

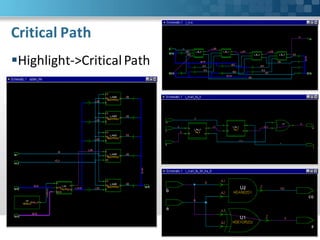

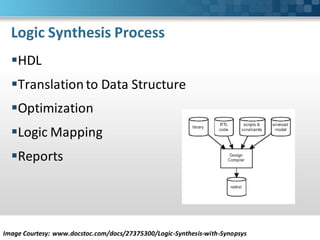

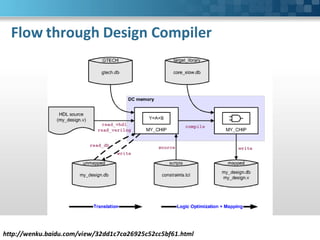

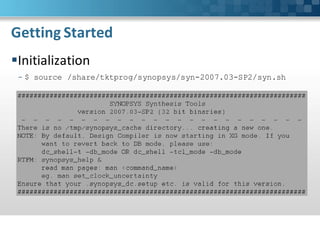

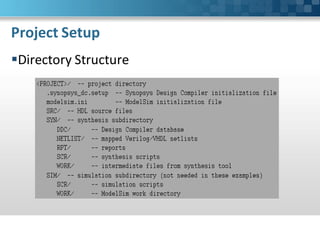

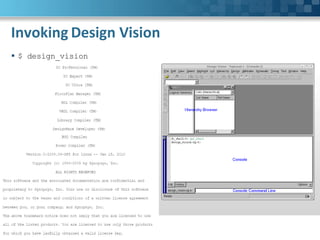

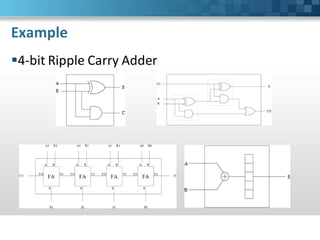

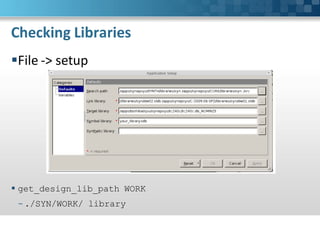

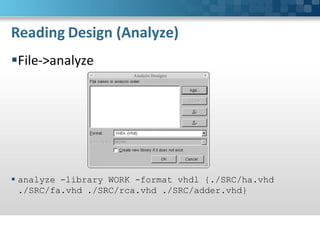

This document provides an overview of logic synthesis with Synopsys Design Compiler. It discusses the ASIC design flow, logic synthesis process, the Design Compiler tool, and the steps to use Design Compiler including project setup, reading the design, setting constraints, optimizing the design, and analyzing results. The goals of logic synthesis are to convert HDL to an optimized gate-level design given a library and constraints. Design Compiler is used to perform logic synthesis and optimization for area, speed or power.

Human: Thank you, that is a concise 3 sentence summary that captures the key aspects of the document.

![Setting Constraints (Contd.)

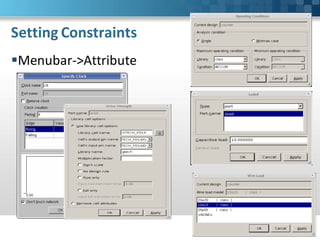

create_clock -name "clk" -period 4 -waveform {0 2} {clk}

set_clock_uncertainty 0.1 clk

set_clock_latency 0.2 clk

set_clock_transition 0.1 clk

set_dont_touch_network clk

set_driving_cell -library umcl18g212t3_tc_180V_25C -lib_cell

HDDFFPB1 -pin Q [get_ports a]

set_driving_cell -library umcl18g212t3_tc_180V_25C -lib_cell HDINVD1

-pin Z [get_ports b] set_load [load_of

umcl18g212t3_tc_180V_25C/HDDFFPB1/D] [get_ports s]

set_input_delay 0.67 [get_ports b] -clock clk

set_output_delay 0.5 [get_ports s] -clock clk

set_max_area 1000](https://image.slidesharecdn.com/logicsynthesiswithsynopsysdesigncompiler-120619134032-phpapp02/85/Logic-synthesis-with-synopsys-design-compiler-25-320.jpg)