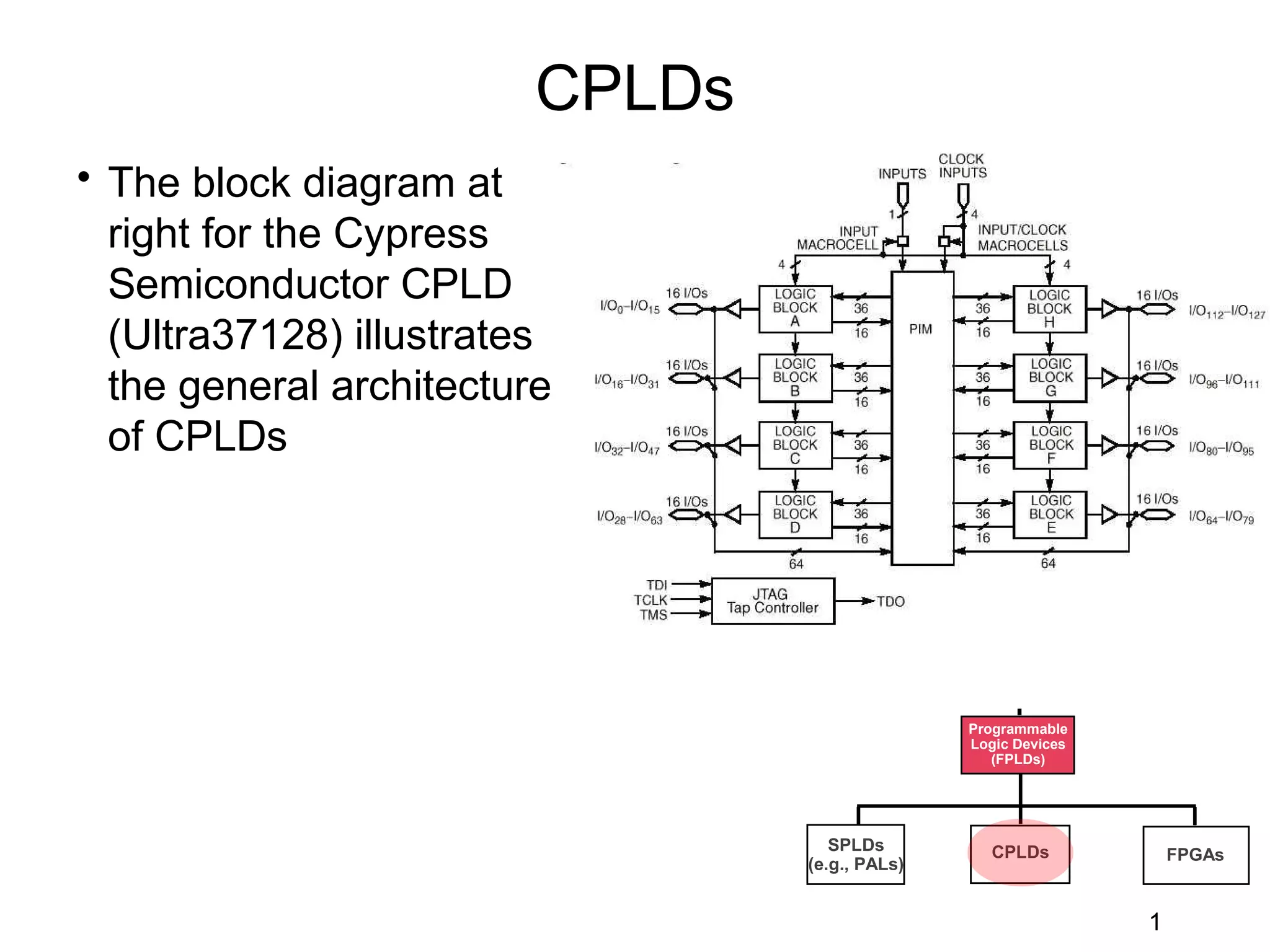

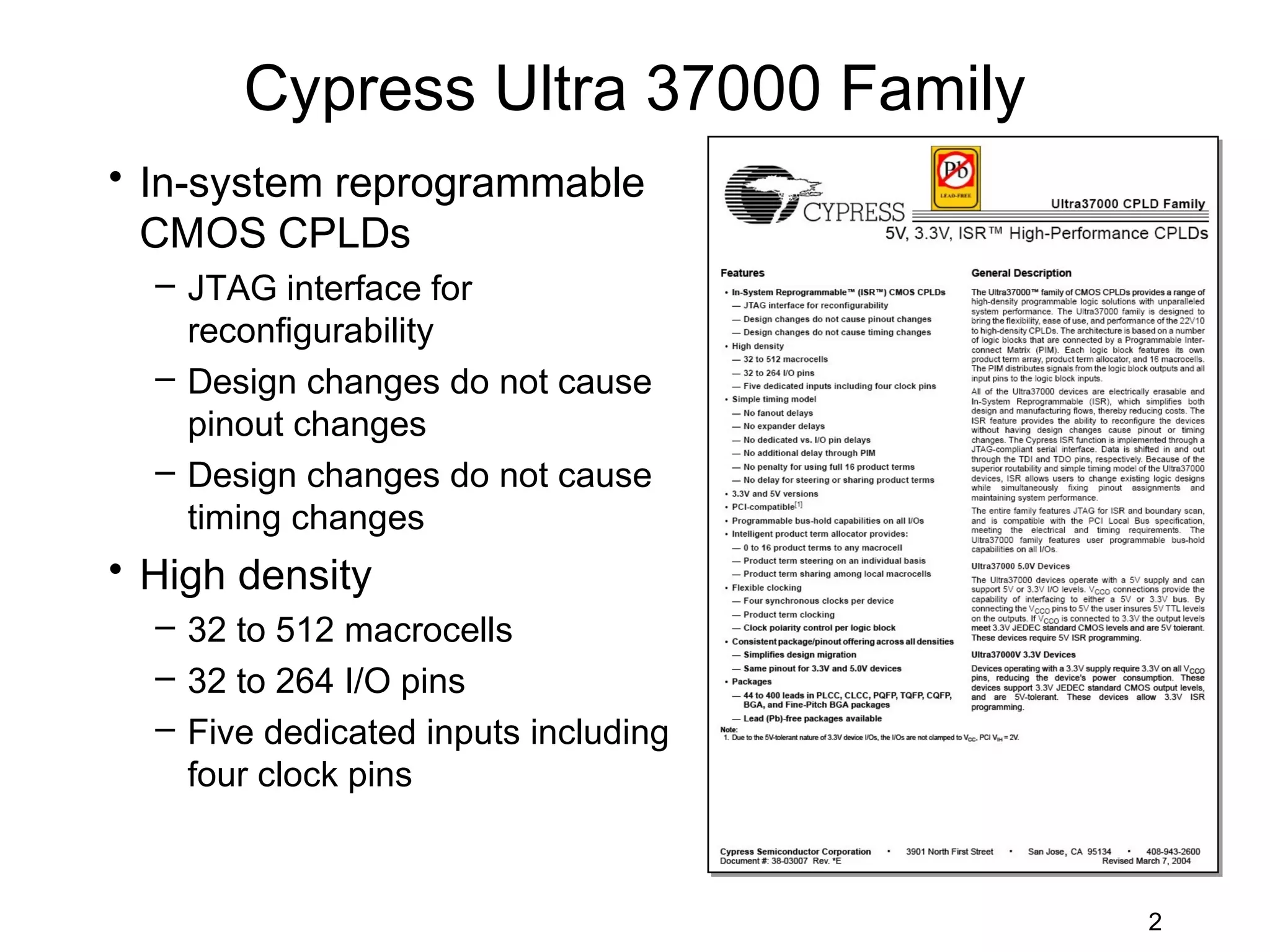

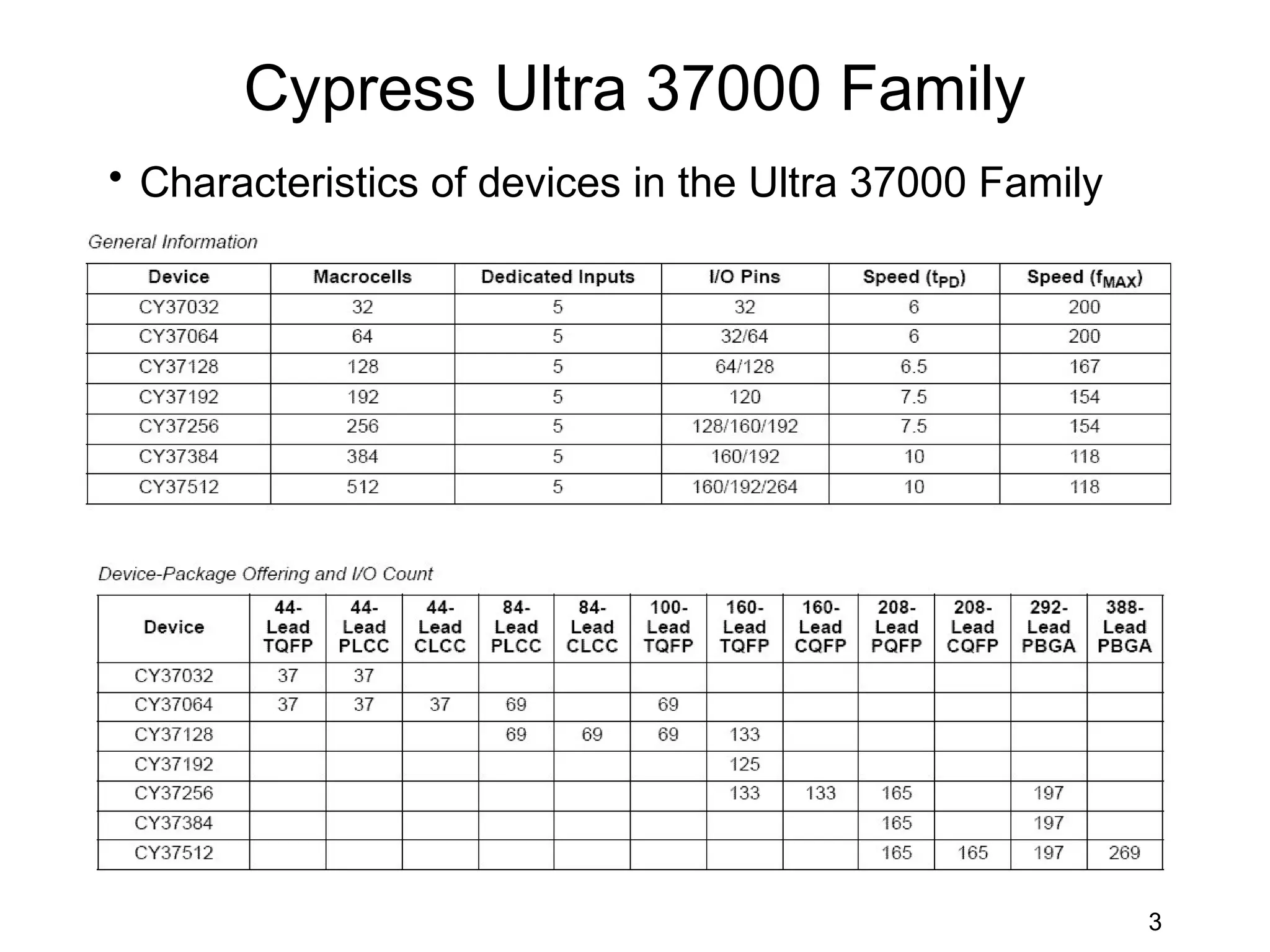

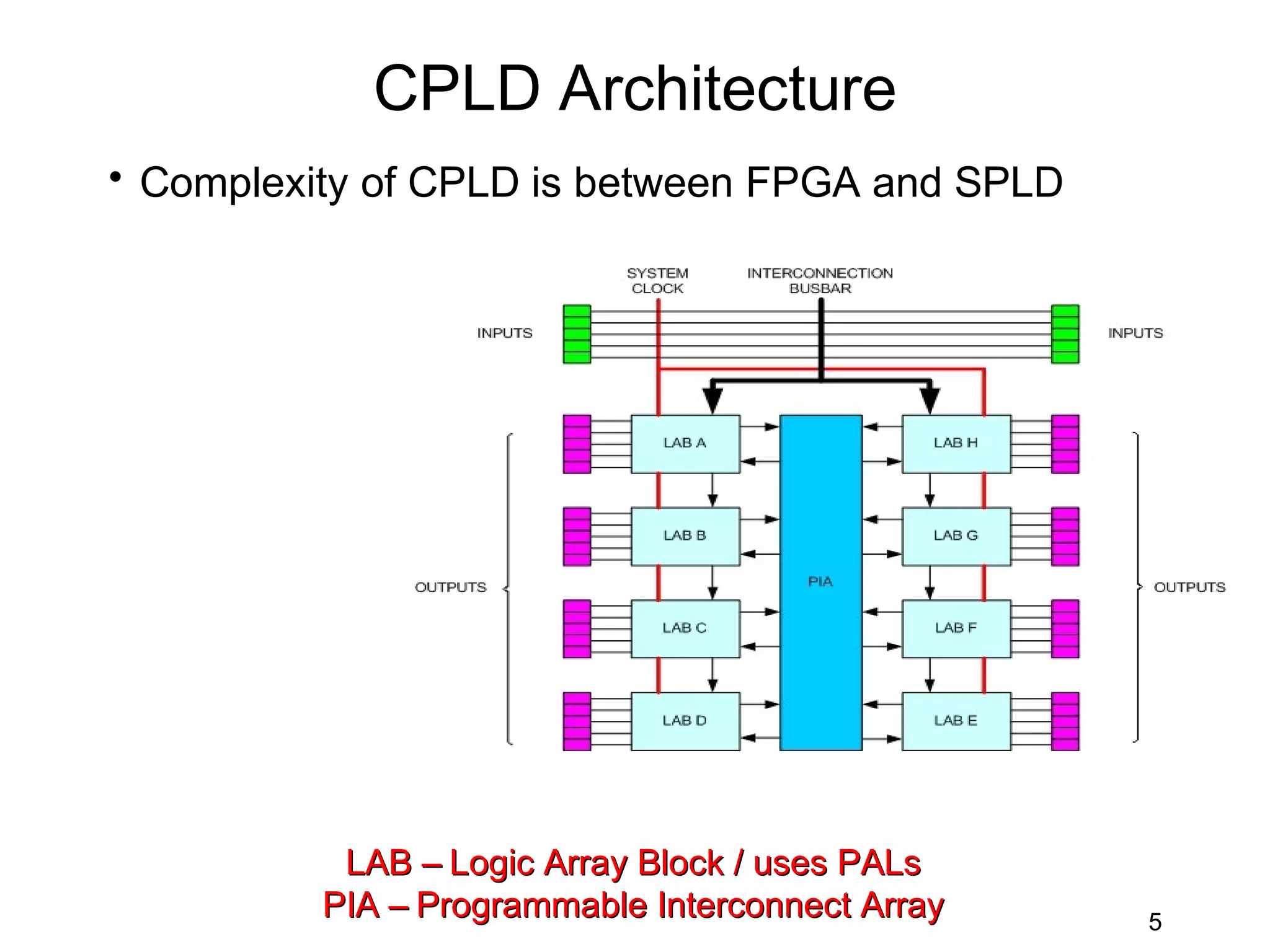

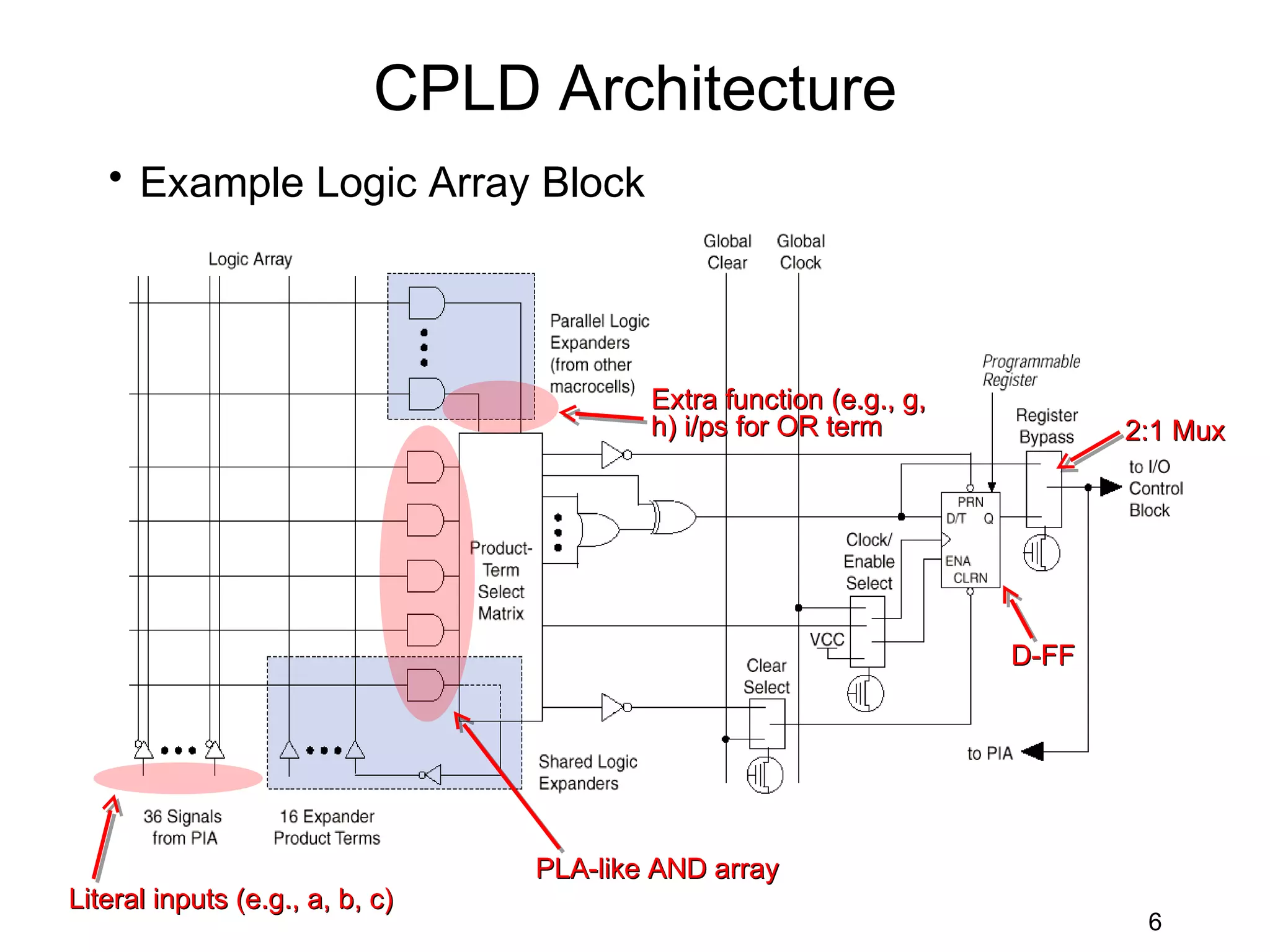

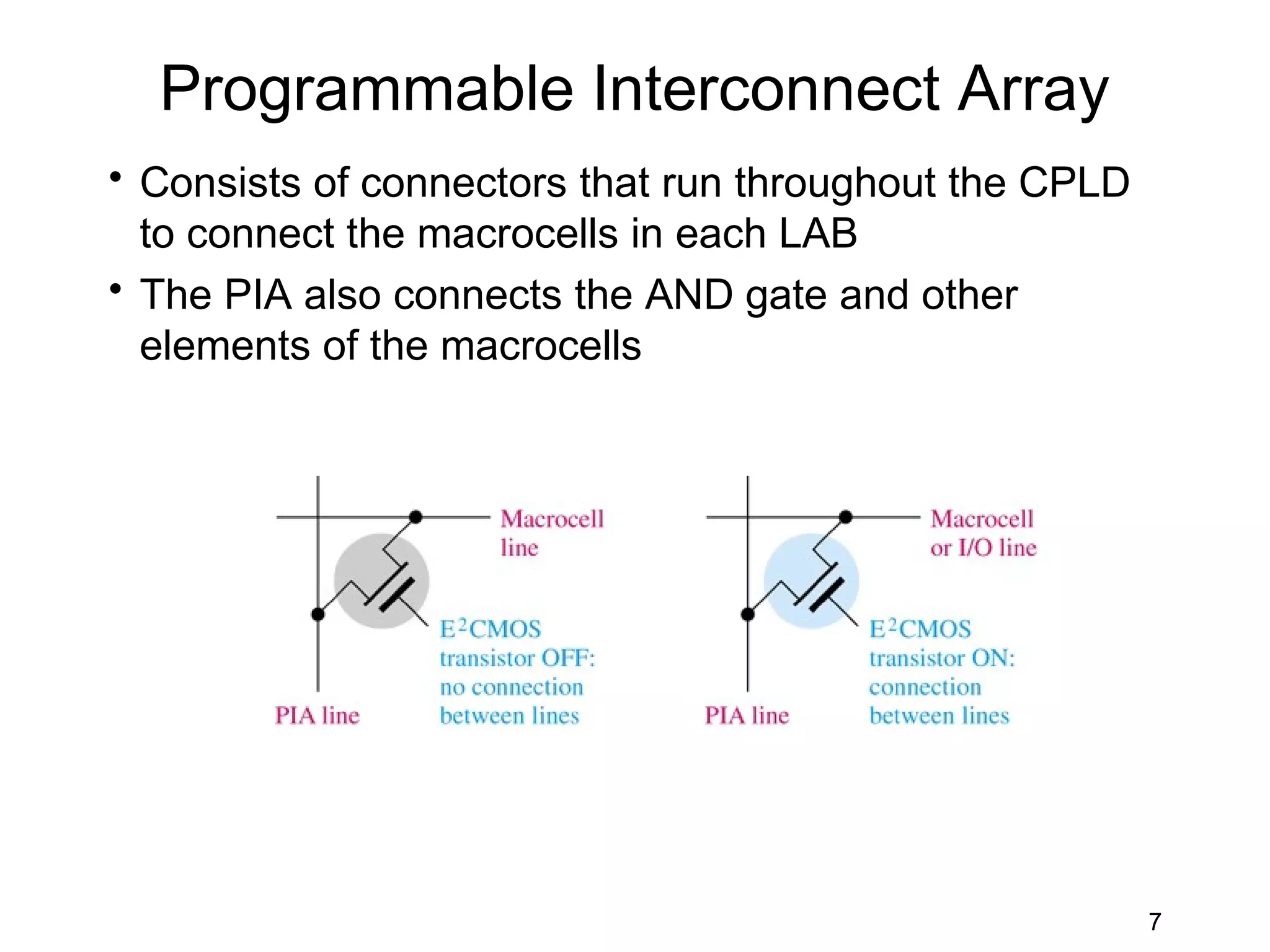

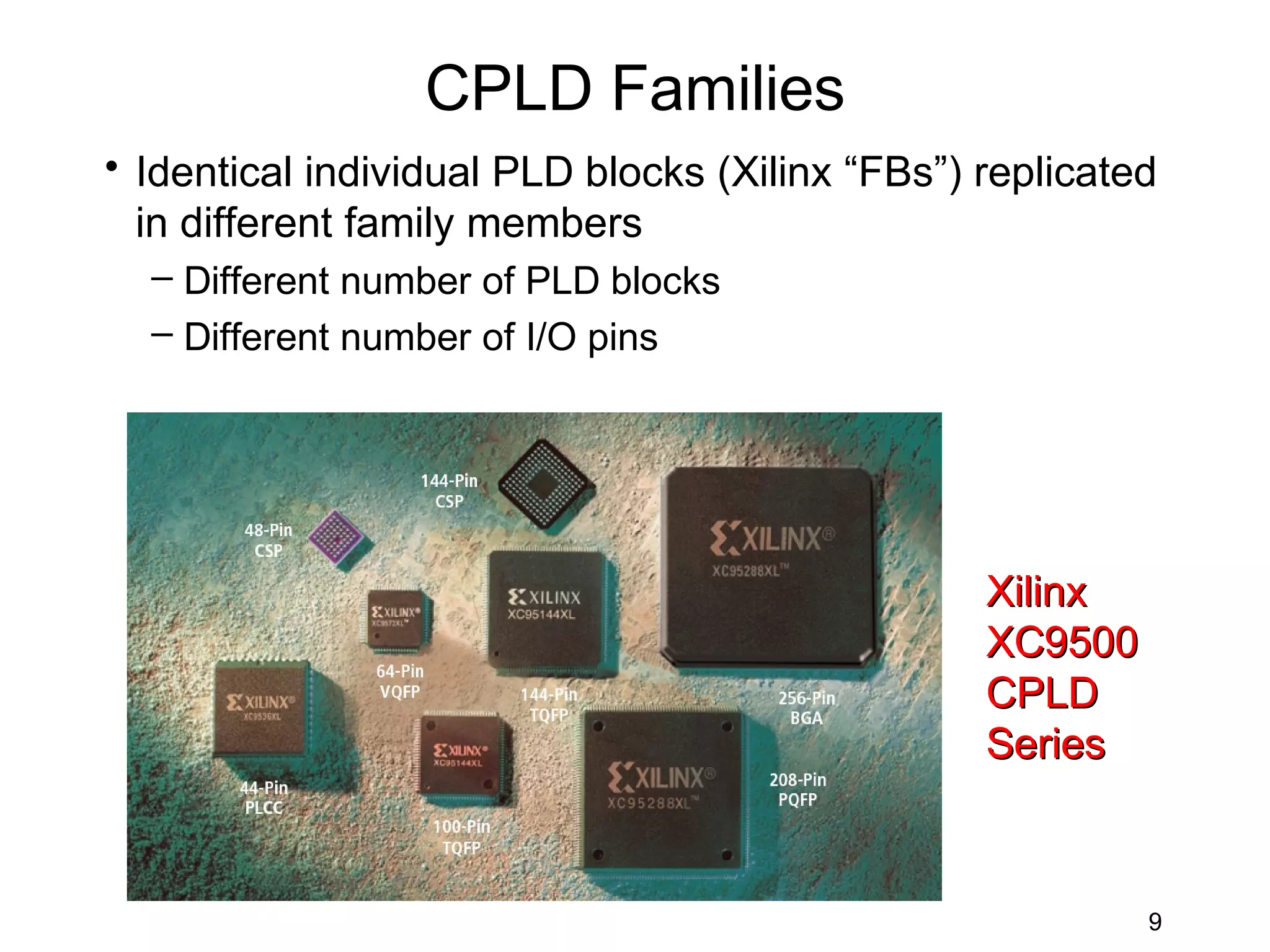

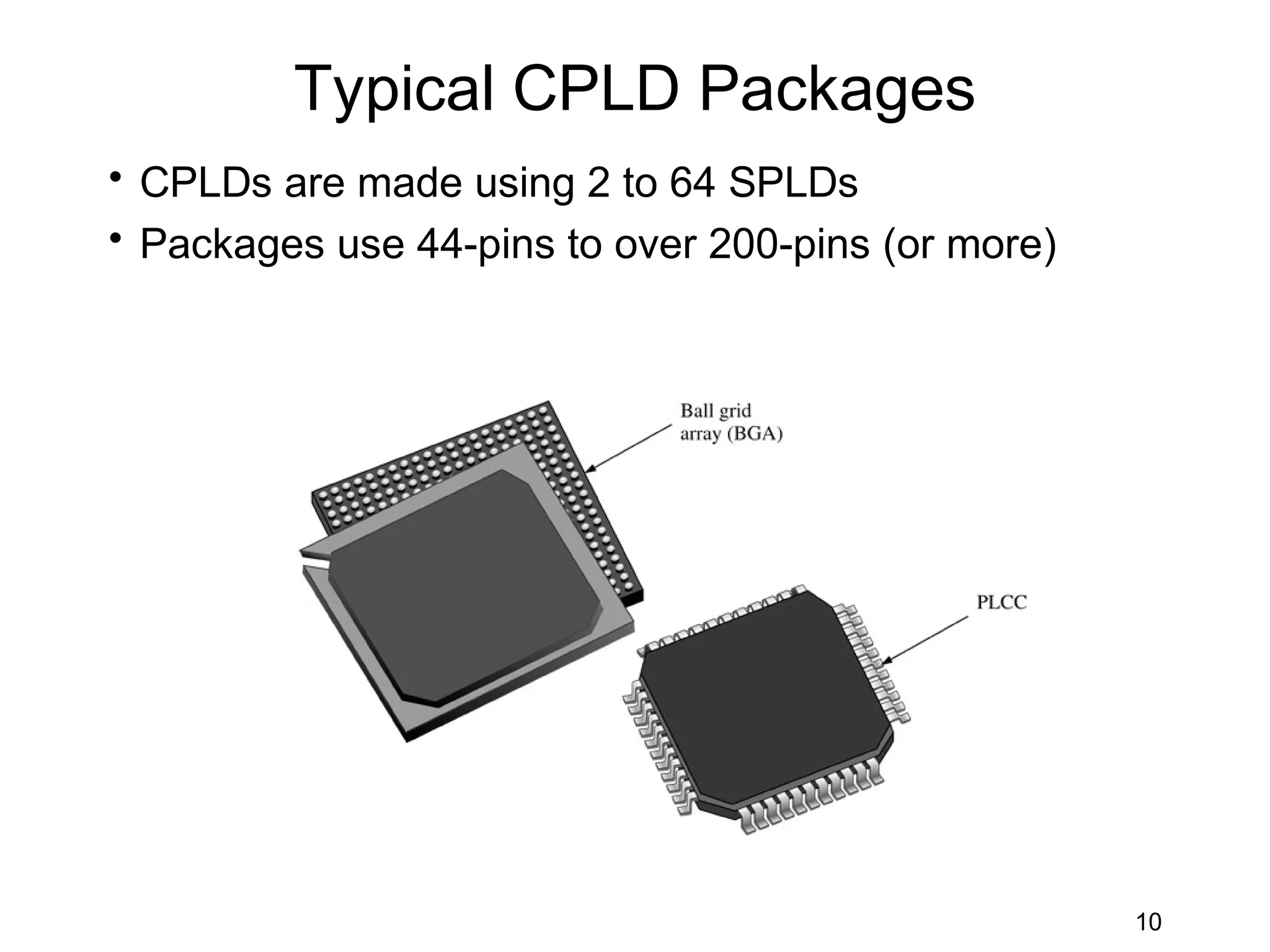

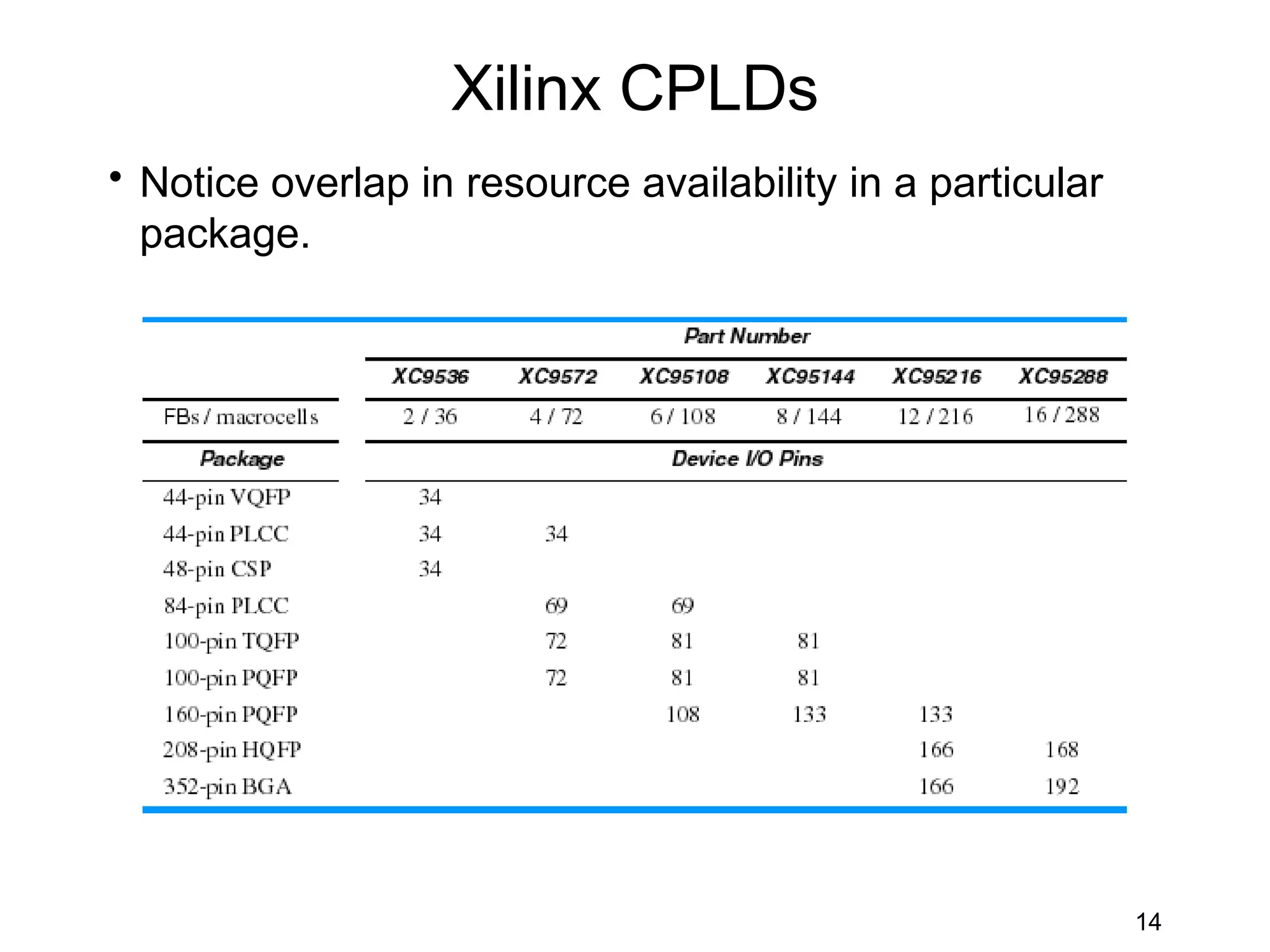

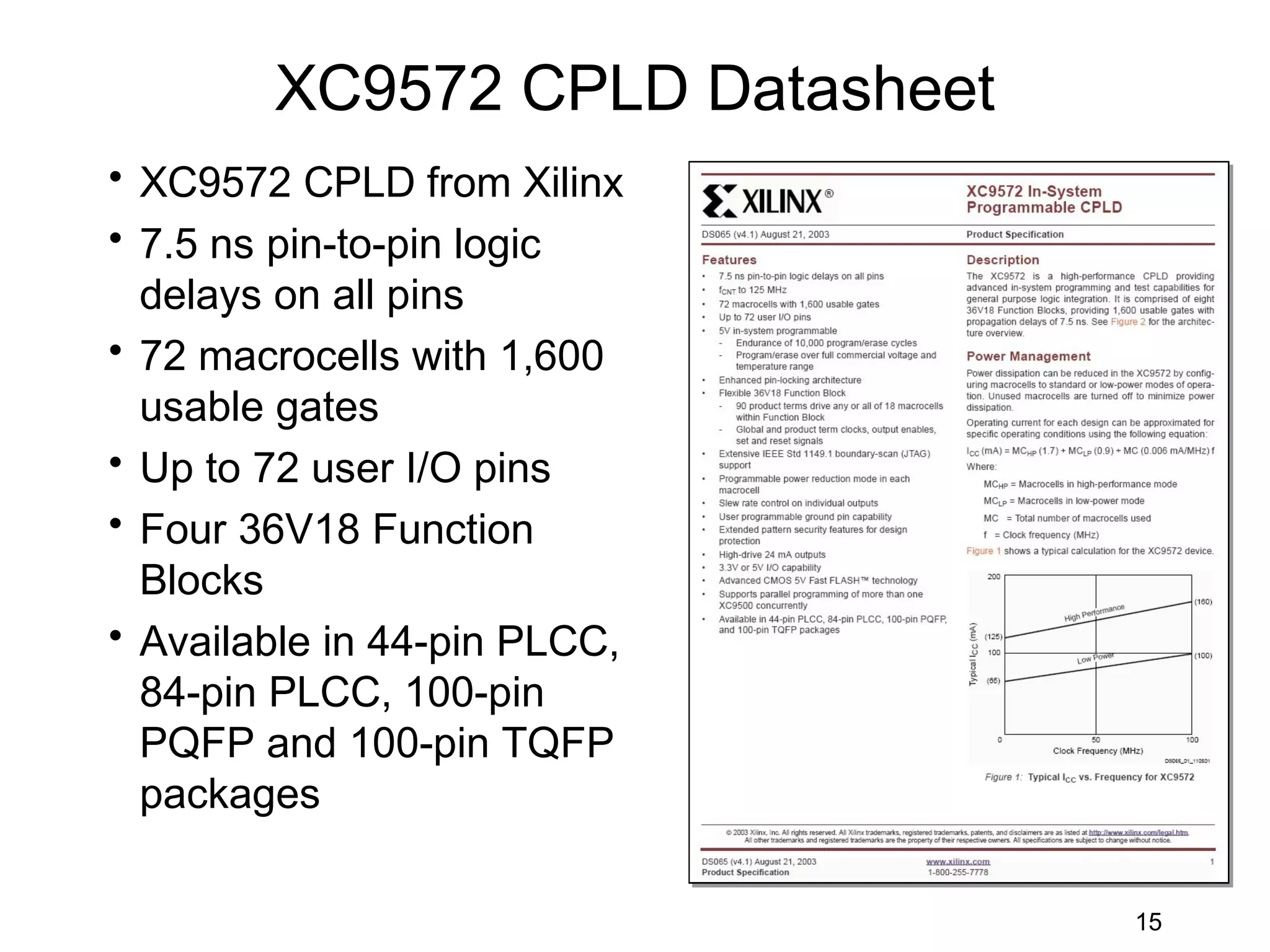

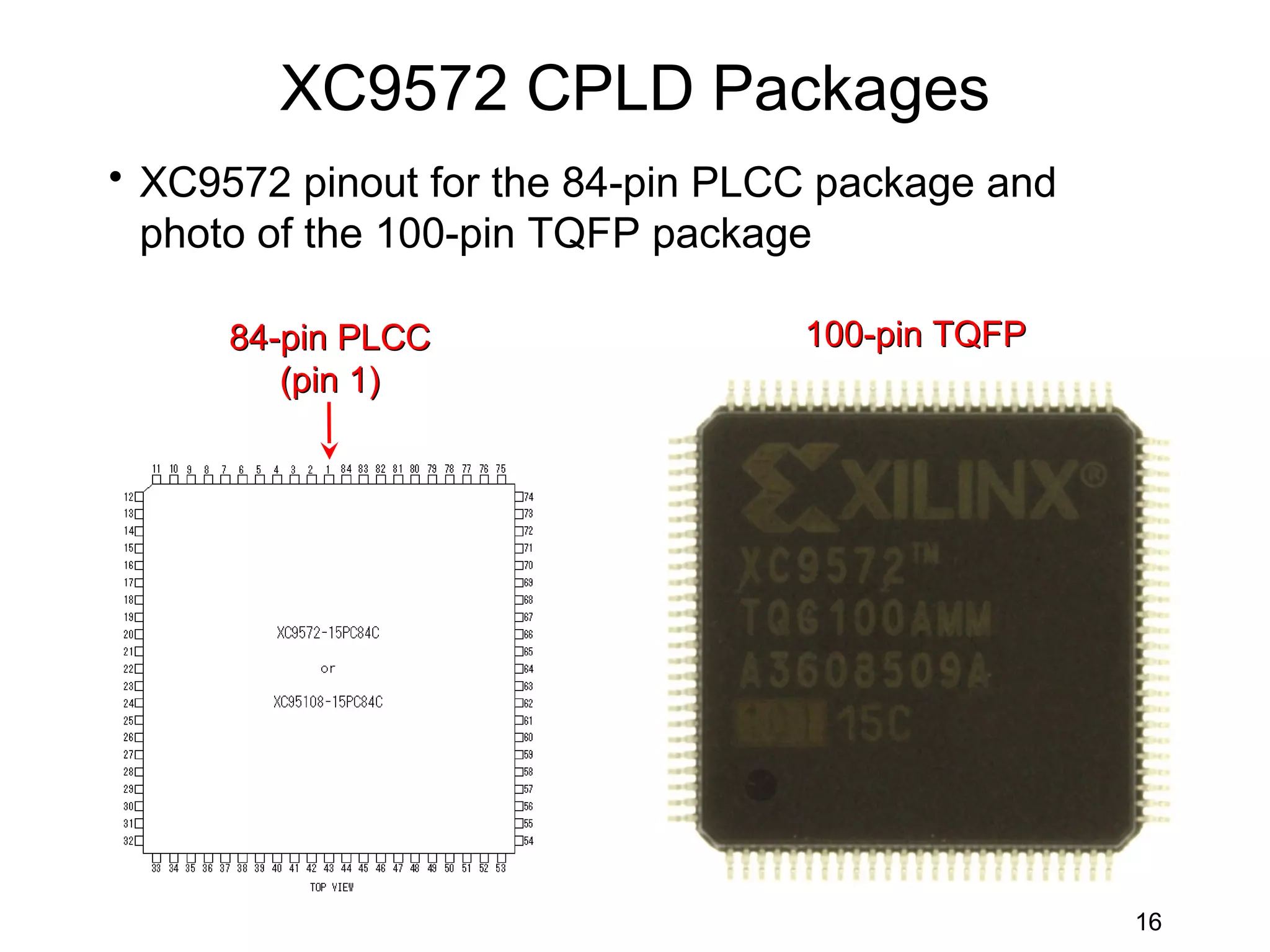

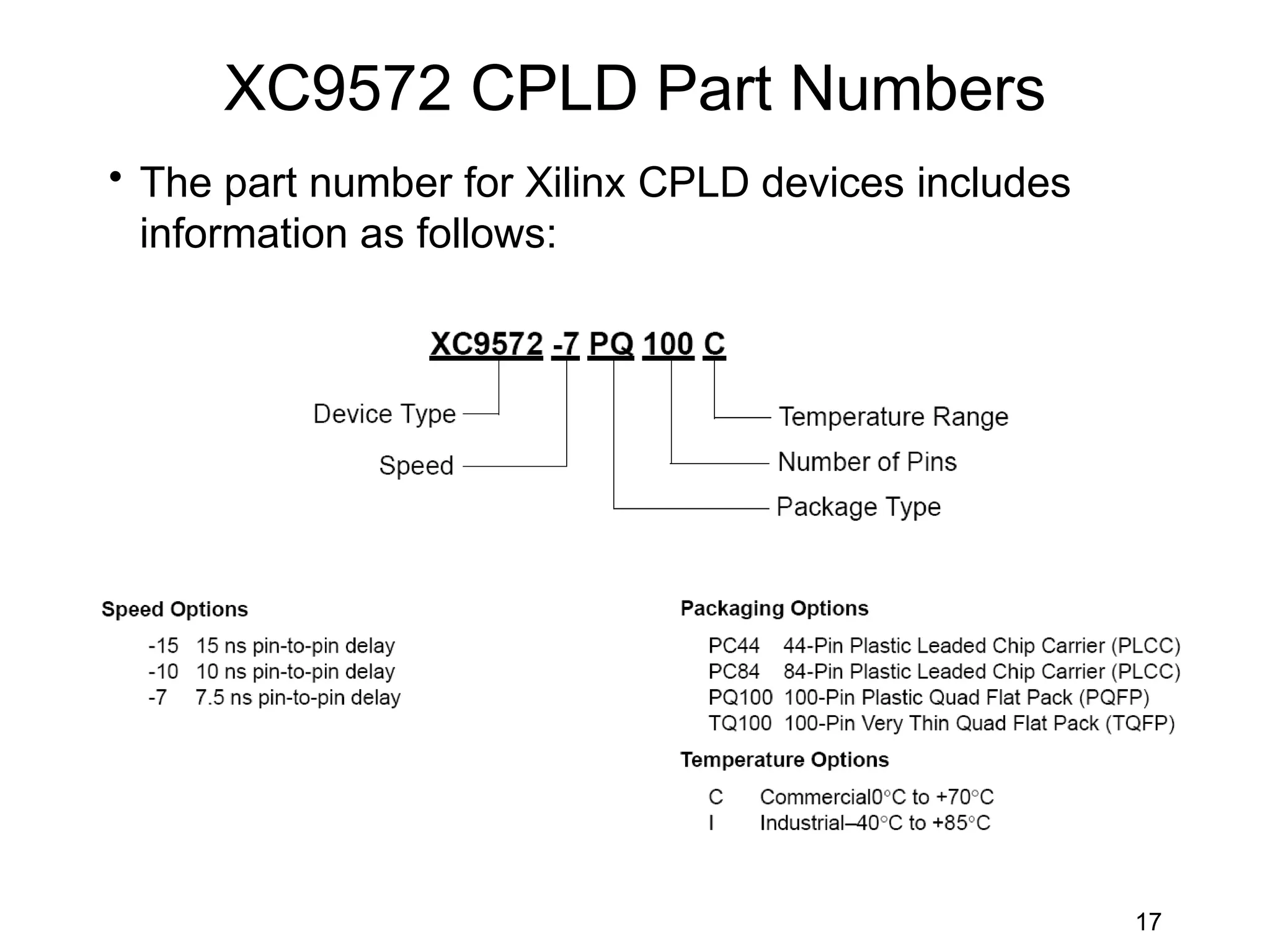

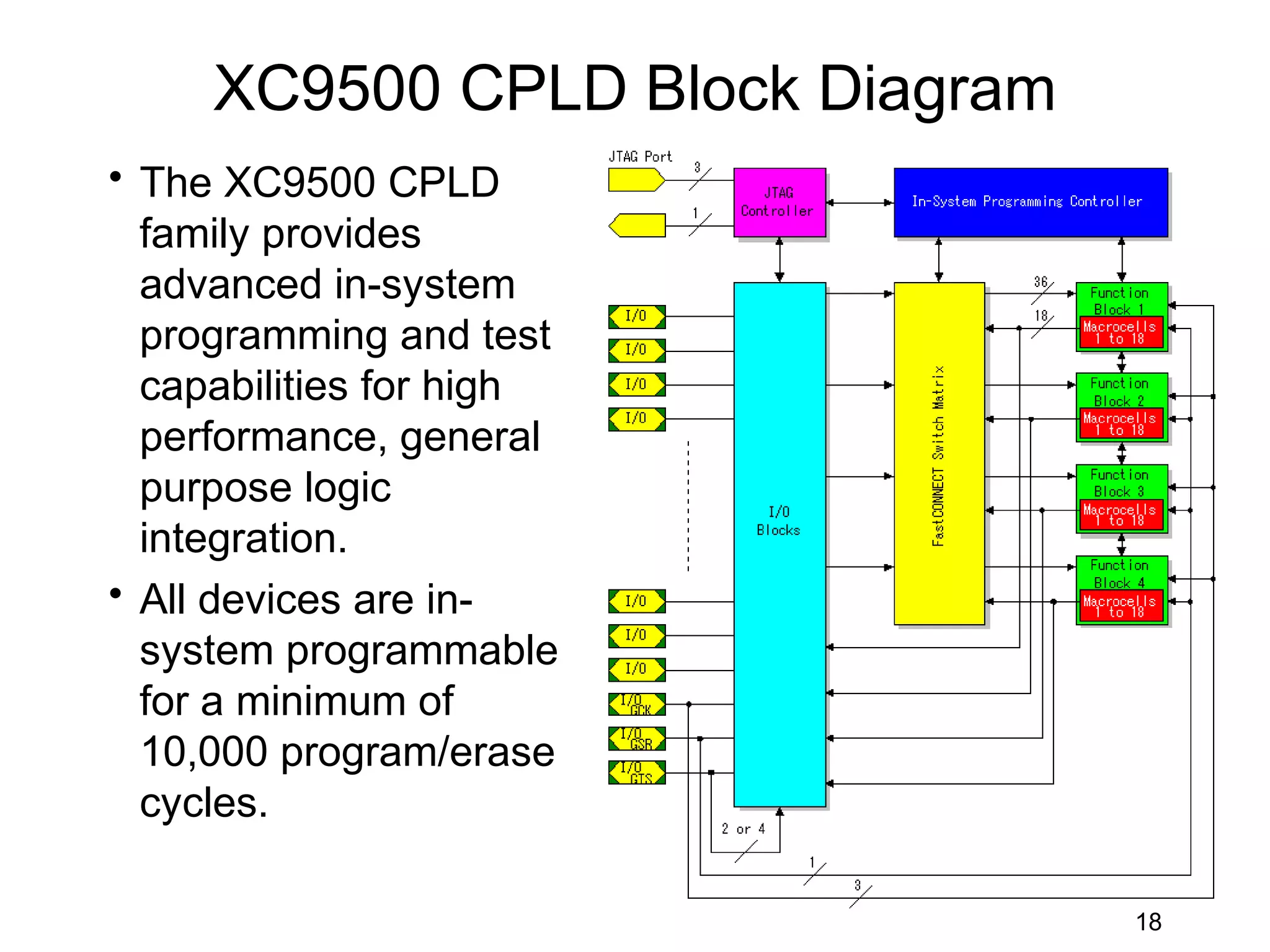

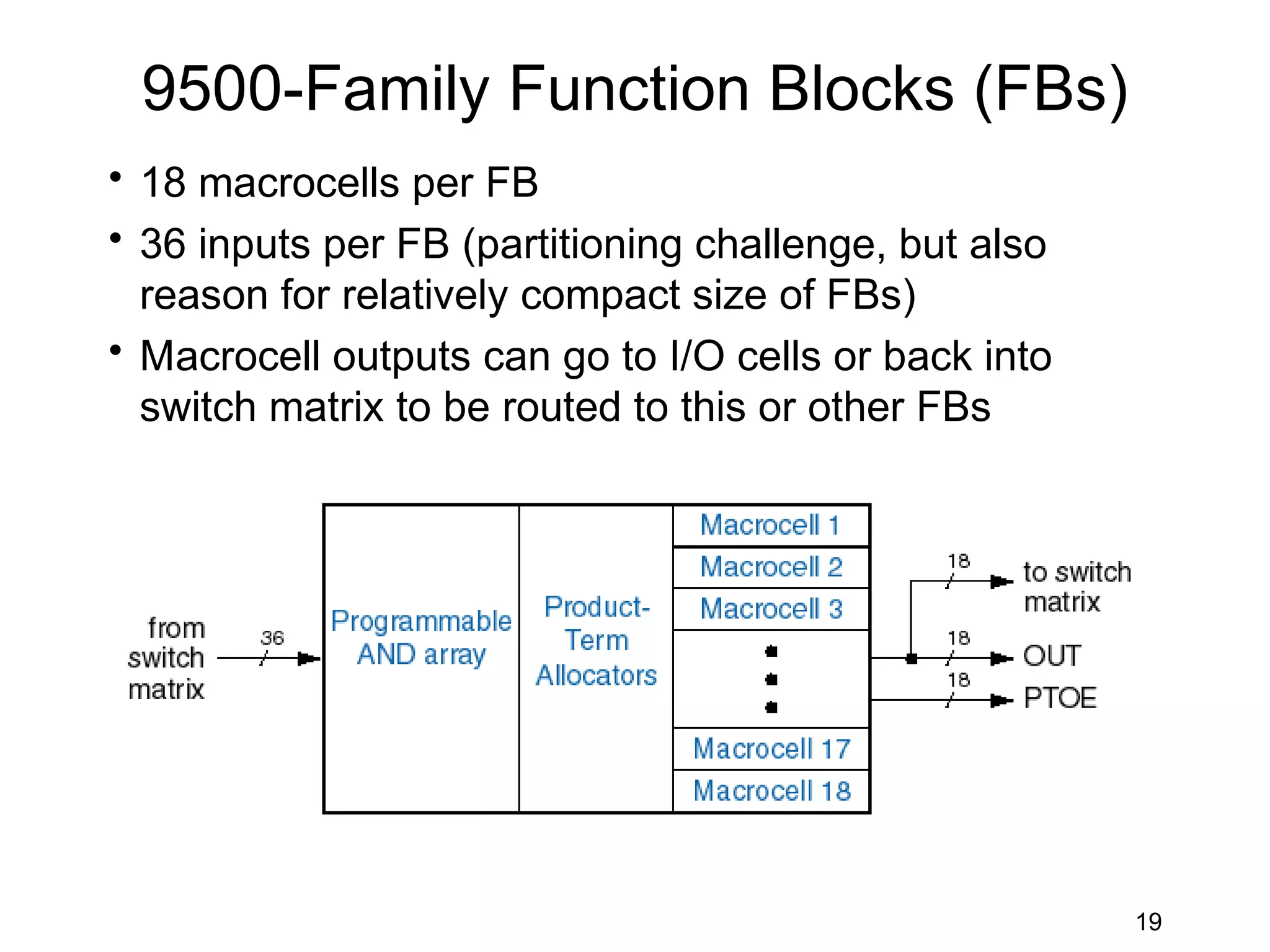

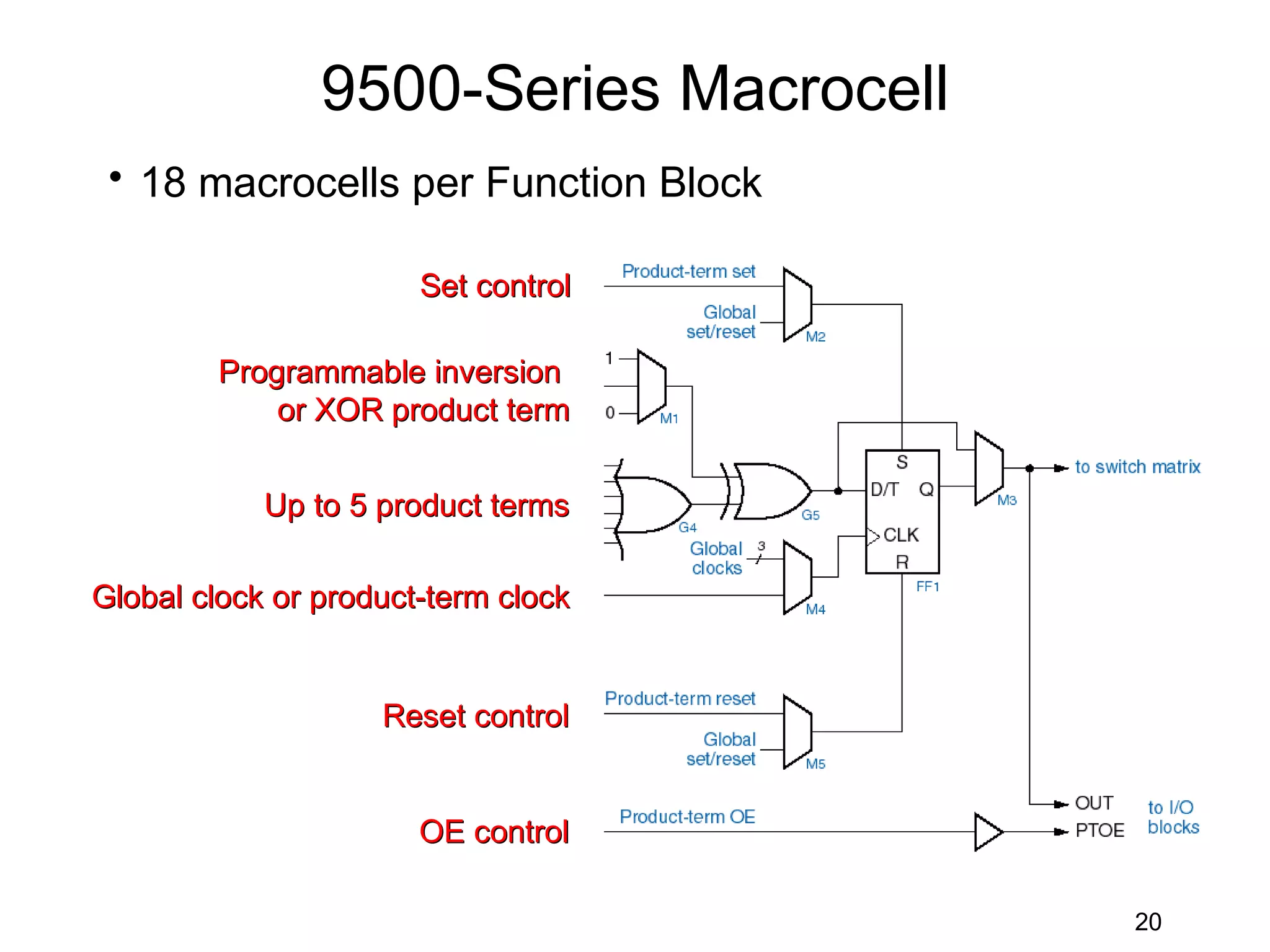

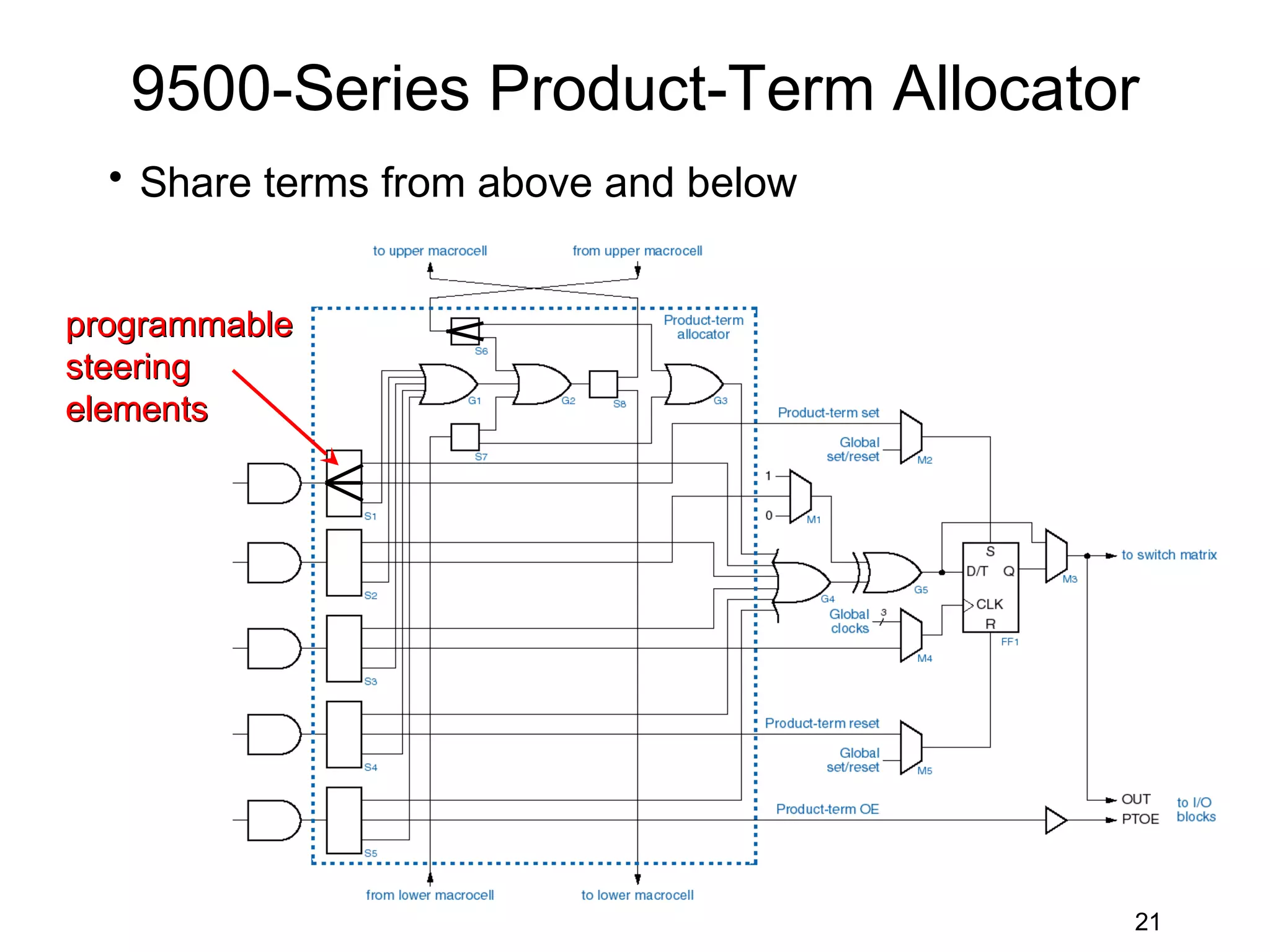

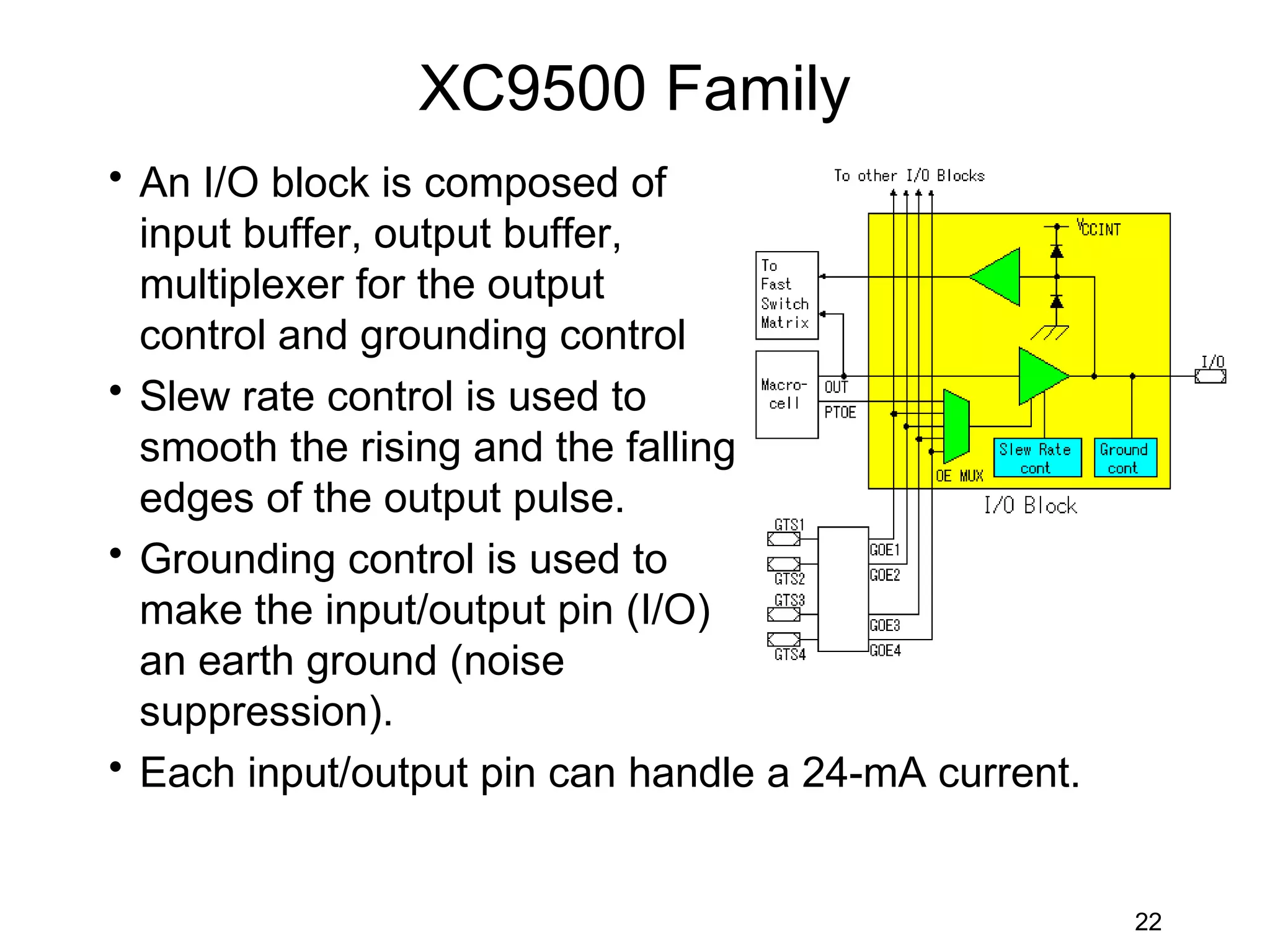

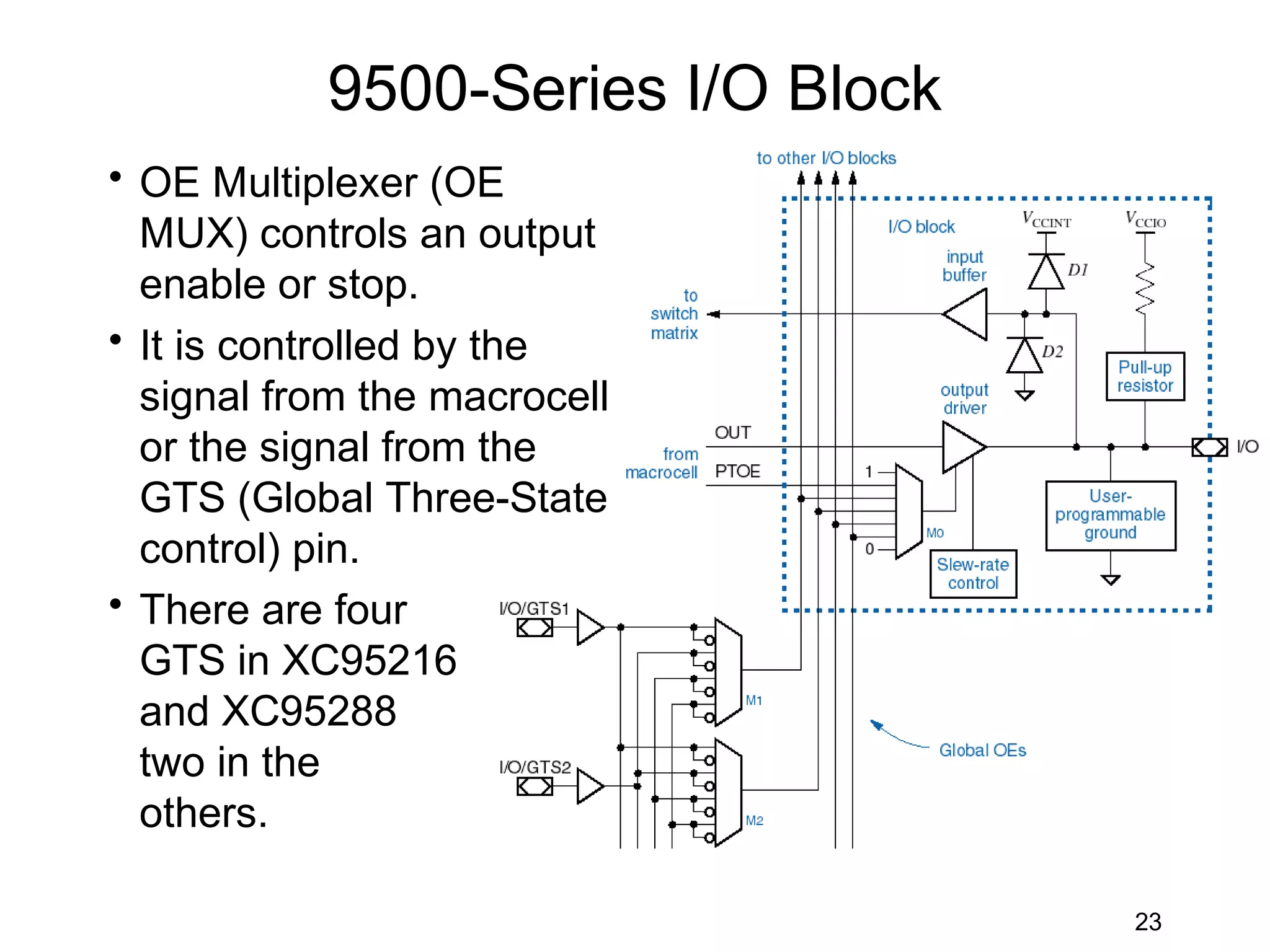

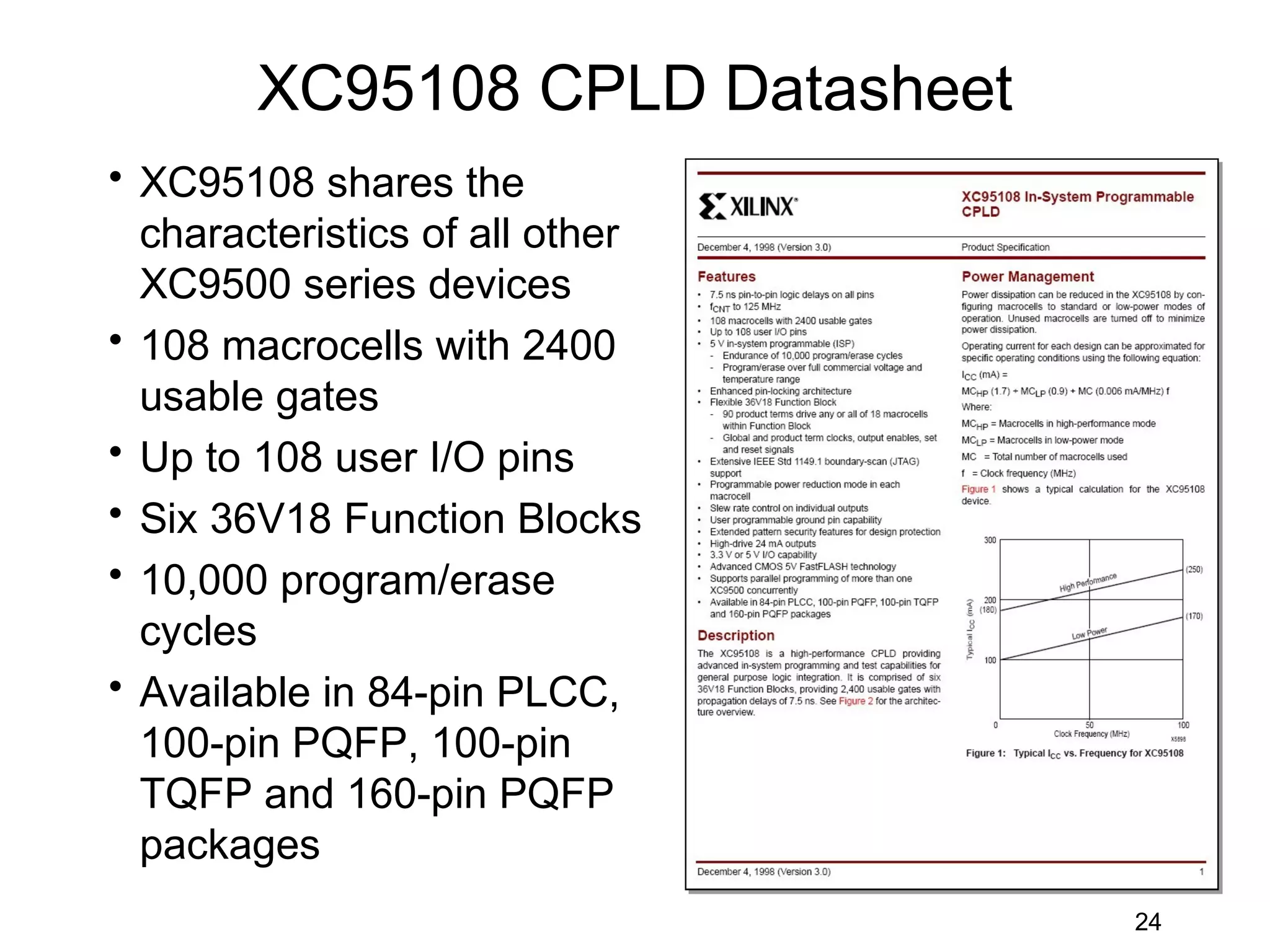

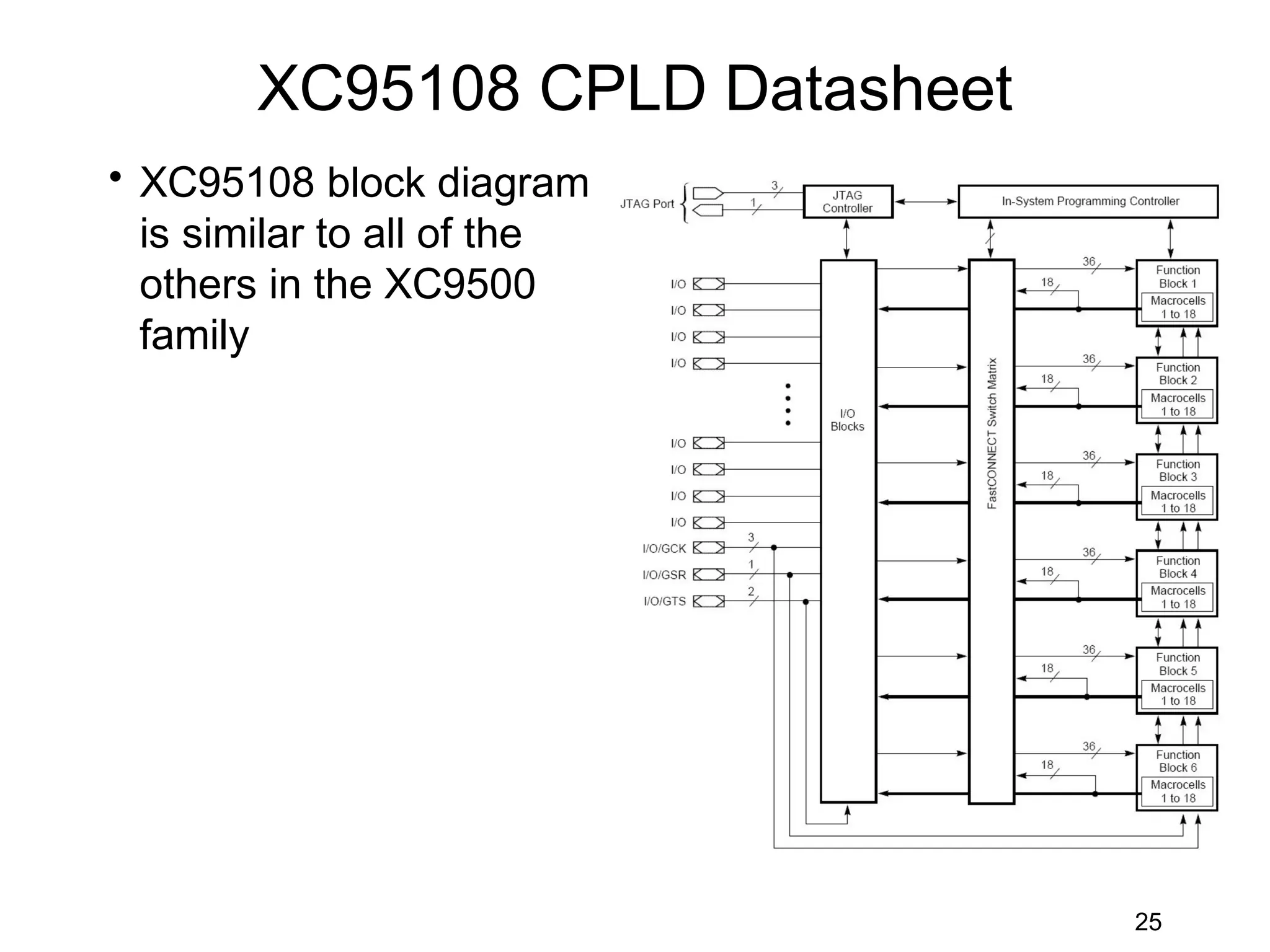

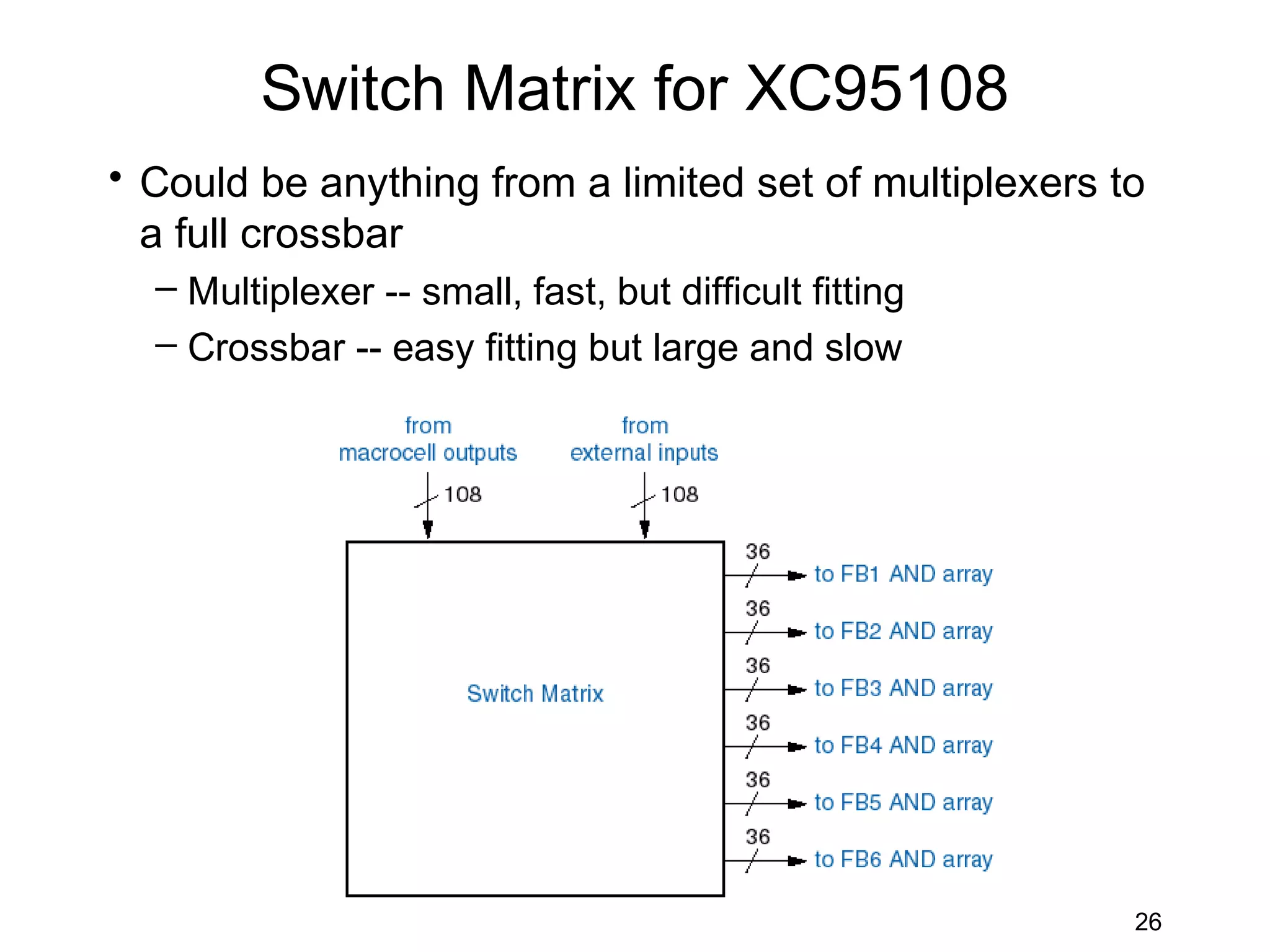

This document discusses CPLDs (Complex Programmable Logic Devices), including their general architecture, reprogrammability, density, and common vendors and families. CPLDs contain programmable macrocells (equivalent to around 20 gates each) connected by a programmable interconnect and support up to 200 I/O pins. They are between FPGAs and SPLDs in complexity. The document describes CPLD architecture including logic array blocks (LABs) and programmable interconnect arrays (PIAs). It provides examples of Xilinx CPLD families, packages, and a datasheet for the XC9572 device.