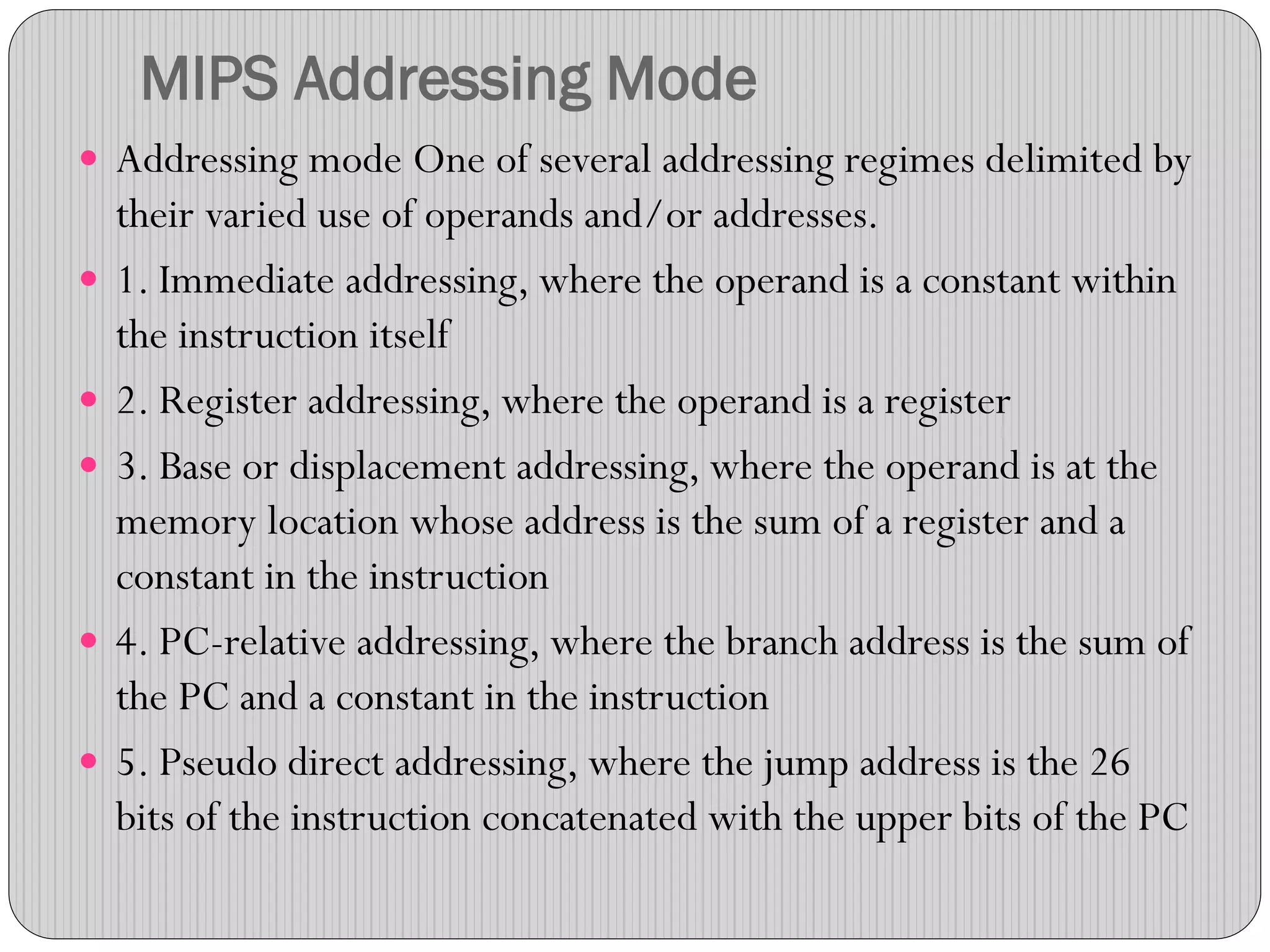

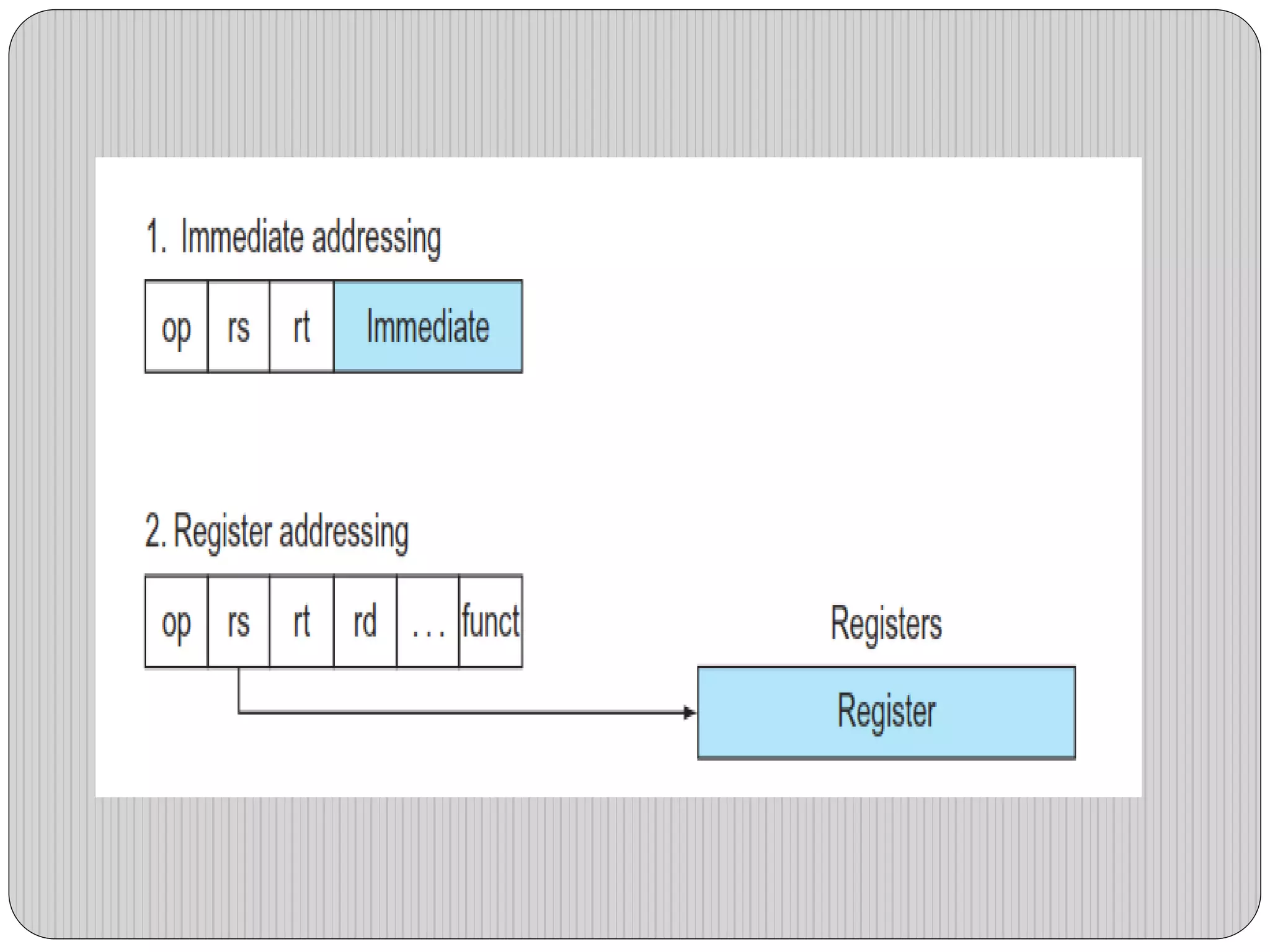

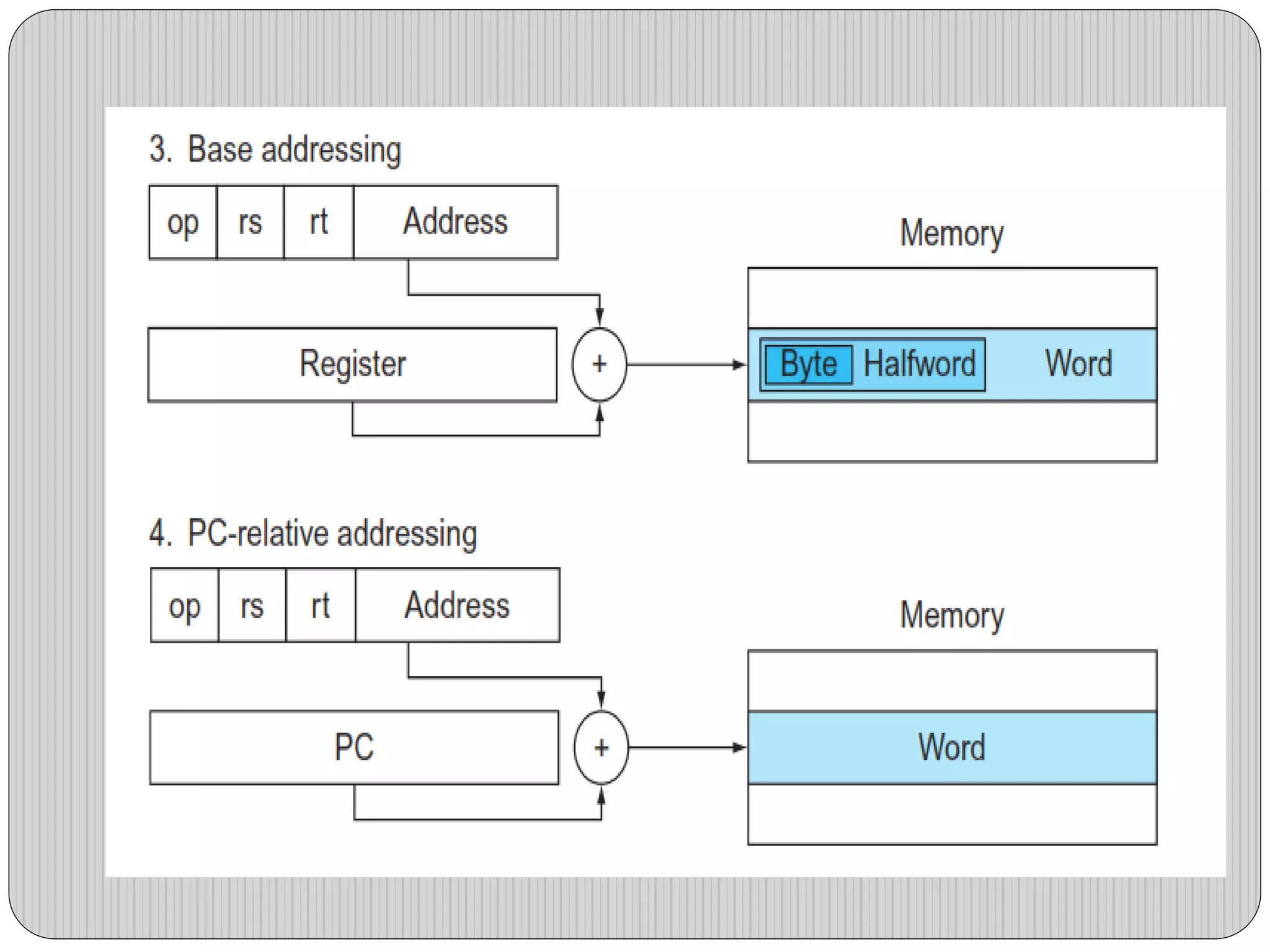

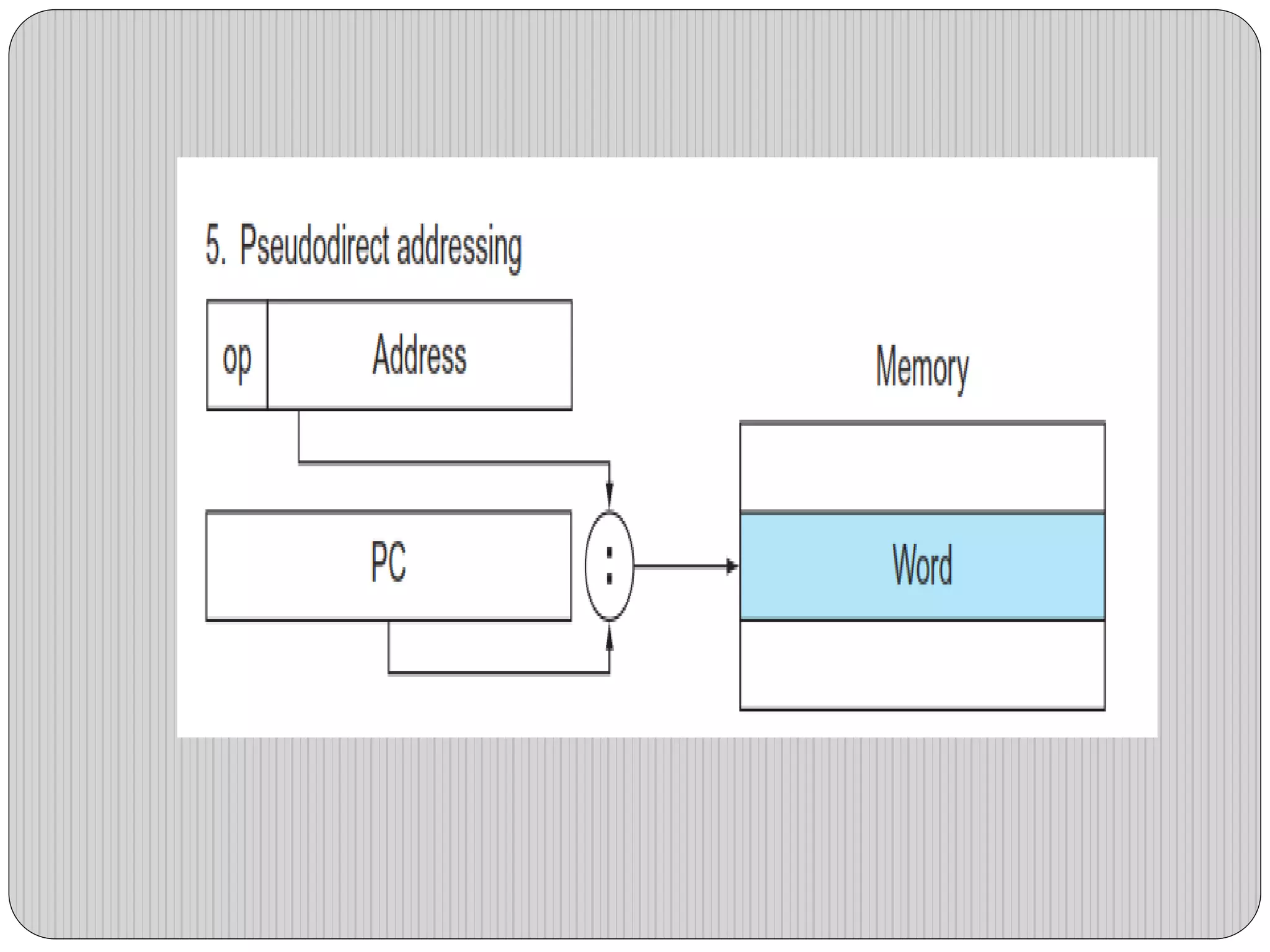

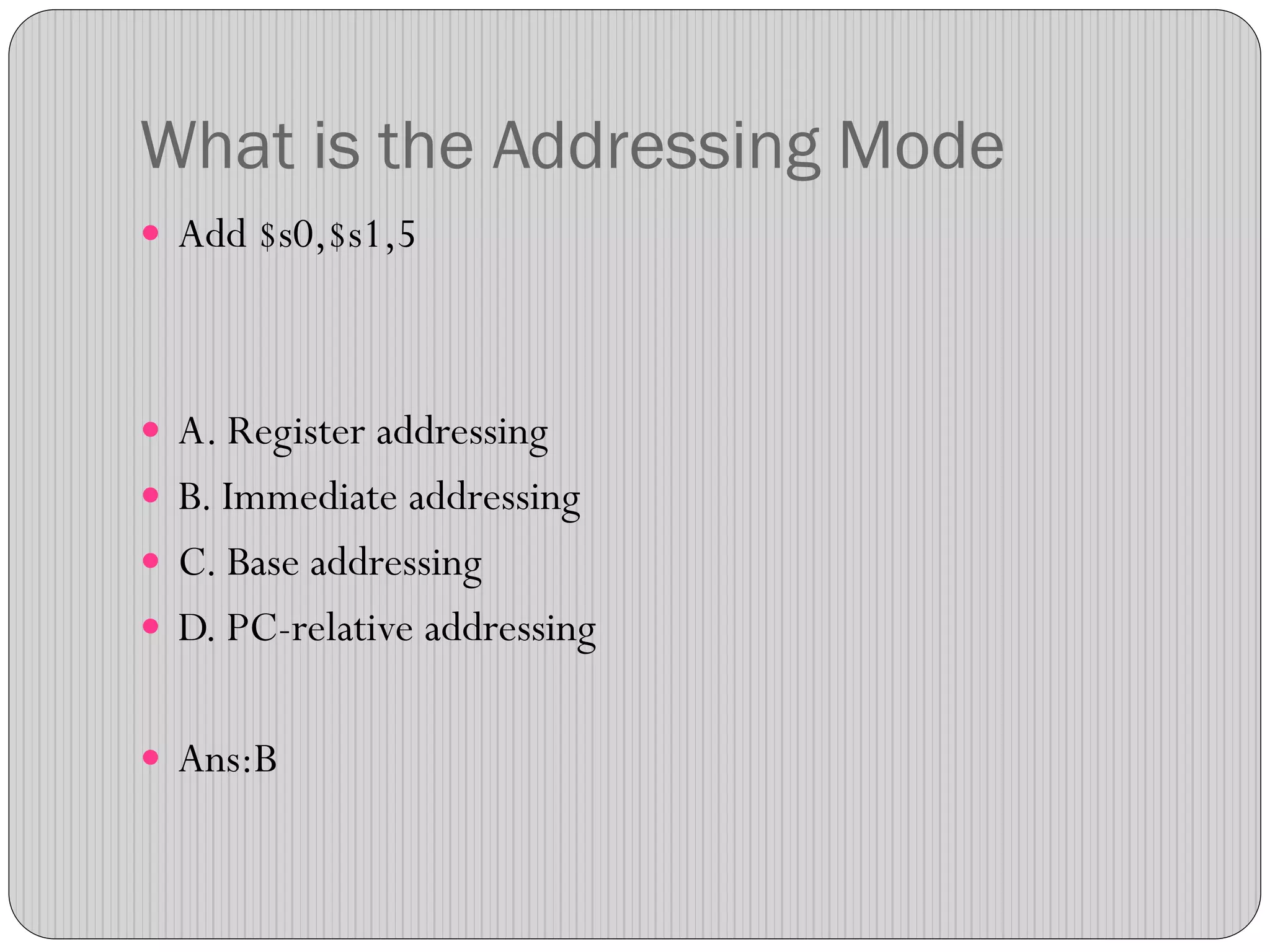

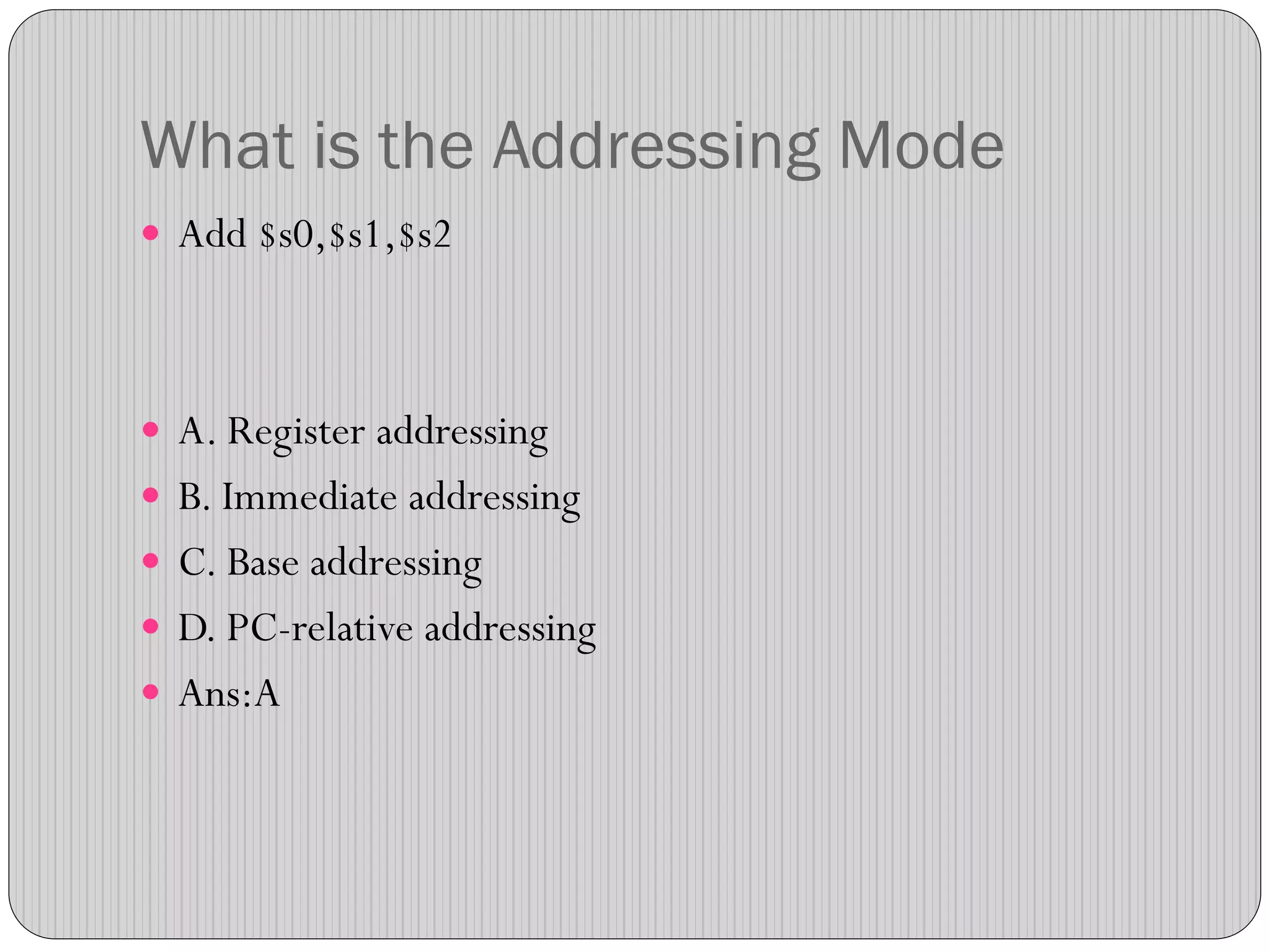

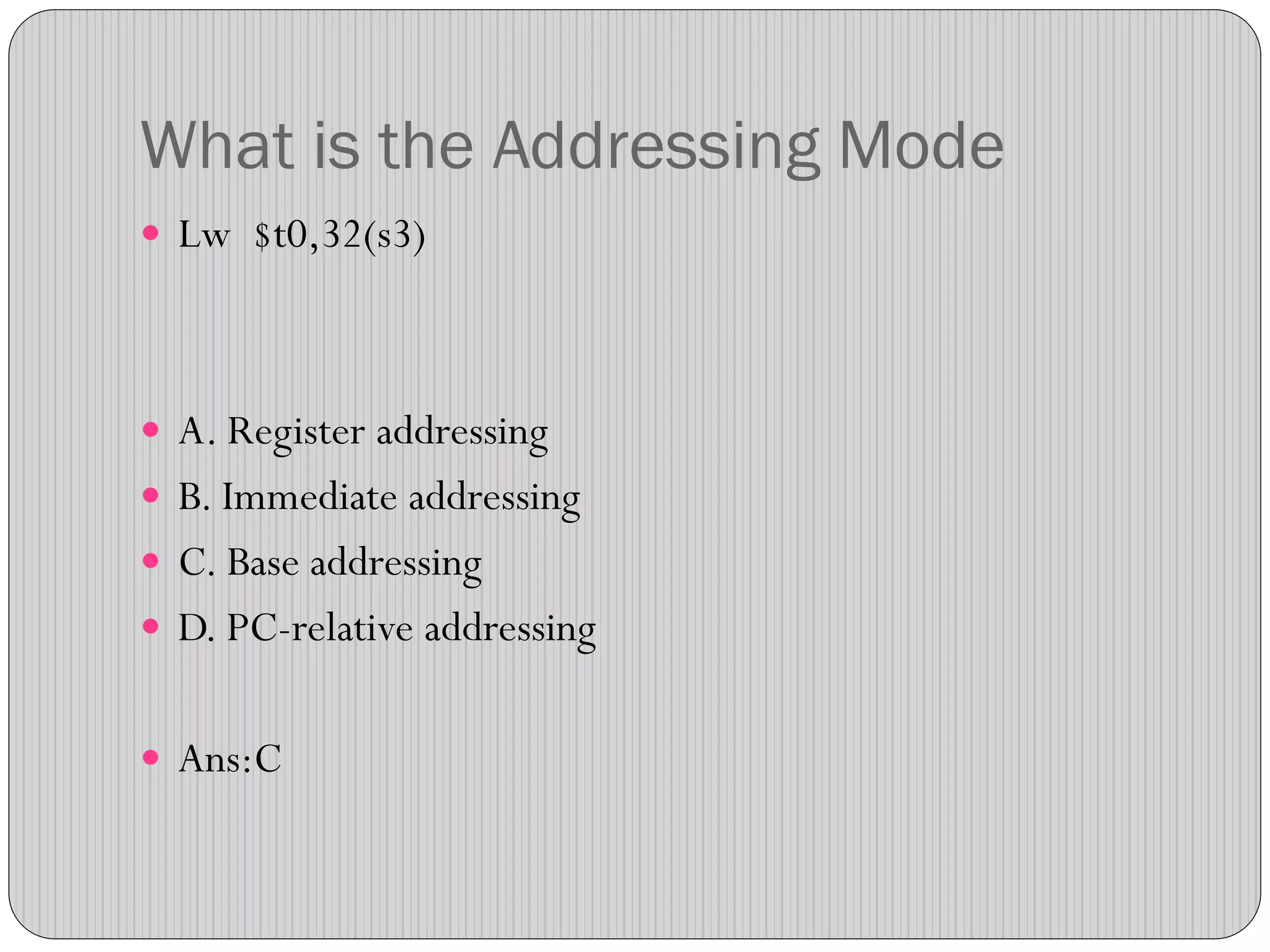

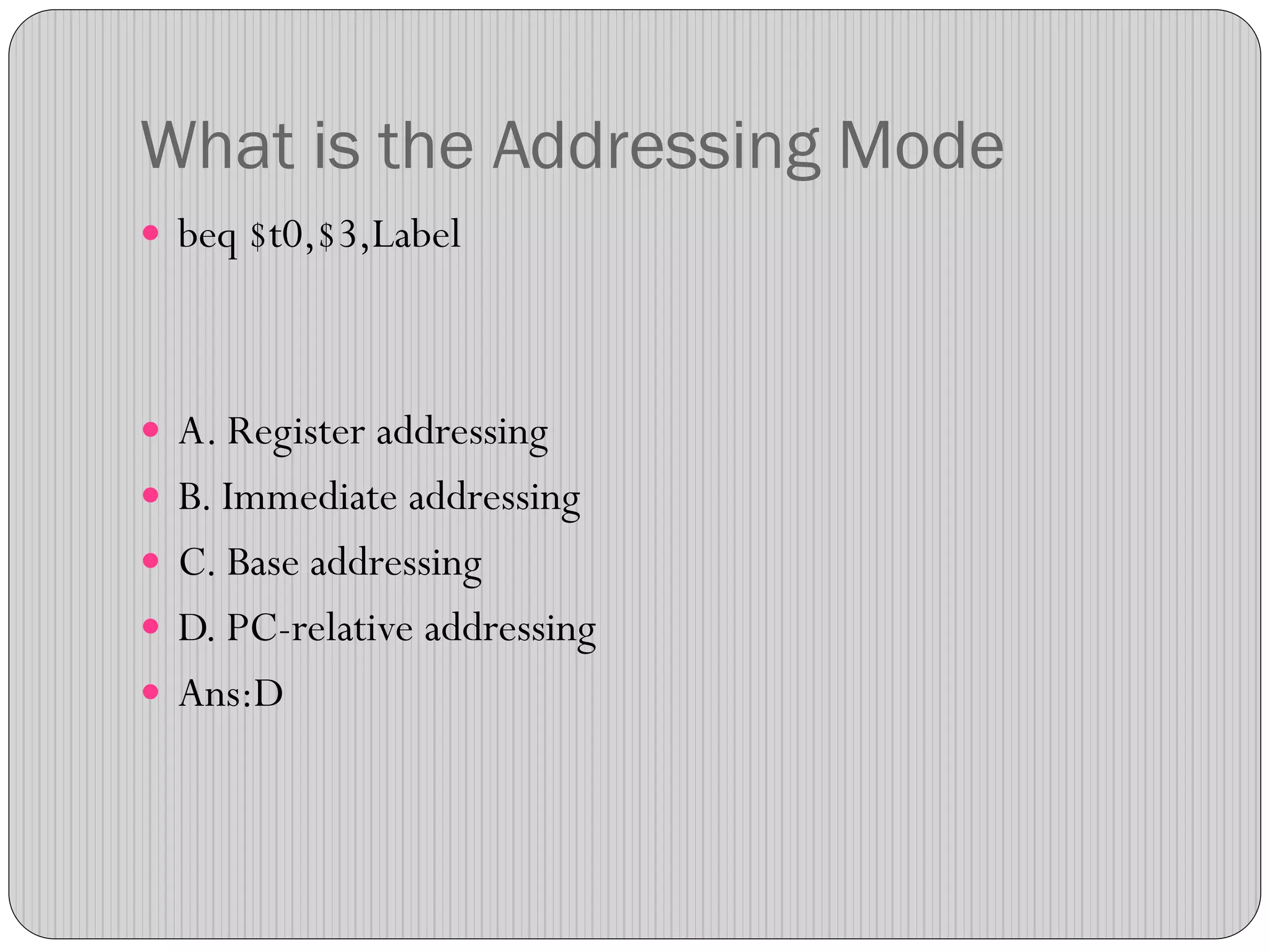

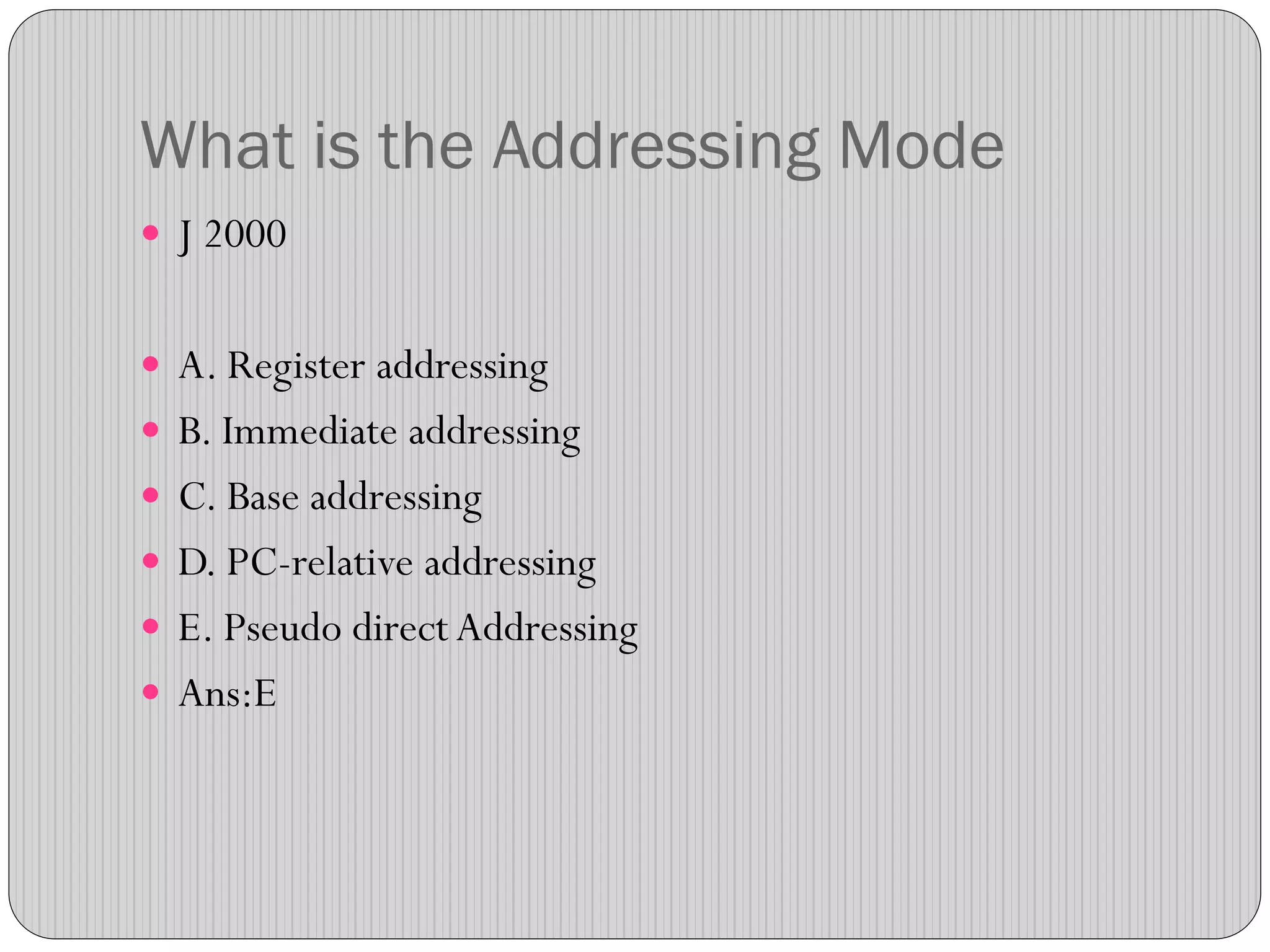

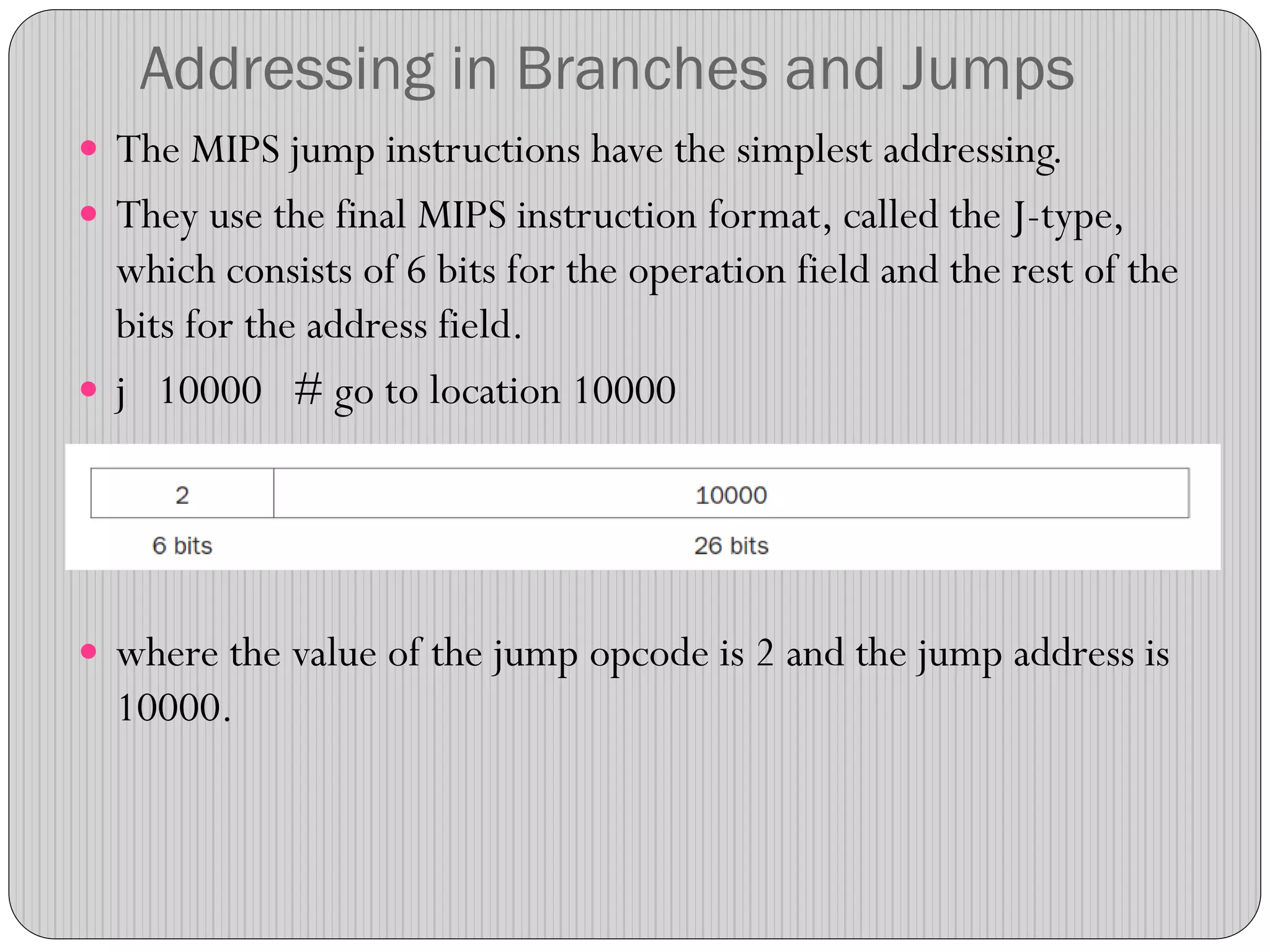

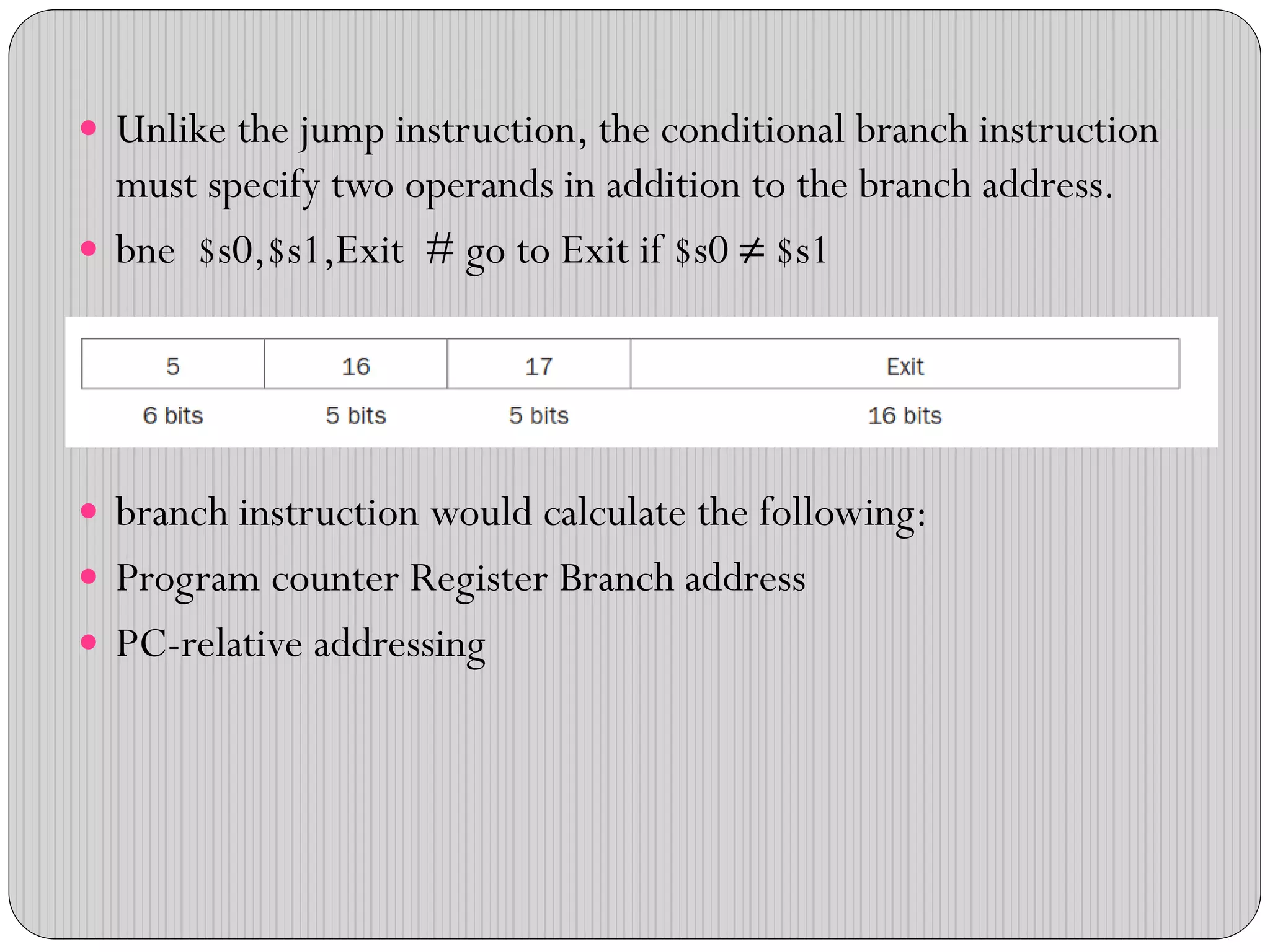

The document discusses different addressing modes in MIPS including immediate, register, base/displacement, PC-relative, and pseudo direct addressing. It provides examples of instructions that use each addressing mode and explains what they do. MIPS uses different instruction formats for jumps, branches, and other instructions. Branches require two operands and calculate the branch address relative to the program counter. Loops in MIPS code are also demonstrated with examples of how they would appear in assembly code.

![ Showing Branch Offset in Machine Language

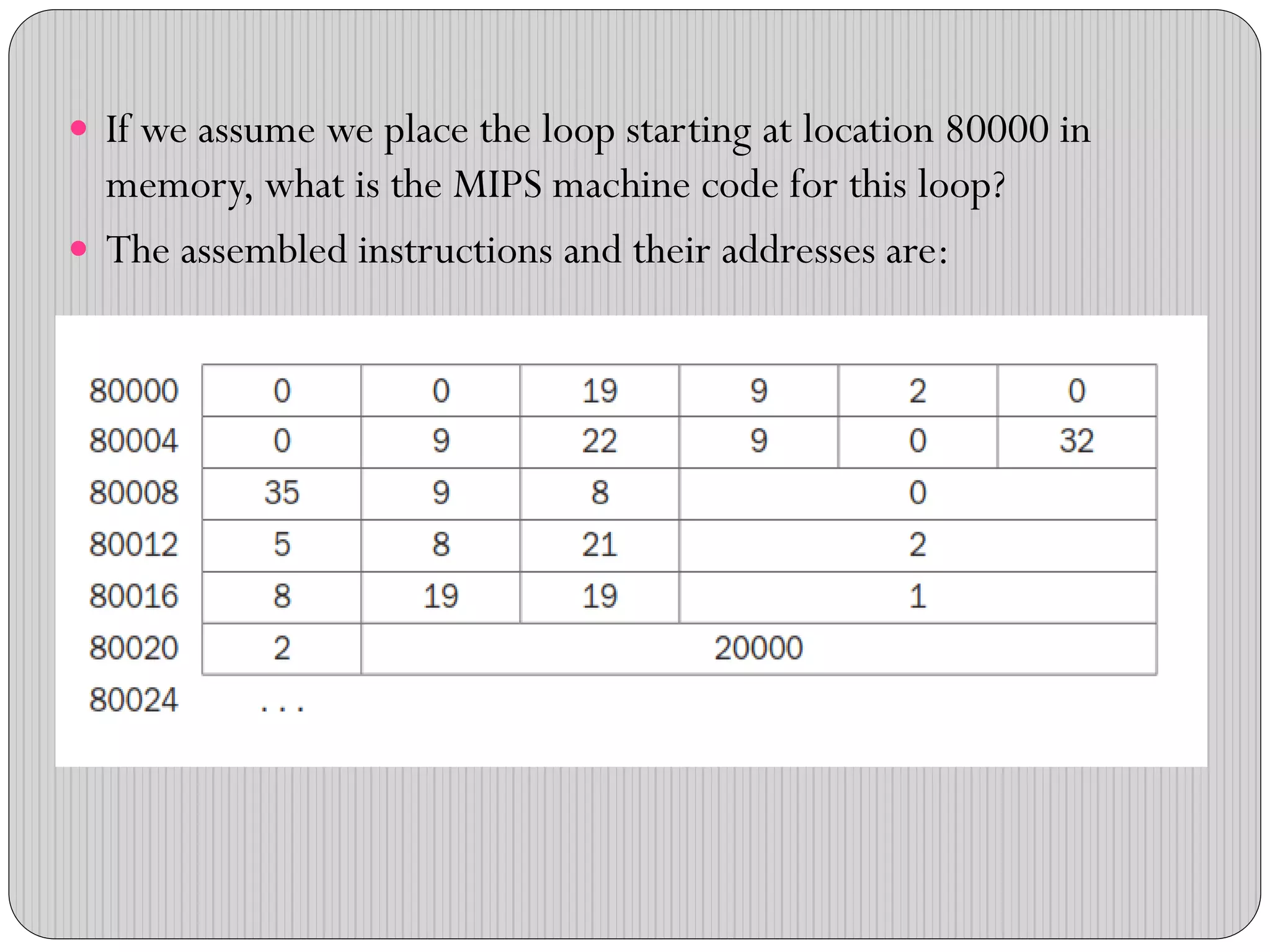

The while loop as compiled into this MIPS assembler code:

Loop:sll $t1,$s3,2 #Temp reg $t1 = 4 * i

add $t1,$t1,$s6 # $t1 = address of save[i]

lw $t0,0($t1) #Temp reg $t0 = save[i]

bne $t0,$s5, Exit # go to Exit if save[i] ≠ k

addi $s3,$s3,1 # i = i + 1

j Loop # go to Loop

Exit:](https://image.slidesharecdn.com/unit-ica-mipsaddressing-200228125915/75/Unit-i-ca-mips-addressing-4-2048.jpg)