The document discusses different types of addressing modes used in computer architecture. It describes 8 types of addressing modes: register, register indirect, immediate, direct, indirect, implicit, relative, and indexed. For each type, it provides an example instruction, brief explanation of how that addressing mode works, and diagram illustrating the addressing mode. It also discusses auto-increment and auto-decrement addressing modes.

![Addressing modes are nothing but the different ways in which the

location of an operand can be specified in an instruction. The number

of addressing modes that a processor supports changes according to

the instruction set it is based on, however there are a few generic ones

that are present in almost all processors and are thus of utmost

importance.

They are as follows:

• register (or register-direct) addressing: R1

• register indirect addressing: M[R1]

• immediate addressing: data

• direct (or absolute) addressing: M[address]

• indirect addressing: M[M[address]]

• implicit addressing: default location

• relative & indexed addressing: M[R1+address]

• pre-decrement, post-decrement, pre-increment, ...

(1)Register (or register-direct) Addressing:

In register mode ,a register contains the operand. The operand is

specified with in one of the processor register. Instruction specifies the

register in which the operand is stored. In register addressing the

operand is placed in one of 8 bit or 16 bit general purpose registers.The

data is in the register that is specifiedby the instruction. Here one register

reference is required to access the data.

Example: Move

MOV C , A C ← A ( Here A is the operand specified in register)

In register,

Add](https://image.slidesharecdn.com/assignmentondifferenttypesofaddressingmodes-200809090034/85/Assignment-on-different-types-of-addressing-modes-2-320.jpg)

![ADD B A ← A + B ( Here B is the operand specified in register)

In register,

Figure:

Figure: Register Addressing Diagram

(2)Register Indirect Addressing:

The instruction specifies the register in which the memory address of operand is

placed. Itdo not specify the operand itself but its location with in the memory

whereoperand is placed. In this addressing, theoperand offsetis placed in any

one of the registers BX,BP,SI,DI as specified in the instruction.

Example:

Move

MOV A , M A ← [[H][L]] Itmoves the data frommemory location specified

by HL register pair to A](https://image.slidesharecdn.com/assignmentondifferenttypesofaddressingmodes-200809090034/85/Assignment-on-different-types-of-addressing-modes-3-320.jpg)

![Figure:

Figure: Immediate Addressing Diagram

Example: MOV AL, 35H (move the data 35H into AL register)

(4)Direct (or absolute) addressing:

The instruction specifies the direct address of the operand.Thememory address

is specified wherethe actual operand is. The operand’s offset is given in the

instruction as an 8 bit or 16 bit displacement element. In this addressing mode the 16 bit

effective address of the data is the part of the instruction.Here only one memory

reference operation is required to access the data.

Example:

Load Accumulator

LDA 2805h A ← [2805] Itloads the data frommemory location 2805 to

A.

Store Accumulator STA

2803h [2803] ←A Itstores the data fromA to memory location 2803

Example: ADD AL,[0301] //add the contents of offset address 0301 to AL

Figure:](https://image.slidesharecdn.com/assignmentondifferenttypesofaddressingmodes-200809090034/85/Assignment-on-different-types-of-addressing-modes-5-320.jpg)

![Figure: Direct Addressing Diagram

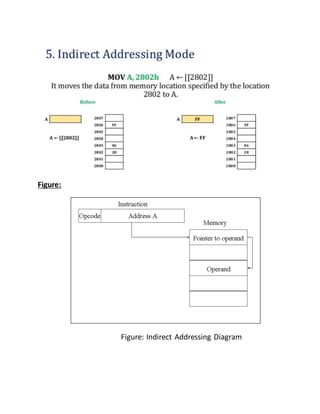

(5)Indirect Addressing:

The instruction specifies the indirect address where the effective

address of the operand is placed. The memory address is specified

where the actual address of operand is placed. The indirect addressing

mode uses a register to hold the actual address that will finally be used

in data moves ,the register itself is not the address, but rather the

number in the register.

Example:

Move

MOV A, 2802h A ← [[2802]]

It moves the data from memory location

specified by the location 2802 to A.](https://image.slidesharecdn.com/assignmentondifferenttypesofaddressingmodes-200809090034/85/Assignment-on-different-types-of-addressing-modes-6-320.jpg)